全志V系列芯片安全机制详解:确保设备安全运行的完整指南

发布时间: 2025-01-04 00:17:48 阅读量: 7 订阅数: 14

全志A20 芯片id 获取方法 。

# 摘要

全志V系列芯片作为高性能嵌入式处理器,在安全架构设计中注重性能与安全的平衡。本文介绍了全志V系列芯片的安全架构,包括硬件级别的加密引擎、安全引导和存储解决方案,以及软件级别的安全加固和沙箱技术。文章还探讨了安全漏洞的分析、防范措施以及修补策略,强调了加密技术在芯片安全中的核心作用,并提供了密钥管理的策略。此外,本文提出安全编程实践的重要性,并展望了人工智能与安全协议未来的发展方向。

# 关键字

全志V系列芯片;安全架构;加密技术;密钥管理;安全编程;人工智能安全;物联网安全协议

参考资源链接:[全志V536、V526专业相机SoC芯片手册](https://wenku.csdn.net/doc/334z5cnuhe?spm=1055.2635.3001.10343)

# 1. 全志V系列芯片概述

全志V系列芯片是全志科技推出的一系列高性能、低功耗的处理器产品,广泛应用于智能设备和边缘计算领域。这些芯片不仅提供了出色的计算性能,还集成了多种先进的功能和接口,以满足不同的应用需求。

## 芯片设计特点

全志V系列芯片采用了多核CPU设计,支持多线程任务处理,能够提供更高的运行效率和更好的用户体验。此外,芯片内置了高性能的图形处理单元(GPU),使得处理多媒体内容和图形界面更加流畅。

## 应用场景

在工业自动化、车载信息娱乐系统、智能家居、可穿戴设备等多个领域中,全志V系列芯片都有其独特的应用场景。其优异的性价比和稳定的性能表现,为开发者提供了丰富的选择空间。

```markdown

- 工业自动化:高可靠性与实时处理能力。

- 车载娱乐:良好的多媒体处理性能。

- 智能家居:低功耗与系统集成。

- 可穿戴设备:小巧尺寸与轻量级操作系统支持。

```

通过了解全志V系列芯片的设计特点和应用场景,我们可以更好地掌握其在不同领域中的优势和应用潜力。接下来的章节将进一步探讨这些芯片的安全架构和技术细节。

# 2. 全志V系列芯片的安全架构

## 2.1 安全架构设计原则

### 2.1.1 安全性与性能的平衡

在设计全志V系列芯片的安全架构时,首要考虑的是安全性与性能之间的平衡。在保证硬件平台高性能的前提下,如何整合安全机制,确保数据的机密性、完整性和可用性是设计过程中的关键。

全志V系列芯片采用的策略包括:

- **硬件安全加速器**: 引入专用硬件模块加速加密解密操作,减少对CPU的依赖,从而降低对整体性能的影响。

- **轻量级加密算法**: 选择那些在保证安全性的同时能够尽可能少消耗计算资源的加密算法。

- **硬件抽象层(HAL)**: 通过HAL,将安全功能与应用层隔离,降低应用层对安全功能的性能损耗。

- **多层次安全策略**: 在不同层面实现安全防护,如在硬件层面实现防篡改,在软件层面实现权限控制,以降低对单一层面安全措施的依赖。

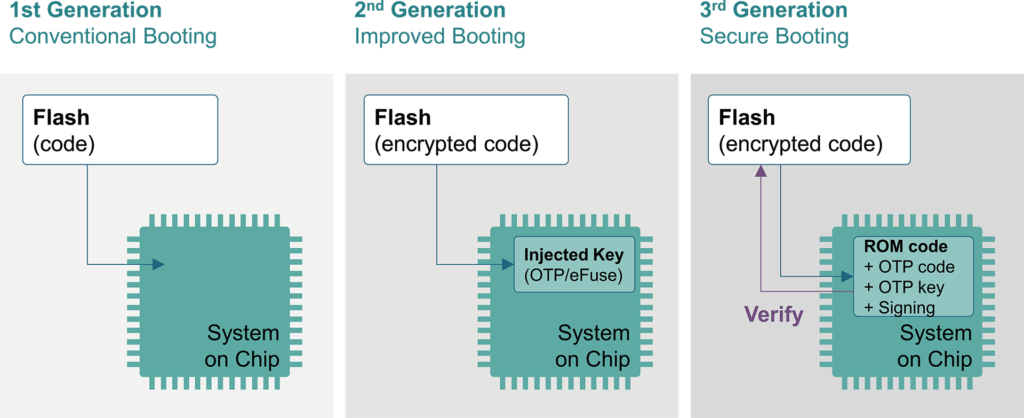

### 2.1.2 安全启动和可信执行环境

全志V系列芯片的设计强调从设备启动阶段即开始维护系统安全。安全启动确保设备只能加载并执行经过认证的代码,从而构建可信执行环境(TEE)。

- **安全引导流程**: 设备在启动时首先验证引导加载程序(Bootloader)的签名,保证后续加载的固件不被篡改。

- **可信执行环境(TEE)**: 在主处理器之外,设置一个专用区域用于处理高安全需求的任务,确保这些任务在隔离和安全的环境中运行,防止数据被窃取或非法访问。

## 2.2 硬件级别的安全特性

### 2.2.1 加密引擎和密钥管理

全志V系列芯片内置先进的加密引擎,为数据传输和存储提供了强大的安全保障。密钥管理是芯片安全的关键组成部分。

- **加密引擎**: 支持多种加密算法,如AES、DES、SHA等,可进行高速数据加密和解密。

- **安全密钥存储**: 提供专用的硬件安全模块(HSM)来存储敏感密钥,确保密钥在硬件级别的安全。

### 2.2.2 安全引导过程

全志V系列芯片的安全引导过程是基于可信计算组(Trusted Computing Group, TCG)提出的安全引导标准,确保设备的完整性和身份验证。

- **初始引导**: 系统在加电后首先执行内部只读存储器(ROM)中的引导代码,ROM代码包含了安全启动的必要逻辑。

- **引导链验证**: 每个阶段的引导程序都会验证下一个引导程序的签名,确保从固件到操作系统的连续性。

### 2.2.3 安全存储解决方案

为了确保用户数据安全,全志V系列芯片提供了安全存储解决方案。

- **数据加密**: 在存储到外部存储器之前,敏感数据会被自动加密。

- **隔离存储区域**: 为不同类型的数据设置不同的存储区域,包括系统数据和用户数据,确保数据隔离性和安全性。

## 2.3 软件级别的安全特性

### 2.3.1 操作系统安全加固

全志V系列芯片的软件安全加固措施针对操作系统层进行了优化,确保系统操作的可靠性和稳定性。

- **最小权限原则**: 默认情况下,应用程序和用户仅具备完成任务所需的最小权限,避免权限过度授权。

- **强制访问控制(MAC)**: 系统通过策略强制控制访问敏感资源,从而降低潜在的风险。

### 2.3.2 应用程序的安全沙箱

为了隔离应用程序,全志V系列芯片利用了安全沙箱技术。

- **运行时隔离**: 每个应用程序在沙箱中运行,其对系统资源的访问受到严格限制。

- **沙箱机制**: 沙箱通过一系列软件和硬件机制确保应用程序之间以及应用程序与系统之间的隔离。

### 2.3.3 运行时的安全防护机制

全志V系列芯片还集成了一系列的运行时安全防护机制,以识别和防御运行时的攻击。

- **异常检测**: 实时监测异常行为和潜在的安全威胁,一旦发现异常即触发告警。

- **入侵检测系统(IPS)**: 集成IPS用于实时检测和预防恶意入侵。

- **安全事件日志**: 记录和审计安全事件,用于事后分析和取证。

```mermaid

graph TD

A[系统加电] --> B[执行ROM引导代码]

B --> C{验证Bootloader签名}

C -->|成功| D[加载Bootloader]

C -->|失败| E[拒绝启动]

D --> F[验证内核签名]

F -->|成功| G[加载内核]

F -->|失败| H[拒绝启动]

G --> I[运行系统]

I --> J{运行时安全监控}

J -->|发现威胁| K[触发安全措施]

J -->|安全运行| L[继续监控]

K --> M[采取防御行动]

```

在上述流程图中,展示了全志V系列芯片从加电到启动过程的安全策略和运行时的防护机制。每个节点代表了芯片在不同阶段的安全检查点,确保了硬件和软件层面的安全性。

# 3. 全志V系列芯片的安全漏洞和防范措施

0

0