全志V系列芯片故障诊断与维修:解决常见问题的速成课程

发布时间: 2025-01-04 00:56:05 阅读量: 5 订阅数: 14

jQuery速成课程:Traversy Media jQuery速成课程的经验教训

# 摘要

全志V系列芯片作为重要的嵌入式系统解决方案,广泛应用于各类智能设备中。本文首先介绍了全志V系列芯片的硬件结构,包括核心处理器架构、存储管理及电源管理机制。随后,文章深入探讨了芯片的故障诊断基础,从硬件和软件故障的诊断流程、常见问题分析到解决方案的提供。在此基础上,本文进一步探讨了维修实践,包括维修工具与设备介绍、具体案例分析和预防措施的建议。最后,文章对故障诊断的高级应用进行了展望,包括远程诊断技术、基于机器学习的故障预测模型、高性能计算环境下的诊断方法以及自动化维修流程的构建。本文为全志V系列芯片的维修和故障处理提供了系统而全面的参考和指导。

# 关键字

全志V系列芯片;硬件结构;故障诊断;维修实践;远程诊断技术;自动化维修流程

参考资源链接:[全志V536、V526专业相机SoC芯片手册](https://wenku.csdn.net/doc/334z5cnuhe?spm=1055.2635.3001.10343)

# 1. 全志V系列芯片概述

全志V系列芯片是全志科技推出的一系列高性能多媒体处理器,广泛应用于平板电脑、智能电视盒、教育机器人等多种设备中。这些芯片以其高集成度、低功耗和卓越的多媒体处理能力在业界享有盛誉。

## 芯片的市场定位与应用领域

全志V系列芯片凭借其出色的性价比,在众多中低端市场领域取得了显著优势,成为了教育、家庭娱乐和个人便携式设备的首选解决方案。其灵活的设计允许制造商快速集成到不同产品中,实现产品差异化。

## 核心技术特点

全志V系列芯片的核心技术特点包括ARM架构的高效处理能力、先进的视频解码技术以及对多种操作系统和应用程序的良好支持。这些技术特点赋予了全志V系列芯片在市场上的竞争力,使其能够在激烈的市场竞争中保持一定的领先优势。

# 2. 全志V系列芯片的硬件结构解析

## 2.1 核心处理器架构

### 2.1.1 CPU核心与缓存设计

全志V系列芯片的CPU核心采用了多核架构设计,通常包含了多个高性能的处理器核心,这些核心可以是同构的也可以是异构的。同构多核指的是所有核心的架构和功能完全一样,而异构多核则意味着核心之间在处理能力或功能上存在差异,这样的设计可以针对不同任务提供更加优化的计算资源分配。

缓存设计是CPU性能的重要组成部分,通常包括一级缓存(L1 Cache)、二级缓存(L2 Cache)等。L1缓存一般分为数据缓存和指令缓存,它们都具有非常低的访问延迟,但容量相对较小。L2缓存容量更大,作为L1缓存的补充,可以缓存更多的数据和指令,减少对主内存的访问次数,提高处理器性能。

在设计中,L1和L2缓存通常被集成到CPU核心中,以便于快速访问。L3缓存通常作为共享缓存,放置在核心群组之间,以进一步提高多核之间的数据共享效率。

### 2.1.2 多核协同工作原理

多核处理器的核心之间通过内部的高速互连网络进行通信,以实现高效的协同工作。当一个核心需要访问另一个核心的缓存数据时,这个请求会通过该网络传输给对应的核心,如果数据不在目标核心的缓存中,那么数据会从共享的L3缓存或者主内存中加载到目标核心的缓存中。

多核协同工作还包括任务调度和负载均衡机制。在操作系统层面上,通常会有调度器来决定每个核心应该执行哪个任务。调度算法可以是简单的轮转调度,也可以是更加复杂的基于任务优先级和执行时间的调度,以确保任务可以在各核心间有效地分配和执行。

多核架构的关键之一在于高速缓存一致性协议,如MESI(修改、独占、共享、无效)协议,保证了所有核心看到的缓存数据是一致的。当一个核心修改了其缓存中的数据时,它需要通知其他核心,这样其他核心缓存中的相同数据将被标记为过时或失效,确保整个系统的数据一致性。

## 2.2 存储管理与接口技术

### 2.2.1 内存管理单元(MMU)

内存管理单元(MMU)是现代处理器中的一个重要组成部分,负责虚拟内存地址到物理内存地址的转换。MMU使用页表来映射虚拟地址空间到物理内存,同时MMU也提供了内存保护机制,通过定义页表项中的权限位来控制对特定内存区域的访问。

MMU支持的特性包括:

- **地址转换**:实现虚拟地址到物理地址的转换。

- **内存保护**:通过权限检查,防止程序之间的非法访问。

- **分页机制**:支持将连续的虚拟地址空间分割成固定大小的页,并映射到物理内存的分页。

在全志V系列芯片中,MMU的设计和实现对于系统性能至关重要。有效的内存管理不仅可以提高程序的执行效率,还可以通过内存保护机制提高系统的安全性。

### 2.2.2 常见的输入输出接口技术

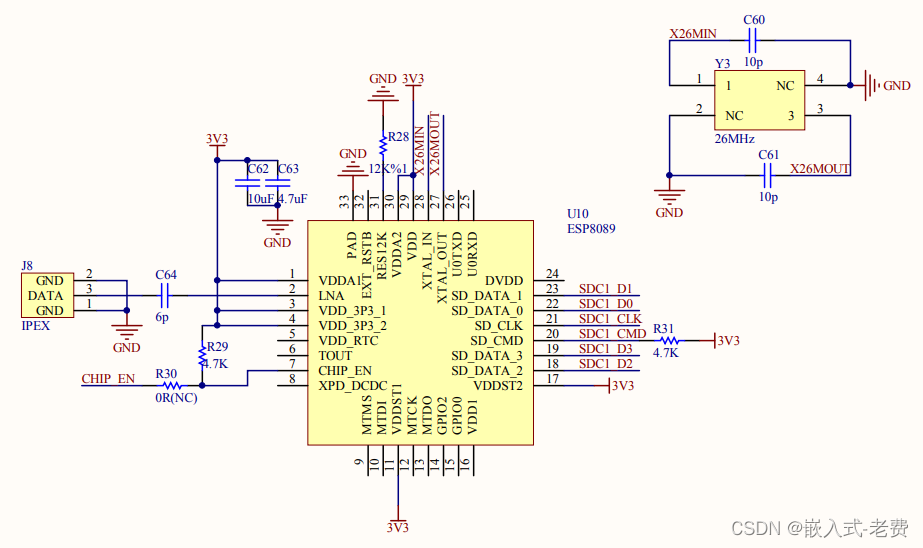

全志V系列芯片支持多种输入输出接口技术,以便于与外部设备进行数据交换。这些接口包括USB、HDMI、SD卡接口、以太网接口、Wi-Fi模块等。

USB接口用于连接各种外部设备,如键盘、鼠标、U盘等。HDMI接口则用于显示输出,支持高清视频和音频的传输。SD卡接口通常用于存储扩展,可以实现大容量数据的存储和读取。以太网和Wi-Fi模块则为设备提供了网络连接功能,使设备可以接入互联网。

这些接口技术在硬件层面通常依赖于特定的控制器芯片,并通过特定的总线如PCIe或I2C等与CPU核心进行通信。设计者需要考虑接口的兼容性、传输速率、以及功耗等因素,以满足不同应用场景的需求。

## 2.3 电源管理机制

### 2.3.1 电源域划分与管理

全志V系列芯片的电源管理设计采用了电源域划分技术,将芯片内不同部分的电源独立管理,以达到降低功耗的目的。通过划分不同的电源域,可以根据需要独立开启或关闭某部分电路,如CPU核心、GPU、内存和其他外设等。

电源管理单元(PMU)负责监控各个电源域的电压和电流,确保系统稳定运行。在全志V系列芯片中,PMU还支持动态电源管理策略,如在系统负载较轻时降低某些电源域的电压,或在高负载时提升电压以保证性能。

电源域划分和管理对延长设备的电池寿命至关重要,尤其是在移动设备和便携式设备中。合理的电源管理可以实现能耗的最优化,既保证了性能需求,又减少了能源消耗。

### 2.3.2 动态电压与频率调节(DVFS)

动态电压与频率调节(DVFS)是全志V系列芯片中用于进一步优化功耗的一种电源管理技术。DVFS的核心思想是根据处理任务的实时需求动态调整CPU的电压和频率。

当设备负载较低时,DVFS可以降低CPU的电压和频率,以减少功耗;而在负载较高时,则提高电压和频率,以满足性能要求。这种动态调节可以在不牺牲性能的前提下,有效降低功耗。

DVFS技术通常依赖于一个预先定义好的电压与频率映射表,这个映射表定义了不同性能需求下的最佳电压与频率设置。芯片根据当前的计算负载情况选择最合适的设置。

DVFS的应用不仅需要硬件支持,也需要软件层面上的配合。操作系统中的调度器需要能够准确评估和预测系统负载,然后通知DVFS模块进行相应的调整。因此,DVFS技术的实现涉及到软硬件协同工作的复杂过程。

DVFS的应用可以在多大程度上降低功耗,这依赖于应用的负载变化特性以及DVFS算法的效率。对于那些负载波动较大的应用场景,DVFS可以带来显著的节能效果。而在负载相对恒定的应用场景中,DVFS的节能效果可能相对有限。

# 3. 全志V系列芯片故障诊断基础

## 3.1 故障诊断流程概述

故障诊断是确保芯片稳定运行的关键步骤,可以尽早发现潜在问题,及时采取措施进行修复。诊断流程是系统性的,旨在提高排查问题的效率和准确性。本节将详细介绍全志V系列芯片的故障诊断流程。

### 3.1.1 硬件检测基本步骤

硬件检测通常包括以下几个基本步骤:

1. **视觉检查**:对全志V系列芯片进行外观检查,检查焊点、连接器、线路板等是否有明显的损坏或短路痕迹。

2. **电源测试**:使用万用表检测电源电压是否符合芯片规格,测量电流消耗,观察电源转换效率。

3. **信号测试**:通过示波器等工具,检查关键信号线路上的波形,确保没有信号衰减或失真问题。

4. **温度测试**:使用红外热像仪检测芯片在不同工作状态下的温度变化,判断散热系统是否正常。

通过这些基础步骤,可以初步判断出芯片是否存在问题,为进一步的详细诊断提供方向。

### 3.1.2 软件调试环境的搭建

软件调试是故障诊断中的重要环节,涉及到软件工具的使用和调试环境的搭建。全志V系列芯片的软件调试环境搭建步骤如下:

1. **下载并安装

0

0