【性能与灵活性平衡术】:7系列FPGA的SelectIO动态配置技巧

发布时间: 2024-12-27 10:30:13 阅读量: 13 订阅数: 11

ug471_7Series_SelectIO_fpga_selectIO_ug471_

# 摘要

本文深入探讨了7系列FPGA中SelectIO技术的理论与实践,以及如何在性能与灵活性之间实现平衡。首先,概述了SelectIO的基本概念和重要作用。随后,详细介绍了SelectIO的工作原理,包括输入输出缓冲器结构、信号完整性与传输线理论,以及电气标准和时序参数设置。接着,本文转入实践部分,分析了动态配置的关键技术,并提供了配置实例的分析。性能优化和灵活性实现的方法也在文中得到了阐述,并通过案例研究展示了平衡二者的方法。最后,文章展望了FPGA技术与SelectIO的未来趋势,探讨了潜在的挑战与机遇。

# 关键字

FPGA;SelectIO;信号完整性;动态配置;性能优化;灵活性实现

参考资源链接:[7系列FPGA SelectIO资源用户指南(UG471 v1.10)](https://wenku.csdn.net/doc/5g44bnz1fe?spm=1055.2635.3001.10343)

# 1. 7系列FPGA与SelectIO概述

FPGA(现场可编程门阵列)技术已经成为现代电子设计中不可或缺的组件,特别是7系列FPGA如Xilinx 7系列,其凭借高性能、高灵活性和成本效益而广泛应用于各个行业。为了充分利用这些FPGA的潜力,开发者需要深入理解其I/O结构和接口能力,也就是所谓的SelectIO技术。

SelectIO技术提供了一套完备的接口解决方案,允许用户根据特定应用需求配置FPGA的I/O引脚。本章将带您概览7系列FPGA的I/O结构,并介绍SelectIO的基础概念和应用。

- **7系列FPGA**: 以Xilinx 7系列为例,这些FPGA提供了丰富的I/O资源,支持从低功耗到高性能的各种应用需求。

- **SelectIO**: 是一种I/O架构,它为FPGA引脚提供了高度灵活的配置选项,能够支持不同的电气标准,如LVCMOS、HSTL、SSTL等。

接下来的章节将探讨SelectIO的基础理论,深入分析其工作原理和配置方法,以帮助您更好地设计出高性能、高灵活性的FPGA系统。

# 2. SelectIO的基础理论

## 2.1 SelectIO的工作原理

### 2.1.1 输入输出缓冲器结构

在深入探讨SelectIO的工作原理之前,需要先了解其核心组成部分——输入输出缓冲器结构。SelectIO通过这些缓冲器能够实现高速信号的输入与输出,以及信号的缓冲和驱动功能。每一块FPGA芯片中的SelectIO都由一组输入缓冲器和一组输出缓冲器组成,这些缓冲器采用高级半导体技术构建,以适应不同的电气标准和信号要求。

输入缓冲器设计用以接收外部信号,它们通常采用低噪声设计以确保信号的清晰度,同时它们可以对信号进行必要的调整和增强以适应芯片内部电路的要求。输出缓冲器则负责将内部信号转换为适合外部电路的标准电平,并驱动外部电路工作。

```mermaid

graph LR

A[输入信号] -->|缓冲增强| B[输入缓冲器]

C[输出缓冲器] -->|转换驱动| D[外部电路]

```

缓冲器的设计不仅关乎于电气特性,还涉及到物理特性和可靠性。因此,设计师会根据不同的应用场合选择合适的缓冲器类型,比如CMOS、HSTL、SSTL等,以满足不同的电气标准需求。

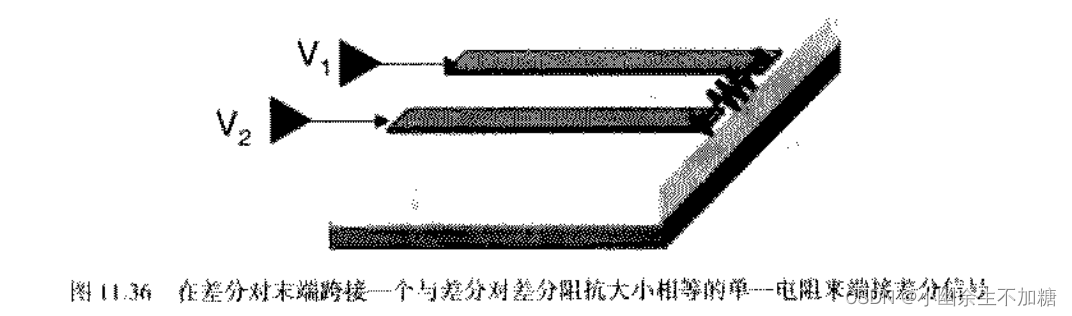

### 2.1.2 信号完整性与传输线理论

信号完整性是FPGA设计中一个非常重要的概念,它关注的是信号在传输路径中的质量和保持原有信息的能力。当信号在传输介质中传播时,会受到电感、电容、电阻等物理特性的限制,这些限制可能影响信号的波形,导致信号失真或延迟。因此,了解并应用传输线理论对于确保信号完整性至关重要。

传输线理论中,阻抗匹配是维持信号完整性的一个关键因素。当信号的源阻抗和负载阻抗匹配时,可以减少信号反射,保证信号质量。此外,传输线的长度、材料、物理布局等也都会影响信号的完整性,尤其是在高频信号传输时这些因素更是不容忽视。

```mermaid

graph LR

A[源] -->|传输线| B[负载]

B -->|反射| A

```

为了确保信号完整性,FPGA设计工程师会在布线设计时考虑传输线的特性阻抗,并确保它与输入输出缓冲器的阻抗一致。同时,通过添加适当的终端电阻来匹配源阻抗和负载阻抗,也可以有效地控制信号反射。在实际应用中,工程师们还必须考虑到信号的串扰、时序和噪音等其他因素,并通过一系列的分析和测试来优化设计。

## 2.2 SelectIO的电气标准和参数

### 2.2.1 不同I/O标准的对比

SelectIO能够支持多种电气接口标准,每种标准都有其特定的电气特性、数据传输速率和应用场合。理解这些标准之间的差异,对于设计满足特定需求的系统至关重要。常见的标准包括LVTTL、LVCMOS、LVDS、HSTL、SSTL等,每种标准都有其明确的电压和电流参数定义。

例如,LVTTL是一种标准的TTL逻辑电平,使用3.3V作为逻辑高电平,逻辑低电平为0V。而LVCMOS(低电压CMOS)则可能使用1.8V、2.5V或3.3V等不同的电源电压。相比之下,HSTL(High-Speed Transceiver Logic)和SSTL(Stub Series Terminated Logic)是专门为了高速内存接口设计的,它们提供了更低的信号摆幅和更严格的时序要求。

| 标准 | 逻辑高电压 | 逻辑低电压 |

| --- | --- | --- |

| LVTTL | 3.3V | 0V |

| LVCMOS | 1.8V/2.5V/3.3V | 0V |

| LVDS | 1.2V | 1.2V |

| HSTL | 1.5V | 1.5V |

| SSTL | 1.25V | 1.25V |

不同的I/O标准需要不同的驱动能力和阻抗匹配,这在设计时必须考虑。例如,LVDS具有较低的电压摆幅和较宽的频率范围,通常用于高速串行数据传输,而HSTL和SSTL由于其高速性能和低电压摆幅特性,经常被应用于高密度内存接口中。

### 2.2.2 时序参数的设置与考量

时序参数对于FPGA设计来说是至关重要的,它们包括但不限于数据有效窗口、建立时间和保持时间。这些参数定义了数据在不同逻辑元件之间传输时的时序要求,确保数据能够在正确的时刻被采样和传输。

数据有效窗口(setup/hold window)是指数据被采样之前和之后的稳定时间范围。在数据传输过程中,需要保证数据在这个窗口内保持稳定状态,否则可能会出现数据读取错误。建立时间(setup time)是指数据在时钟信号边沿到来之前必须稳定的时间;保持时间(hold time)则是指数据在时钟信号边沿过后必须保持稳定的时间。如果建立或保持时间不足,都可能导致数据读取失败。

```mermaid

graph LR

A[时钟边沿] -->|建立时间| B[数据稳定]

B -->|数据有效窗口| C[保持时间]

C -->|数据稳定| D[下一个时钟边沿]

```

在SelectIO的配置中,工程师需要根据系统的要求对时序参数进行仔细的设定。这通常涉及到时钟域的交叉处理、延迟匹配、以及时钟树的布局与布线。SelectIO通过提供精细的时序调整机制,允许工程师对输入和输出的时钟进行微调,从而实现更严格的数据同步。

此外,

0

0