【7系列FPGA I_O布局优化】:SelectIO资源的高级规划指南

发布时间: 2024-12-27 09:47:45 阅读量: 22 订阅数: 11

# 摘要

本文旨在详细探讨FPGA I/O资源的布局优化策略,重点介绍了SelectIO技术的理论基础及其在FPGA中的应用。通过分析SelectIO的架构、配置参数和性能特点,本文阐述了如何通过合理的I/O资源分配、高速信号布局技巧和仿真验证来实现有效的布局优化。文章还提供了具体的实践案例,探讨了在实际项目中应用这些优化策略的实际效果,并对未来FPGA I/O布局优化的发展趋势与挑战进行了预测和讨论。本文的研究为提高FPGA系统性能和功耗管理提供了理论和实践的指导。

# 关键字

FPGA;SelectIO技术;I/O布局优化;信号完整性;热管理;AI优化

参考资源链接:[7系列FPGA SelectIO资源用户指南(UG471 v1.10)](https://wenku.csdn.net/doc/5g44bnz1fe?spm=1055.2635.3001.10343)

# 1. FPGA I/O资源与布局优化概述

在现代电子设计中,FPGA(现场可编程门阵列)凭借其灵活性、可编程性和高性能成为众多系统中的关键组件。本章将概述FPGA I/O资源的重要性,以及如何通过优化布局来实现最佳性能。

## 1.1 I/O资源的角色

FPGA的I/O资源是连接FPGA内部逻辑与外部世界的桥梁。它们负责信号的输入输出,对于整个系统的性能、速度和可靠性有着决定性的影响。因此,合理利用并优化I/O资源至关重要。

## 1.2 布局优化的目标

布局优化旨在通过合理规划I/O资源的分配、信号路径和接口设计,提升系统的整体效率。这包括减少信号延时、降低电磁干扰、改善信号完整性、并优化热分布和功耗。

## 1.3 布局优化的挑战

随着技术的发展,FPGA的I/O速度越来越快,同时要求支持更高的数据吞吐量和更复杂的协议。这些都给布局优化带来了新的挑战,包括高速信号处理、时序约束和信号完整性分析等问题。

我们将通过后续章节深入探讨如何应对这些挑战,以期达到最优的FPGA I/O布局优化效果。

# 2. SelectIO技术理论基础

SelectIO技术是FPGA I/O布局优化的基石,涵盖了信号路径、驱动接收器类型、配置参数、以及性能分析等方面。下面将对这些理论基础进行详细阐述。

## 2.1 SelectIO架构解析

### 2.1.1 SelectIO信号路径

SelectIO信号路径是指从FPGA芯片内部逻辑单元到芯片外部世界之间的信号传输通道。一个典型的SelectIO信号路径包含以下几个关键部分:

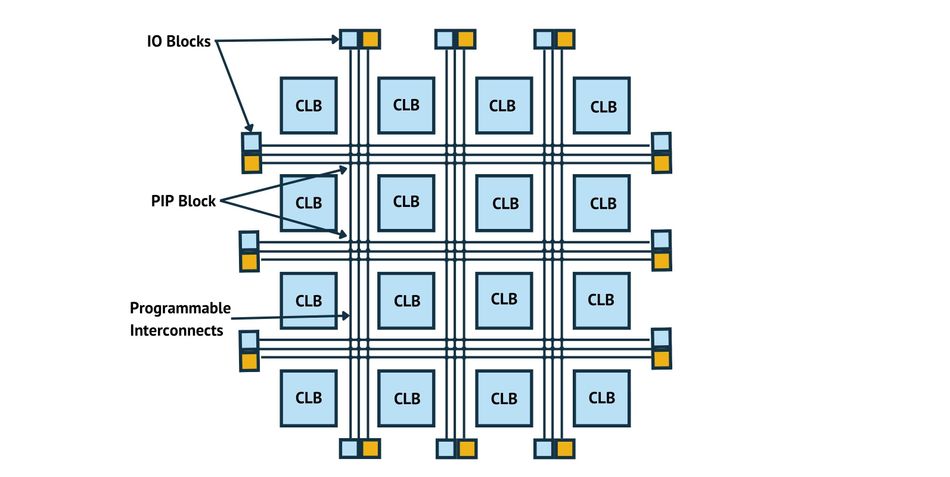

- **内部逻辑单元(Logic Cells)**:逻辑单元是FPGA内部用于处理信号的单元。在SelectIO架构中,逻辑单元通常位于FPGA芯片的核心区域。

- **输入/输出块(I/O Blocks, IOBs)**:IOBs是位于FPGA芯片边缘的特殊电路模块,主要负责信号的输入输出功能。每个IOB都包含了多个引脚,可以配置为信号输入、输出或双向信号。

- **输入/输出缓冲区(Buffers)**:信号在IOBs中传输时,需要经过缓冲区。缓冲区可以是上拉、下拉、三态或双向缓冲器,用于增强信号的驱动能力,并提供必要的电气特性。

- **FPGA内部互连网络**:这是连接内部逻辑单元和IOBs的布线资源。SelectIO架构通常采用灵活的互连网络,以支持不同的I/O标准和配置需求。

- **芯片封装引脚(Package Pins)**:FPGA的封装引脚负责将信号连接到外部的PCB(印刷电路板)。

### 2.1.2 SelectIO的驱动和接收器类型

SelectIO支持多种驱动和接收器类型,这些类型的选择对于信号质量和电气特性至关重要。

- **驱动器(Drivers)**:驱动器主要负责将内部逻辑单元的信号传输到外部世界。SelectIO技术提供了多种驱动器类型,如LVDS、HSTL、SSTL等,它们都具有不同的电气特性和信号速率。

- **接收器(Receivers)**:接收器则用于从外部世界接收信号,并将其传输到FPGA内部。接收器同样需要与信号的特性相匹配,常见的接收器类型包括CMOS、LVCMOS等。

SelectIO的驱动和接收器类型的选择依赖于信号传输的具体需求和标准,例如:

```mermaid

flowchart LR

SubsystemA[内部逻辑单元] -->|驱动| Driver[驱动器]

Driver -->|信号| PackagePin[封装引脚]

PackagePin -->|环境| SubsystemB[外部设备]

SubsystemB -->|信号| Receiver[接收器]

Receiver -->|接收| SubsystemA

```

## 2.2 SelectIO的配置参数

### 2.2.1 I/O标准的选择与应用

在SelectIO架构中,I/O标准的选择至关重要,它直接影响到FPGA的性能和可靠性。常见的I/O标准包括:

- **LVCMOS**(低压CMOS):适用于低速、低功耗的应用场景。

- **LVDS**(低压差分信号):用于高速信号传输,具有较高的抗干扰能力和传输距离。

- **HSTL**(高摆幅终端逻辑):常用于存储器接口,如DDR SDRAM。

- **SSTL**(串行终端逻辑):用于高速存储器接口,如DDR2/DDR3。

在设计中选择合适的I/O标准时,需要考虑以下因素:

- 信号速率和数据传输率。

- 电源电压和电流要求。

- 信号的电气特性。

- 可用的I/O引脚数量。

### 2.2.2 时钟管理与同步机制

时钟是数字电路中用于同步信号和操作的脉冲信号。在SelectIO架构中,良好的时钟管理至关重要。

- **全局时钟网络(Global Clock Networks)**:用于提供全芯片范围内的时钟信号,确保信号同步。

- **区域时钟(Regional Clocks)**:提供给特定区域的时钟信号,减少资源的消耗。

- **专用时钟引脚(Dedicated Clock Pins)**:用于外部时钟源的接入,其路径短、延迟低。

时钟管理中还会应用到同步机制,例如:

- **锁相环(Phase-Lock

0

0