【FPGA开发转型必读】:Vitis与传统FPGA在lib库应用的差异分析

发布时间: 2024-12-14 07:36:57 阅读量: 1 订阅数: 3

参考资源链接:[VITIS创建与应用静态库lib文件指南](https://wenku.csdn.net/doc/sy8jf297n9?spm=1055.2635.3001.10343)

# 1. FPGA开发转型概述

## 简介

FPGA(现场可编程门阵列)技术历经数十年的发展,已经在通信、军事、医疗等领域占据举足轻重的地位。随着设计复杂性的提高,传统FPGA开发方式已经不能完全满足现代应用的需求。因此,越来越多的工程师开始转向使用更高效、更现代化的开发工具,如Xilinx的Vitis。

## 转型的必然性

FPGA开发的转型不仅与技术进步有关,还与市场需求紧密相关。一方面,现代FPGA的规模和复杂性要求工程师们提高生产力,而传统工具的局限性开始成为创新的障碍。另一方面,软件定义的硬件(SDSoC)理念和高层次综合(HLS)技术的兴起,也促使FPGA开发流程向更灵活、更易于维护的方向发展。

## 转型的路径

随着Vitis等集成开发环境的推出,FPGA开发人员获得了全新的设计平台。Vitis不仅仅是硬件描述语言(HDL)的替代品,它提供了一个完整的开发环境,支持从软件开发到硬件实现的全流程。本章将探讨FPGA开发转型的背景,转型的意义以及转型中的关键步骤。

# 2. Vitis开发环境基础

### 2.1 Vitis环境介绍

#### 2.1.1 Vitis的安装与配置

Vitis是Xilinx推出的统一软件平台,旨在加速可编程逻辑和异构计算应用的开发。对于开发者而言,安装Vitis环境是展开工作的第一步。这一过程包括了下载安装包、配置系统环境变量、安装必要的依赖项和验证安装。

**步骤概述:**

1. **系统要求检查**:确认操作系统版本和硬件需求是否满足Vitis支持的条件。

2. **下载安装包**:访问Xilinx官方网站或通过Vitis软件平台获取安装包。

3. **运行安装向导**:执行安装程序并遵循向导提示进行安装。

4. **配置环境变量**:安装完成后,根据提示或自行操作配置环境变量,例如`PATH`和`LD_LIBRARY_PATH`。

5. **安装依赖软件**:安装Vitis运行所需的依赖软件包,例如JRE和GraphicsMagick。

6. **验证安装**:运行Vitis IDE并创建一个新项目验证安装是否成功。

**代码块示例:**

```bash

# 示例安装脚本

tar -xvzf vitis_2022.1.tar.gz # 解压安装包

export VITIS=<Vitis安路径>

source $VITIS/settings64.sh # 配置环境变量

./xsetup # 启动安装向导

```

**参数说明:**

- `VITIS`:指定Vitis安装的路径。

- `settings64.sh`:包含环境变量配置的脚本。

**逻辑分析:**

上述脚本中的每一步都至关重要,特别是在配置环境变量的时候,正确设置路径可以确保在终端任何位置都能直接运行Vitis命令。

**扩展性说明:**

在实际环境中,需要根据自己的操作系统和具体需求调整安装路径和配置内容。如果遇到问题,比如许可证问题或者网络连接问题,需查看Xilinx的官方文档获取进一步的帮助。

#### 2.1.2 Vitis的工作空间和项目管理

工作空间是Vitis中管理项目的地方。用户在Vitis中创建、打开、管理项目时,都是基于工作空间的概念进行操作。理解如何高效地利用工作空间和管理项目,对于提高开发效率非常关键。

**工作空间特性:**

- **项目组织**:工作空间可以包含多个项目,可以按项目类型、项目用途等进行分组。

- **视图定制**:用户可定制工作空间的布局和信息展示方式,适应个人或团队的工作习惯。

- **版本控制集成**:Vitis支持与Git等版本控制系统集成,便于代码版本管理。

**项目管理操作示例:**

```mermaid

graph LR

A[创建项目] --> B[设置项目属性]

B --> C[配置源文件]

C --> D[添加资源]

D --> E[构建项目]

E --> F[运行和调试]

```

**代码块示例:**

```bash

# 使用命令行创建Vitis项目

vitis -new project -name my_project -template application -location ~/vitis_workspaces

```

**参数说明:**

- `my_project`:新项目的名称。

- `-template application`:项目模板类型,这里是应用类型项目。

- `-location`:指定项目存储的位置。

**逻辑分析:**

上述命令行的参数指定了项目的名称、模板以及存储位置。这些参数是创建新项目时必须明确指定的,它们将直接影响项目的结构和内容。

**扩展性说明:**

在项目管理中,用户可能需要根据项目需求进行复杂的配置,如设置特定的编译器优化选项或链接脚本等。了解Vitis的项目属性设置,有助于在不同开发阶段实现更灵活的定制化开发。

### 2.2 Vitis与传统FPGA工具对比

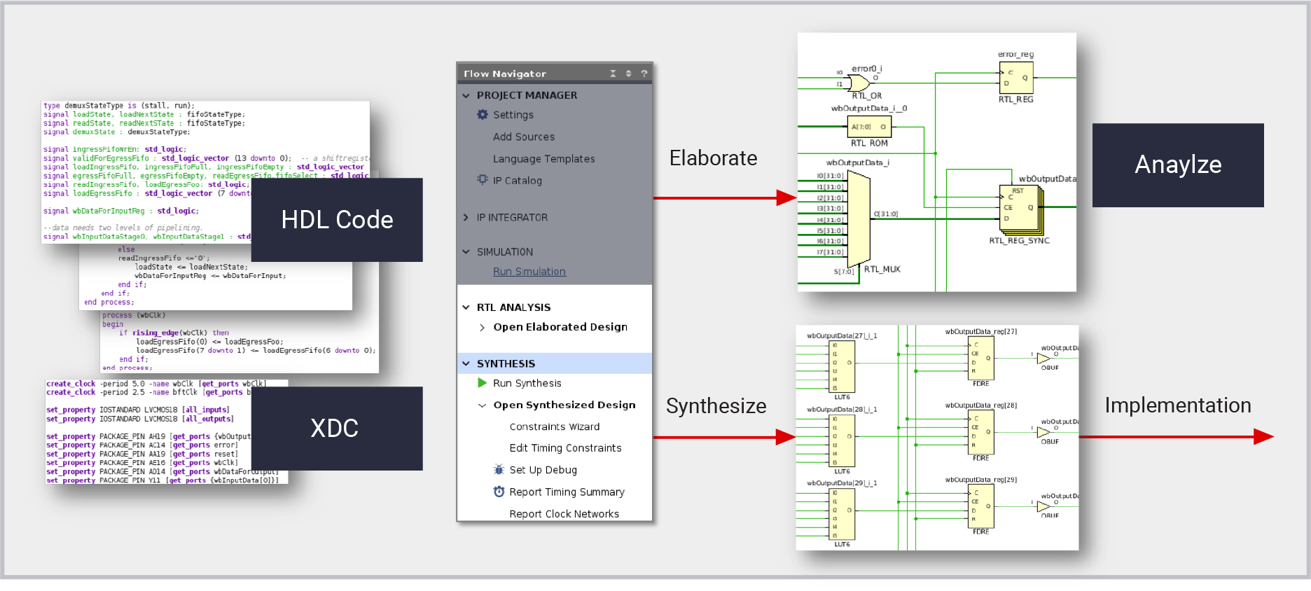

#### 2.2.1 开发流程的变革

Vitis在传统FPGA开发流程上做了不少改进,引入了高层次综合(HLS)和异构设计的思想,使得开发者能够以更接近软件开发的方式来设计FPGA。

**开发流程对比:**

- **传统工具流程**:编写HDL代码(如VHDL/Verilog),进行仿真测试,综合、实现、生成比特流,最后进行硬件验证。

- **Vitis流程**:代码编写(支持C/C++、OpenCL等),通过HLS工具转换为硬件实现,利用Vitis的集成开发环境进行调试和仿真。

**变革要点:**

1. **C/C++的全面支持**:Vitis使得用C/C++或HLS进行FPGA开发成为可能,这对于传统硬件设计者和软件开发者来说,都降低了进入门槛。

2. **软件仿真**:提供了一个更接近真实硬件执行的软件仿真环境,让开发者在硬件实现前就进行详尽的测试。

3. **系统级调试**:Vitis提供了一套更全面的调试工具,支持系统级的调试,进一步减少了硬件验证的需求。

**逻辑分析:**

Vitis的这些改变大幅提升了开发的效率和便捷性。例如,软件开发者可以使用熟悉的编程语言开发硬件加速功能,而无需深入理解硬件描述语言。

### 2.3 Vitis lib库的基本使用

#### 2.3.1 lib库的概念和结构

Vitis平台的库(lib库)是一组预先构建好的功能模块,这些模块可以被直接引用到用户项目中以加速开发过程。在FPGA开发中,库的概念与传统软件开发中的库有相似之处,但也有其独特性。

**库的类型:**

1. **Xilinx官方库**:提供优化的硬件加速模块,如数学运算

0

0