北邮信通院模电实验6学习笔记:JFET-CS放大电路的关键参数解锁

发布时间: 2024-12-17 02:01:20 阅读量: 10 订阅数: 12

北京邮电大学_信通院_模电实验六_JFET-CS放大电路测试报告

参考资源链接:[北邮信通院模电实验6_JFET-CS放大电路测试报告](https://wenku.csdn.net/doc/6412b58dbe7fbd1778d43905?spm=1055.2635.3001.10343)

# 1. JFET-CS放大电路概述

放大电路在电子设备中扮演着至关重要的角色,尤其是在要求高质量信号处理的场合。其中,结型场效应晶体管(JFET)共源(CS)放大电路由于其出色的线性特性和高输入阻抗,在许多应用中表现尤为突出。共源放大电路是将JFET作为放大元件,以共源连接方式设计的电路。它能够提供良好的放大性能,主要用于放大微弱信号,比如在音频系统、测量仪器和通信设备中的信号放大等场合。

在本章中,我们将从基本概念入手,逐步深入到JFET-CS放大电路的内部工作原理。首先,会介绍放大电路的定义及其重要性,然后概述JFET-CS放大电路的基本组成和功能。接下来,我们将探讨这类放大电路在电子系统中的应用范围以及它如何满足不同场合下的特定需求。

为了更好地理解,我们会举例说明JFET-CS放大电路在实际应用中如何提高电子设备的性能,例如,在音频放大器中,它能够提供低失真的音频信号,而在通信设备中,则能增强信号的传输质量。通过本章的学习,读者应能对JFET-CS放大电路有一个宏观的把握,并对其工作原理有一个初步的了解。

# 2. JFET-CS放大电路的理论基础

## 2.1 JFET的工作原理

### 2.1.1 JFET的基本结构和工作状态

结型场效应晶体管(Junction Field-Effect Transistor,JFET)是一种利用电场效应控制半导体内部电荷载流子数量来达到控制电流大小的半导体器件。它主要由三个部分构成:源极(Source)、漏极(Drain)和栅极(Gate)。JFET的栅极通过PN结与导电沟道(Channel)隔开,因此其工作特性受到栅极电压的控制。

JFET有N型和P型两种基本类型,分别对应沟道材料的不同。在N型JFET中,沟道是N型半导体,而栅极则由P型半导体构成。在P型JFET中,沟道是P型半导体,栅极则是N型半导体。不论哪种类型,当对栅极施加反向偏压时,栅极附近的载流子会被耗尽,导致导电沟道的有效宽度减小,从而改变漏极电流。

JFET在工作时,源极和漏极之间存在一个电压(Vds),同时在栅极和源极之间施加一个电压(Vgs)。根据Vgs的不同取值,JFET有以下几种工作状态:

- 截止状态:Vgs足够负,使得沟道被耗尽层完全夹断,此时漏极电流Id为零。

- 三极管区(Triode Region)或线性区:Vgs的绝对值较小,沟道仍然开放,Id与Vds之间存在线性关系。

- 夹断区(Pinch-off Region)或饱和区:Vgs绝对值较大,使沟道在漏极一端夹断,此时Id趋于饱和,主要由Vgs决定。

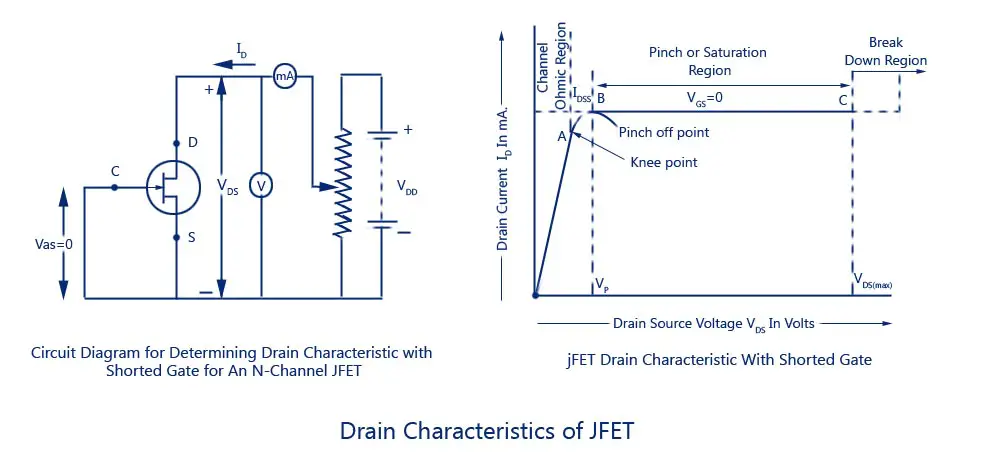

### 2.1.2 JFET的特性曲线和参数

JFET的静态工作特性主要由以下两个曲线描述:

- 转移特性曲线(Id - Vgs):表示漏极电流Id与栅极电压Vgs之间的关系。该曲线主要用来确定夹断电压(Vp)和跨导(gm)等参数。

- 输出特性曲线(Id - Vds):表示漏极电流Id与漏极电压Vds之间的关系,通常在不同的Vgs下绘制。在三极管区,Id随Vds线性增加;进入夹断区后,Id趋于饱和。

JFET的几个重要参数包括:

- 夹断电压(Vp):使沟道完全夹断的栅极电压的绝对值。

- 跨导(gm):漏极电流对栅极电压变化的敏感度,是衡量放大能力的一个重要参数。

- 源极电阻(rds(on)):漏极电流为饱和值时的漏极至源极电阻。

- 最大漏极电流(Idss):在Vgs=0时可以流过JFET的最大漏极电流。

理解JFET的工作原理和特性曲线是深入分析其放大电路功能的基础,接下来我们将探讨基于这些原理的基本放大电路。

## 2.2 基本放大电路的工作原理

### 2.2.1 共源放大电路的特点

共源放大电路是JFET应用中最基本的放大电路配置,它的特点是输入信号从栅极输入,输出信号从漏极取出。由于源极共地(或共其他参考电位),故得名“共源”。这种电路结构在放大中频信号时具有很好的放大能力,并且输入阻抗高、输出阻抗低,非常适用于信号源内阻较高而负载阻抗较低的应用场景。

共源放大电路的主要优点包括:

- 高输入阻抗:由于栅极几乎不抽取电流,因此对信号源的影响非常小。

- 较高的电压增益:由于负载连接在漏极,且漏极电流受到栅极电压的控制,所以电压增益较高。

- 线性度较好:相比共漏放大电路(源跟随器),共源放大电路的线性度更好。

然而,共源放大电路也有缺点:

- 输出阻抗较高:输出端直接连接到漏极,因此输出阻抗较高,不利于后级电路的驱动。

- 频率特性需要优化:由于存在内部电容效应,高频响应可能需要通过特定设计进行优化。

### 2.2.2 放大电路的关键参数解析

在设计和使用共源放大电路时,需要关注的关键参数主要包括:

- 开环增益:在没有反馈的情况下,放大器的增益。对于共源放大器,开环增益非常高。

- 输入阻抗:栅极对外电路的阻抗,一般非常高,可以达到数百兆欧姆。

- 输出阻抗:漏极对外电路的阻抗,相对较低,但是仍然有可能是几百到几千欧姆。

- 3dB带宽:在频域内,放大器的增益降低到最大增益的约70.7%(-3dB)时的频率范围。这是衡量放大器频率响应的一个重要指标。

为了确保放大电路的性能满足应用需求,必须对这些参数进行精确的设计和优化。特别是在多级放大、频率补偿和稳定性设计方面,需要仔细考虑电路参数的交互作用。

接下来,我们将深入探讨JFET-CS放大电路的理论分析,包括静态工作点的设定和小信号模型的建立。

## 2.3 JFET-CS放大电路的理论分析

### 2.3.1 电路的静态工作点分析

为了保证JFET-CS放大电路在放大信号时工作在最佳状态,首先需要设定一个合适的静态工作点。静态工作点是指放大器在没有输入信号时的直流工作状态,包括漏极电流Id和漏极电压Vds。对于共源放大电路来说,静态工作点主要由两个参数设定:栅极偏置电压Vgs和漏极电源电压Vdd。

工作点的选择需要满足以下条件:

- 漏极电流Id应位于放大器线性放大区的中心,避免进入截止区或饱和区。

- 漏极电压Vds应足够高,以确保信号的完整放大,但又不能太高以免增加功耗或超出器件安全工作区。

通常,静态工作点的设置需要通过实验调试,或使用电子负载等设备进行模拟和测试。在理论分析中,我们采用小信号模型来预测和评估电路的行为。

### 2.3.2 电路的小信

0

0