负载效应解决专家:JFET-CS放大电路的高效应对策略

发布时间: 2024-12-17 01:40:44 阅读量: 11 订阅数: 12

北京邮电大学_信通院_模电实验六_JFET-CS放大电路测试报告

参考资源链接:[北邮信通院模电实验6_JFET-CS放大电路测试报告](https://wenku.csdn.net/doc/6412b58dbe7fbd1778d43905?spm=1055.2635.3001.10343)

# 1. JFET-CS放大电路基础

在模拟电子技术领域,结型场效应晶体管共漏放大电路(JFET-CS)是应用广泛的电路结构之一,特别是在需要高输入阻抗和低输出阻抗的场合。JFET-CS放大电路通过利用结型场效应晶体管的特性,为信号处理提供了高效率的放大能力。本章节我们将简单介绍JFET-CS放大电路的基本概念,为深入探讨其工作原理、负载效应及其优化策略打下基础。

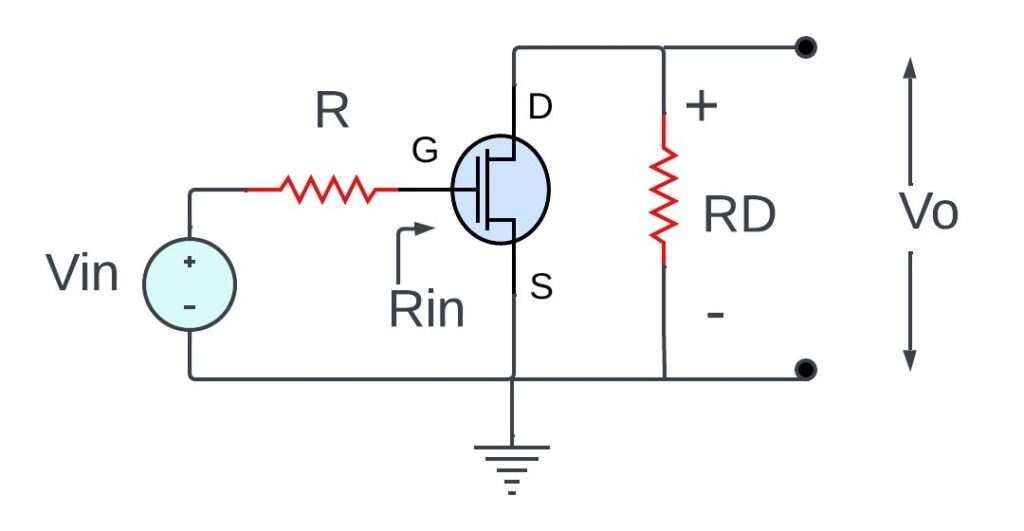

## 1.1 JFET-CS放大电路的基本组成

JFET-CS放大电路主要由结型场效应晶体管(JFET)、电源、负载电阻、偏置电阻以及输入输出连接器组成。电路的共同源(CS)配置允许信号在源极与漏极之间传输,从而实现放大功能。

## 1.2 放大原理简述

在JFET-CS放大电路中,输入信号通过调制JFET的漏极电流来实现放大。由于源极接地,输入信号会改变漏源之间的电压,从而影响漏极电流。漏极电流的变化导致输出端负载电阻上电压的变动,最终实现信号的放大。

## 1.3 JFET-CS放大电路的优势

相较于双极型晶体管放大电路,JFET-CS放大电路具有几个显著优势,包括极高的输入阻抗、较低的噪声水平以及较好的温度稳定性。这些优势使得它在信号弱、源阻抗高的环境中尤为适用。

通过本章对JFET-CS放大电路基础的介绍,我们为接下来章节深入分析其工作原理和负载效应奠定了坚实的基础。接下来,我们将详细了解JFET-CS放大电路的工作原理,以及负载效应对电路性能的潜在影响。

# 2. JFET-CS放大电路的工作原理

## 2.1 JFET-CS放大电路的基本构成

JFET-CS放大电路,即结型场效应晶体管(Junction Field-Effect Transistor)源极接地放大电路,是一种常用的模拟信号放大电路。它由三个基本部分组成:输入电路、放大器本体和输出电路。输入电路主要包括输入电阻和耦合电容,负责将信号源耦合到放大器并提供一定的输入阻抗;放大器本体由JFET组成,其核心工作区域是在其栅极-沟道之间形成的耗尽层,通过改变耗尽层的厚度来控制沟道的导电性;输出电路则通常由负载电阻构成,以实现信号的放大和输出。

## 2.2 JFET的工作特性

为了深入理解JFET-CS放大电路的工作原理,首先要分析JFET的工作特性。JFET是一种电压控制器件,其工作原理基于栅极电压对沟道中电流的控制作用。JFET的栅极和源极间存在一个PN结构,当栅极电压低于某一阈值电压时,沟道中形成导电路径,电流可从源极流向漏极。

- **栅-源电压(V_GS)和漏极电流(I_D)**:JFET的漏极电流(I_D)受栅-源电压(V_GS)的控制。当V_GS逐渐变负,沟道逐渐变窄,导致漏极电流(I_D)减少。

- **饱和区与夹断区**:在一定的漏极电压(V_DD)下,存在一个栅极电压(V_GS)使得漏极电流(I_D)达到饱和值。当V_GS变得更负时,沟道末端将被夹断,导致漏极电流(I_D)急剧减小,此时JFET进入夹断区。

## 2.3 信号放大过程分析

在JFET-CS放大电路中,信号放大过程主要发生在JFET的沟道区域。当交流输入信号被耦合到栅极时,输入信号电压的变化会改变栅极对沟道的控制能力,进而影响到漏极电流的大小。由于漏极电流流过负载电阻,这将导致负载两端的电压变化,即输出电压的变化。输出电压的变化与输入信号电压成比例,从而实现了信号的放大。

- **信号调制**:通过改变栅极电压(V_GS),可以调整沟道的电阻,进而调整漏极电流(I_D)。漏极电流的波动经过负载电阻转换成电压波动,实现信号的调制。

- **频率响应**:JFET-CS放大器的频率响应依赖于其电路设计。通常高频信号会被电容元件所衰减,而低频信号会受到电源线和接地线中电感的影响。

## 2.4 工作原理的数学表示

JFET-CS放大电路的工作原理可以通过一系列的数学公式来表示,这包括场效应晶体管的伏安特性方程和电路的负载线方程。其中,伏安特性方程用于描述漏极电流(I_D)与漏极电压(V_DS)、栅极电压(V_GS)之间的关系。负载线方程则描述了负载电阻(R_L)上电压与电流的关系。

- **JFET伏安特性方程**:I_D = I_DSS * (1 - V_GS/V_P)^2,其中I_DSS为夹断电流,V_P为夹断电压。

- **负载线方程**:V_DD = I_D * R_L + V_DS,说明了漏极电压(V_DD)被分配到负载电阻(R_L)和漏极-源极之间。

这些方程与电路的配置相结合,可以预测放大电路的性能,并用于设计目的。通过这些方程,工程师可以优化电路参数,以实现所需的放大效果。

### 2.4.1 伏安特性方程深入解析

```math

I_D = I_DSS \cdot \left(1 - \frac{V_{GS}}{V_P}\right)^2

```

该方程表明了漏极电流I_D与栅-源电压V_GS之间的关系,它揭示了JFET的非线性特性。当栅-源电压V_GS为零时,漏极电流I_D达到最大值I_DSS,即夹断电流。随着V_GS变得更负,夹断电压V_P以下的电流迅速下降。该非线性特性在电路设计中需要仔细考虑,因为放大器的线性度直接影响到放大信号的质量。

### 2.4.2 负载线方程实例应用

```math

V_{DD} = I_D \cdot R_L +

```

0

0