【确保模型正确导入的Verilog检查清单】:HSPICE仿真前必做步骤

发布时间: 2024-12-17 18:21:05 订阅数: 3

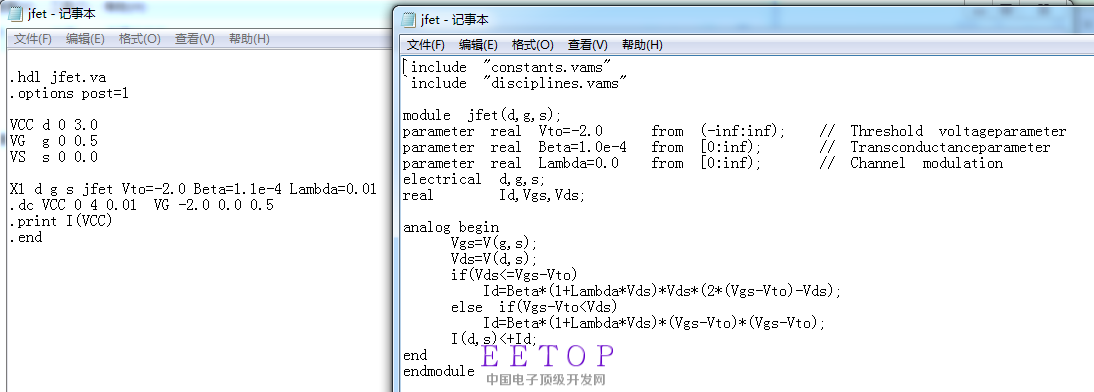

veriloga的模型导入hspice的方法

参考资源链接:[Verilog-A到HSPICE模型导入教程:混合仿真的关键](https://wenku.csdn.net/doc/6412b466be7fbd1778d3f79a?spm=1055.2635.3001.10343)

# 1. Verilog模型导入的重要性

在数字电路设计和验证的过程中,模型导入是至关重要的一环。正确导入模型可以确保仿真的真实性和准确性,从而直接影响到后续硬件设计的可靠性和性能。通过对模型的导入进行细致的检查和验证,工程师能够及早发现潜在的设计缺陷,避免在项目后期产生昂贵的修改成本。本章我们将深入探讨模型导入的重要性,并通过案例分析来展示其在实际工程中的应用。

# 2. Verilog检查清单的理论基础

### 2.1 Verilog语言的简介

在集成电路设计和数字系统建模领域,Verilog语言是不可或缺的工具之一。它不仅简化了复杂电路的设计过程,而且通过模块化的设计,为硬件的仿真和验证提供了极大的便利。

#### 2.1.1 Verilog的基本语法和构造

Verilog是一种硬件描述语言(HDL),它的基本语法包括模块、端口、赋值语句、条件语句等。我们可以通过以下代码块了解Verilog的基本语法结构:

```verilog

module my_module(input wire a, input wire b, output wire c);

// 基本逻辑运算

assign c = a & b; // AND门

endmodule

```

#### 2.1.2 Verilog的数据类型和操作符

Verilog支持多种数据类型,包括向量(如`reg[7:0]`)和标量(如`wire`)。此外,它还提供了一系列的操作符来进行位运算、逻辑运算等,例如`&`(位与)和`&&`(逻辑与)。代码块下提供一个操作符使用的简单例子:

```verilog

module bitwise_operators(input wire [3:0] a, input wire [3:0] b, output wire [3:0] c);

assign c = a & b; // 位与操作

endmodule

```

### 2.2 模拟与仿真流程概述

#### 2.2.1 模拟和仿真的基本概念

模拟是通过数学模型来仿真硬件电路的行为。它分为功能仿真和时序仿真。功能仿真只关注逻辑功能正确与否,而时序仿真则考虑信号的时序特性。以下的表格总结了两者的区别:

| 类型 | 目的 | 关注点 | 工具举例 |

|------------|------------------------------|------------------|-----------------|

| 功能仿真 | 验证电路逻辑是否正确 | 逻辑功能 | Verilog-XL, Icarus Verilog |

| 时序仿真 | 确保电路在时钟约束下正常工作 | 信号时序特性 | HSPICE, VCS |

#### 2.2.2 HSPICE在Verilog仿真中的角色

HSPICE是业界标准的电路仿真软件,特别擅长进行精确的时序仿真和信号完整性分析。它与Verilog仿真结合,能够帮助工程师精确模拟复杂电路的行为。下面是使用HSPICE进行仿真的一段代码:

```spice

* HSPICE simulation netlist

.include 'my_module.sp'

VIN in 0 PULSE(0 1 0 1ns 1ns 10ns 20ns)

CLOAD out 0 1pF

.tran 1ns 30ns

.option post=2

.end

```

### 2.3 检查清单的目的和原则

#### 2.3.1 预防错误和缺陷的方法

检查清单是预防错误和缺陷的有效工具。它通过列出一系列步骤,确保设计过程中的关键环节得到妥善处理。以下是设计一个检查清单的示例:

- 检查所有模块的输入输出端口是否定义正确。

- 验证所有模块的时钟域是否清晰定义。

#### 2.3.2 检查清单在项目管理中的作用

检查清单有助于保持项目的组织性和可追踪性。它们不仅能够促进团队成员之间的沟通,还能帮助项目管理者跟踪项目进度和质量控制。下表展示了检查清单在项目管理中的作用:

| 作用 | 描述 |

|----------------------------|----------------------------------------------------------------------------------------|

| 促进团队沟通 | 通过标准化的检查项,确保团队成员之间有共同的理解和目标。 |

| 提高项目可追踪性 | 对每个设计阶段的关键检查点进行追踪,确保项目按照既定流程推进。 |

| 质量控制和风险评估 | 检查清单能帮助识别潜在的风险点,并采取预防措施,以提高最终产品的质量。 |

| 支持文档管理和知识保留 | 检查清单作为项目文档的一部分,便于未来项目参考,同时也是知识管理的重要环节。 |

通过本章节的介绍,读者应该对Verilog检查清单有了基本的理解,包括Verilog的基本语法、仿真与仿真的基础流程,以及检查清单在预防错误和项目管理中的作用。在后续章节中,我们将深入探讨如何使用检查清单来确保HSPICE仿真的准确性,以及在实践中如何应用这些理论知识来提高设计效率和质量。

# 3. HSPICE仿真前的准备工作

在深入探讨Verilog检查清单的实践应用之前,我们必须确保仿真环境已经准备就绪,以便进行有效的设计验证。本章节将细致探讨在HSPICE环境下进行仿真的前期准备工作,包括环境和工具的配置、Verilog模块的设计与测试,以及仿真脚本的编写与调试。这些准备工作是建立在扎实的理论知识和实践经验之上的,对于确保最终仿真结果的准确性至关重要。

## 3.1 环境和工具的配置

在开始仿真之前,首先需要配置一个适合进行HSPICE仿真的环境。这包括硬件的准备、软件的安装以及环境变量的配置。只有这样,才能够确保HSPICE能够顺利运行并使用相应的资源。

### 3.1.1 安装HSPICE软件

HSPICE仿真软件需要在高性能的工作站或服务器上运行,通常操作系统为Unix/Linux。安装过程通常包括以下步骤:

1. 下载HSPICE软件安装包,通常以光盘映像文件(ISO)或其他封装格式存在。

2. 在服务器上挂载安装光盘映像,然后运行安装程序。

3. 遵循安装向导的指示进行安装,根据许可协议同意安装。

4. 在安装过程中可能需要输入许可密钥。

5. 安装完成后重启系统,以便系统完全识别HSPICE软件。

安装HSPICE后,还需要确保该软件能够在命令行中正常调用,这涉及到后续环境变量的设置。

### 3.1.2 配置仿真环境变量

环境变量对于HSPICE软件的运行至关重要,它们指定了软件的安装路径、许可文件路径等关键信息。以下是在Unix/Linux系统中设置HSPICE环境变量的步骤:

1. 打开终端,编辑用户的`.bashrc`或`.bash_profile`文件(取决于所使用的shell和Unix/Linux发行版)。

2. 在文件的末尾添加必要的环境变量设置,例如:

```sh

export PATH=$PATH:/opt/HSPICE安装路径/bin

export HSPICE许可服务器的主机名或IP地址

```

3. 保存并关闭文件,然后在终端执行`source .bashrc`或`source .bash_profile`使更改立即生效。

4. 测试HSPICE是否可以正常运行,通过输入`hspice`命令并检查是否能够进入HSPICE的命令行界面。

以上步骤完成了环境与工具的基本配置。然而,除了硬件和软件的准备,设计的验证还需依赖于合理设计的Verilog模块和对应的测试策略,这是下一小节要探讨的内容。

## 3.2 Verilog模块的设计和测试

在HSPICE仿真实验之前,设计的Verilog代码需要符合特定的标准并满足特定的质量要求。这意味着需要编写可测试的模块并使用单元测试来验证其功能。

### 3.2.1 编写可测试的Verilog模块

一个良好的可测试的Verilog模块需要满足以下条件:

1. **模块化**: 模块应该专注于单一功能,便于管理和复用。

2. **可配置性**: 通过参数来配置模块的行为,使其能够适应不同的测试场景。

3. **可观察性**: 模块输出清晰明确,便于检测到错误。

4. **

0

0