【解码器选购指南】:MIPI CSI-2 v3.0解码器技术规格与性能对比

发布时间: 2024-12-16 17:03:39 阅读量: 11 订阅数: 19

xilinx的mipi csi-2解决方案IP核

参考资源链接:[2019 MIPI CSI-2 V3.0官方手册:相机串行接口标准最新进展](https://wenku.csdn.net/doc/6401ad0fcce7214c316ee231?spm=1055.2635.3001.10343)

# 1. MIPI CSI-2 v3.0解码器技术概览

在移动设备与高清影像技术日益发展的今天,相机接口的标准也在不断地进化。移动行业处理器接口(MIPI)联盟推出的Camera Serial Interface 2(CSI-2)已经成为移动设备相机模块与显示设备间通信的主导标准。本章将简要介绍MIPI CSI-2 v3.0解码器的基本概念及其应用背景。

## 1.1 了解MIPI CSI-2 v3.0的市场地位

MIPI CSI-2 v3.0是MIPI联盟在2018年发布的标准版本,它相比于前代版本,在数据传输速率、功耗效率以及错误校正等方面都有所提升。这一标准被广泛应用于智能手机、平板电脑以及其他移动计算设备中。通过理解这一标准,我们可以更好地理解移动设备中相机模块的工作原理及优化路径。

## 1.2 解码器在系统中的作用

在图像数据传输链路中,MIPI CSI-2 v3.0解码器扮演着至关重要的角色。它负责将传感器发送的高速串行信号解码为处理单元能够理解的并行信号。在这一章节中,我们将逐步剖析解码器的核心功能,并解释其如何影响整个图像传输的效率和质量。

这一概览为进一步深入了解MIPI CSI-2 v3.0技术打下了坚实的基础,为后续章节中对标准的详细解读和解码器技术的深入分析奠定了基石。

# 2. ```

# 第二章:MIPI CSI-2 v3.0标准详解

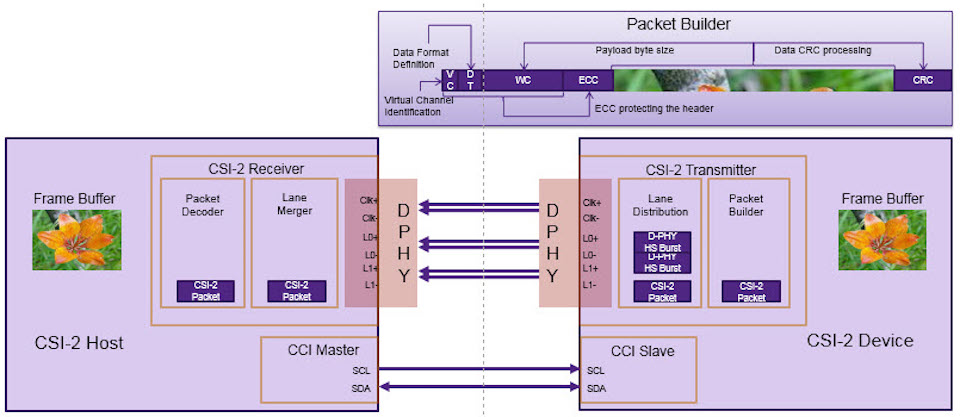

MIPI CSI-2 v3.0是移动设备中图像和视频数据传输的重要标准,它规定了在移动设备内部组件之间如何传输高速多媒体数据。本章将深入探讨该标准的各个方面,从通信协议基础开始,到时序控制与同步机制,以及数据包结构和Lane配置管理等内容。

## 2.1 通信协议基础

通信协议是任何数据传输系统的核心。MIPI CSI-2 v3.0协议定义了在不同设备组件之间如何可靠地传输数据。

### 2.1.1 数据传输原理

数据传输原理主要描述了数据包如何在MIPI CSI-2 v3.0接口上发送和接收。传输过程涉及物理层的数据编码和时序控制。该接口使用差分信号传输,其中数据和时钟都是通过专用的Lane进行传输的。为了确保数据的完整性和准确性,采用了低电压差分信号(LVDS)技术。每个Lane负责传输特定的数据信号,而时钟Lane则负责提供时钟信号以同步数据传输。

### 2.1.2 协议层次结构

MIPI CSI-2 v3.0协议的层次结构通常包括物理层、链路层和应用层。物理层负责在设备之间建立连接以及信号的发送和接收。链路层处理数据包的格式化、序列化以及差错控制。应用层负责数据包的内容和编码格式,它根据不同的应用场景要求不同的数据包格式。

## 2.2 信道与数据格式

信道和数据格式是决定数据传输效率和系统性能的关键因素。

### 2.2.1 Lane配置与管理

Lane配置与管理是MIPI CSI-2 v3.0标准中的一个重要方面。Lane是指物理接口中的单个差分信号对。为了实现高速数据传输,可以配置多个Lane并行工作。这样可以成倍增加数据传输的带宽。Lane配置可以是单个Lane、双Lane、四Lane或更多,取决于所需的总线宽度和速度。

Lane管理包括初始化序列、训练序列以及错误检测和重传机制。在初始化序列中,发送端和接收端会协商Lane的数量和速度。训练序列是用于确保所有Lane都已经正确同步并准备就绪,以便开始数据传输。错误检测和重传机制保证数据包的完整性,如果检测到错误,将请求重传。

### 2.2.2 数据包结构详解

数据包是MIPI CSI-2 v3.0接口上传输的最基本单位。每个数据包由头部(Header)、有效载荷(Payload)和尾部(Trailer)三部分组成。头部包含了包的类型、长度以及路由信息等;有效载荷包含了实际的数据;尾部则可能包含一些错误检测信息。

数据包结构的设计至关重要,它不仅要最小化开销,而且要提供足够的信息以确保数据能够被正确解析和处理。例如,包头部的特定字段可以用来指示数据包是图像数据、控制命令还是其他类型的数据。

## 2.3 时序控制与同步

时序控制和同步是任何数据传输系统中保证数据完整性的关键部分。

### 2.3.1 时钟域分析

在MIPI CSI-2 v3.0接口中,时钟域分析是指对数据传输过程中各个组件间时钟信号的管理和同步。因为数据传输涉及到多个设备,而这些设备可能使用各自独立的时钟源。为了避免时钟偏差导致的数据损坏,MIPI CSI-2 v3.0定义了严格的时钟同步机制。这包括使用独立的时钟Lane来传输时钟信号,并在物理层面上实现时钟恢复技术。

### 2.3.2 同步机制介绍

同步机制主要依赖于以下几个部分:

- **时钟同步**:如上所述,使用独立的时钟Lane。

- **帧同步**:数据传输以帧为单位进行,每个帧以特定的同步码字开始,接收端可以通过这些同步码字检测帧的开始和结束。

- **虚拟通道**:对于需要支持多个数据流的系统,虚拟通道允许在单一物理连接上复用不同的数据流。

下面是一个简单的表格展示时钟同步和帧同步的关键特性:

| 同步类型 | 关键特性 | 作用 |

| --- | --- | --- |

| 时钟同步 | 使用时钟Lane传输时钟信号 | 确保数据传输的同步 |

| 帧同步 | 通过同步码字开始和结束帧 | 准确地分割和同步帧 |

```

为了更好的理解时钟同步和帧同步的概念,我们可以用一个mermaid流程图来描述数据传输的过程。

```mermaid

g

```

0

0