Cadence 17.2 SIP电磁兼容性(EMC)设计:掌握预防干扰与合规测试的技巧

发布时间: 2024-12-26 15:19:55 阅读量: 5 订阅数: 8

# 摘要

电磁兼容性(EMC)是电子设备设计中的关键要素,它保证设备在电磁环境中能够正常运行而不产生无法接受的电磁干扰。本文系统介绍了EMC的基础知识及在Cadence SIP电磁设计中的应用,详细阐述了干扰的分类、EMC设计原则、Cadence SIP设计中EMC的策略和方法以及预防干扰的技术和组件选择。进一步,文章探讨了Cadence SIP EMC设计的实践步骤,包括前期的EMC准备、设计过程中的应用及后期的合规测试。本文还介绍了高级设计技巧,如EMC仿真工具的使用、解决复杂EMC问题的策略和预防和解决EMI的高级技术。最后,通过案例研究分析了EMC设计的成功与失败,展望了EMC设计的发展趋势和未来挑战,为电磁兼容性设计提供了全面的理论和实践指导。

# 关键字

电磁兼容性(EMC);Cadence SIP设计;干扰分类;EMC策略;仿真工具;EMI滤波器;案例研究

参考资源链接:[Cadence SIP设计详解:系统级别封装技术与流程](https://wenku.csdn.net/doc/jsb61shb63?spm=1055.2635.3001.10343)

# 1. 电磁兼容性(EMC)基础与重要性

电磁兼容性(EMC)是电子系统设计中的关键要素,它保证了在复杂电磁环境中设备能够正常运行,不受其他设备的干扰,同时也不对其他设备产生干扰。对于IT行业而言,EMC不仅是遵守行业标准的问题,更是产品稳定性和可靠性的重要保障。

## 1.1 EMC定义与作用

电磁兼容性(EMC)涉及到电子设备在其电磁环境中能正常工作,且不产生无法忍受的电磁干扰的能力。一个电子设备要想达到EMC要求,它必须具备两方面的能力:一是抗干扰能力,二是发射控制能力。良好的EMC设计能够降低电磁干扰(EMI),从而提高设备整体性能和用户体验。

## 1.2 影响EMC的因素

影响电磁兼容性的因素多种多样,包括但不限于设备的材料、设计、布局、电源管理、信号完整性、接地技术等。在IT设备中,如服务器、网络设备等,由于它们通常工作在高密度环境中,因此对EMC性能有着极高的要求。在设计初期就需要考虑到EMC的因素,避免后期因不合规带来的大量修改和成本增加。

## 1.3 EMC的重要性

从法规合规、产品性能到市场竞争力,EMC的重要性不言而喻。各国政府都制定了严格的标准和法规,强制电子产品满足一定的EMC要求。因此,EMC设计已成为产品开发不可或缺的一部分。一个符合EMC标准的产品能够提供更好的用户体验,并降低因电磁干扰导致的故障风险,从而提升企业的品牌形象和市场地位。

# 2. ```

# 第二章:Cadence SIP电磁设计的理论基础

## 2.1 电磁兼容性原理

### 2.1.1 干扰的分类和来源

干扰在电子设计领域内可以分为两大类:传导干扰和辐射干扰。传导干扰是指通过电路或电路板上的导线直接传输的干扰,如电源线、信号线等。此类干扰通常由于电流回路之间的不恰当耦合造成,诸如接地环路和共阻抗耦合等问题。

辐射干扰则来自于设备或系统产生的电磁场,这种干扰通过电磁波的形式在空间中传播。它们可能来源于高速开关电路、高频信号处理部分或外部电磁源。辐射干扰不仅对本系统中的其他部分造成影响,还可能干扰到其他设备的正常工作。

### 2.1.2 电磁兼容性设计的基本原则

电磁兼容性设计的一个基本原则是“共存原则”,即让系统内的各个设备或模块在工作时互不干扰。为了实现这一点,设计时要遵循“隔”、“避”、“抗”的综合策略。

- “隔”意味着在源头上对干扰进行隔离,例如通过使用隔离变换器、隔离接口等手段。

- “避”涉及避免干扰的产生和敏感电路的保护,比如通过合理的布线、布局减少信号的辐射和接收。

- “抗”则是提高电路或系统自身对干扰的抵抗能力,使用抗干扰滤波器、屏蔽材料等技术。

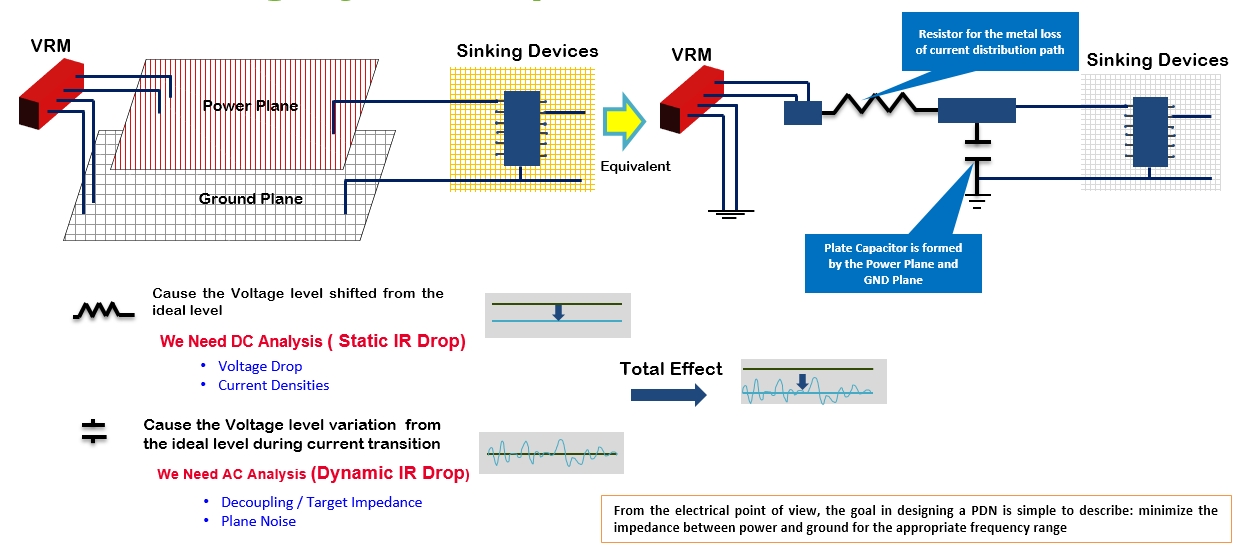

此外,电磁兼容性设计还需注意信号完整性和电源完整性,确保高速信号的质量不受干扰影响,同时保证供电质量,避免供电不稳定引起的工作异常。

## 2.2 Cadence SIP设计中的EMC考量

### 2.2.1 SIP设计中EMC的策略和方法

在Cadence SIP(System in Package)设计中实施EMC策略,首先需要识别哪些部分是高风险的EMC区域,并采用特定的设计方法和规则。例如:

- 使用多层布线设计以分散信号回路,从而减少电磁辐射。

- 为高速信号设置恰当的终端阻抗匹配,以防止信号反射引起的辐射。

- 在设计中加入信号完整性(SI)和电源完整性(PI)的检查,避免高频下的EMI问题。

为达到更好的EMC效果,设计者可利用Cadence工具集中的高级分析和优化功能,比如IBIS模型仿真,用于分析和优化引脚间的串扰。

### 2.2.2 预防干扰的关键技术和组件选择

SIP设计中预防干扰的核心技术包括:

- 屏蔽技术:通过金属外壳或屏蔽层来阻止电磁场的辐射和接收,减少外部干扰。

- 去耦合技术:在电路板上使用去耦电容,以确保电源的稳定性,减少因电源波动引起的干扰。

- 电路布局优化:合理布局关键信号路径,采用差分信号传输减少干扰。

组件选择方面,要特别注意:

- 选择高频率稳定性、低噪声的信号发生器和接收器组件。

- 使用合适的去耦电容,其大小和类型需根据信号频率和电流需求来确定。

- 应用高品质的屏蔽材料和封装技术,以适应不同环境下的EMC需求。

下一章节,我们将详细探讨Cadence SIP EMC设计的实践步骤,从设计前期的准备,到设计过程中的应用,以及设计完成后的合规测试。

```

# 3. Cadence SIP EMC设计的实践步骤

## 3.1 设计前期的EMC准备

### 3.1.1 电磁兼容性标准和法规要求

电磁兼容性(EMC)标准和法规是确保电子设备在其电磁环境中正常工作的关键。对于Cadence SIP(系统级封装)设计而言,了解并遵守相关的EMC标准至关重要,它们定义了设备必须满足的辐射和抗扰度性能指标。

例如,国际标准如IEC 61000系列和CISPR 22/24覆盖了电磁干扰(EMI)的限制和测试方法,是工业和消费者电子产品制造商必须遵守的规则。此外,特定国家可能有自己的EMC法规,例如美国的FCC Part 15和欧盟的CE标记认证要求。

在设计前期,工程师需要评估产品将要进入的市场的EMC标准,并确保设计满足这些标准。这通常需要与电磁兼容性测试实验室合作,以预测和

0

0