JK触发器波形图绘制:仿真软件运用与符号术语详解

发布时间: 2024-12-13 19:24:08 阅读量: 3 订阅数: 11

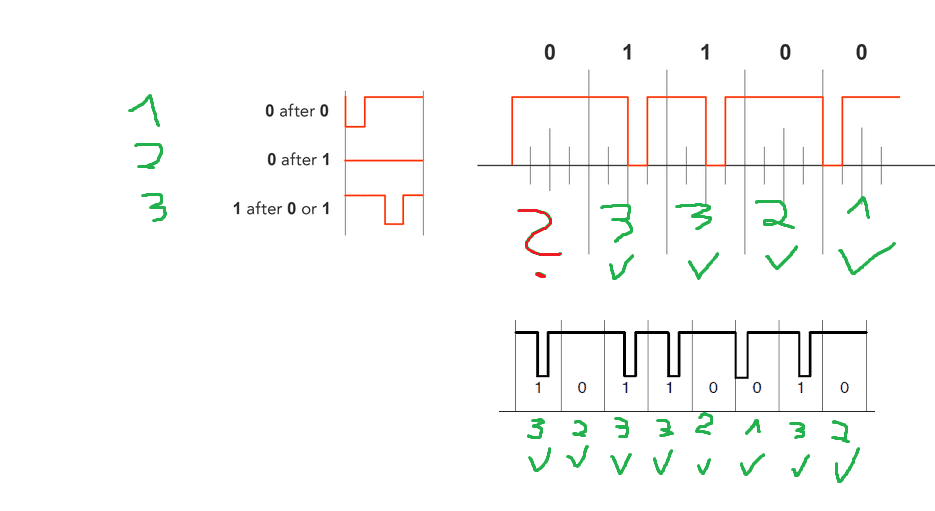

jk触发器波形图怎么画?主从jk触发器波形图

参考资源链接:[jk触发器波形图怎么画?主从jk触发器波形图](https://wenku.csdn.net/doc/645e416795996c03ac47f9d6?spm=1055.2635.3001.10343)

# 1. JK触发器波形图绘制概述

JK触发器是数字电路中非常重要的存储元件,它在时序逻辑电路设计中发挥着核心作用。波形图是展示数字信号随时间变化的图形表示,对于理解电路工作状态和调试电路至关重要。本章将简要介绍JK触发器波形图绘制的意义及其在工程实践中的应用,同时概览后续章节内容。

本章旨在帮助读者建立对JK触发器波形图绘制的基本认识,为后续深入分析和实践打下基础。我们会从JK触发器的定义和工作原理开始,逐步深入探讨波形图绘制的方法和技巧,以及在仿真软件中的应用和案例分析。

绘制JK触发器的波形图不仅是理论学习的验证,也是实际电路设计不可或缺的一步。通过本章的学习,读者将能够掌握JK触发器波形图绘制的基本概念和操作流程,为更复杂电路设计和分析奠定坚实的基础。

# 2. JK触发器理论基础

## 2.1 JK触发器的工作原理

### 2.1.1 逻辑电路图和功能表

在数字逻辑设计中,JK触发器是一种广泛使用的双稳态设备,能够存储1位二进制信息。其核心结构由两个交叉耦合的NAND或NOR门构成,根据输入J(置位)、K(复位)的不同组合,JK触发器可以控制输出Q的状态变化。下面是JK触发器的简化逻辑电路图:

```mermaid

graph TD

J[输入J] -->|与门| JK[与非门]

K[输入K] -->|与门| JK

JK -->|反向| Q[输出Q]

```

JK触发器的特性可以通过功能表来表示,显示了不同的输入组合导致的状态转换:

| J | K | Q(n) | Q(n+1) | 描述 |

|---|---|------|--------|------|

| 0 | 0 | 0 | 0 | 保持 |

| 0 | 0 | 1 | 1 | 保持 |

| 0 | 1 | 0 | 0 | 复位 |

| 0 | 1 | 1 | 0 | 复位 |

| 1 | 0 | 0 | 1 | 置位 |

| 1 | 0 | 1 | 1 | 置位 |

| 1 | 1 | 0 | 1 | 反转 |

| 1 | 1 | 1 | 0 | 反转 |

### 2.1.2 状态转换图和特性方程

状态转换图是一个描述JK触发器状态转移的图示,展示了在不同输入J和K的条件下,输出Q如何变化。状态转换图如下:

```mermaid

graph TD

A[0] -->|J=0,K=0| A

A -->|J=0,K=1| B

A -->|J=1,K=0| C

A -->|J=1,K=1| D

B[1] -->|J=0,K=0| B

B -->|J=0,K=1| B

B -->|J=1,K=0| C

B -->|J=1,K=1| D

C[2] -->|J=0,K=0| A

C -->|J=0,K=1| B

C -->|J=1,K=0| C

C -->|J=1,K=1| D

D[3] -->|J=0,K=0| A

D -->|J=0,K=1| B

D -->|J=1,K=0| C

D -->|J=1,K=1| D

```

JK触发器的特性方程可以表示为:

\[ Q_{(n+1)} = J \overline{Q_n} + \overline{K} Q_n \]

其中,\( Q_{(n+1)} \) 代表下一个状态,\( Q_n \) 代表当前状态,J和K是输入信号。特性方程说明了在J和K都为1的条件下,输出Q将会反转其当前状态。

## 2.2 JK触发器的模式分析

### 2.2.1 同步模式与异步模式

JK触发器可以工作在同步模式或异步模式。在同步模式下,所有的触发器在同一个时钟信号的边沿触发。而异步模式则允许触发器在不依赖于时钟信号的情况下立即响应输入信号的变化。

同步模式下,JK触发器的主要特点是可以实现更复杂的时序控制逻辑。在异步模式下,能够实现快速的置位和复位操作。对于设计者而言,选择合适的模式取决于具体的应用需求。

### 2.2.2 简化的特性表与JK触发器的稳定状态

JK触发器的简化的特性表是根据特性方程,省略了部分输入组合,从而得到了简化版的转换规则:

| J | K | Q(n+1) |

|---|---|--------|

| 0 | 0 | Q(n) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | \(\overline{Q(n)}\) |

简化的特性表强调了JK触发器的一个重要特性:在J和K均为高电平(1)时,输出Q将会在下一个时钟周期反转。这种特性使得JK触发器在设计时钟同步电路或计数器时非常有用,因为它可以在每个时钟周期都能够可靠地反转状态。

JK触发器的稳定状态是指在给定输入条件下,触发器的输出在没有新的有效输入改变的情况下保持不变。根据JK触发器的特性方程,我们可以分析得出在特定的输入J和K组合下,触发器具有稳定状态。例如,当J=0且K=0时,无论当前的输出Q是0还是1,触发器都会保持当前状态,这为设计稳定的工作电路提供了基础。

为了深入理解JK触发器的工作原理,设计者需要熟悉其逻辑电路图、功能表、状态转换图以及特性方程,这样才能够在数字电路设计中灵活应用JK触发器,解决各类时序逻辑问题。

# 3. 仿真软件的选择与环境搭建

## 3.1 常见的仿真软件介绍

### 3.1.1 仿真软件的功能对比

在数字电路设计和测试领域,仿真软件是不可或缺的工具,它允许工程师在实际构建电路前验证设计的有效性。市场上存在多种仿真软件,它们各自具备独特的功能和特点。以下是一些流行的数字电路仿真软件的对比。

- **VHDL/Verilog仿真器**:如ModelSim和Vivado,它们主要用于硬件描述语言(HDL)的仿真测试。它们支持高度的自定义,并允许用户在FPGA和ASIC设计的开发过程中进行早期验证。

- **SPICE仿真器**:如LTspice和Multisim,这些工具广泛用于模拟电路

0

0