JK触发器波形图绘制:揭秘电子工程师的必备技能

发布时间: 2024-12-13 18:36:19 阅读量: 7 订阅数: 11

参考资源链接:[jk触发器波形图怎么画?主从jk触发器波形图](https://wenku.csdn.net/doc/645e416795996c03ac47f9d6?spm=1055.2635.3001.10343)

# 1. JK触发器的基本概念与功能

JK触发器是数字逻辑电路中常用的一种触发器,它拥有较高的灵活性和可靠性,因此在各种数字系统设计中得到了广泛的应用。本章节将对JK触发器进行初步介绍,让读者了解其基本概念和功能,为接下来的深入学习打下坚实的基础。

触发器是一种双稳态电路,能够存储一个位的信息,即0或1。JK触发器作为一种改进型的RS触发器,它通过引入两个输入端(J和K)来改善了RS触发器的不确定状态。当J和K端同时为高电平时,触发器会切换其当前状态。此外,JK触发器在设计上还具有保持状态的能力。

具体地,本章节会围绕以下内容展开:

- JK触发器的定义和工作模式;

- JK触发器相对于其他类型触发器的特点;

- JK触发器在数字电路设计中的基本功能和应用场景。

通过这一章节的学习,读者将掌握JK触发器的核心概念,并为进一步的波形分析和应用案例研究奠定理论基础。

# 2. JK触发器的理论基础与波形分析

## 2.1 JK触发器的工作原理

### 2.1.1 逻辑电路的组成与功能

JK触发器是一种广泛应用于数字电路中的基本逻辑组件,它具有两个输入端(J和K)和两个输出端(Q和非Q)。JK触发器是RS触发器的改进版,其特点在于在某些特定输入条件下可以解决RS触发器的不确定状态问题。

从逻辑电路的组成来看,JK触发器通常由两个与非门或或非门交叉耦合而成。每个门的输出连接到另一个门的输入,形成了一个反馈循环。这种结构使得JK触发器在接收到新的输入信号时,能够根据J和K输入的变化来决定输出状态的变化。

JK触发器的功能在于存储信息,即根据输入信号的变化,改变或保持其内部状态,并将这些状态输出。在数字电路中,这种存储功能是构成复杂逻辑电路和存储设备的基础。

### 2.1.2 J和K输入的作用与特点

J和K输入是JK触发器的关键因素,它们决定了触发器状态的变化。具体来说:

- 当J=1且K=0时,触发器会置位(set),使得输出Q变为1。

- 当J=0且K=1时,触发器会复位(reset),使得输出Q变为0。

- 当J=0且K=0时,无论当前状态如何,触发器将保持当前状态不变。

- 当J=1且K=1时,触发器会切换其状态,即如果Q原来是1,则变为0;如果Q原来是0,则变为1。

这种特性使得JK触发器能够在多个时钟周期内提供稳定且可预测的输出状态。此外,JK触发器在J=K=1的条件下具有“切换”或“翻转”的能力,这在构建计数器和分频器等电路时非常有用。

## 2.2 JK触发器的状态表和特性方程

### 2.2.1 状态表的构建方法

状态表是描述JK触发器在不同输入状态下的输出状态的表格。构建状态表的基本步骤如下:

1. 确定触发器的输入变量(J和K)以及输出变量(Q和非Q)。

2. 列出所有可能的输入组合(J和K的四种组合)。

3. 根据JK触发器的工作原理,确定在每种输入组合下输出Q的预期状态。

4. 在表格中记录这些信息。

状态表是理解JK触发器行为的基础,它直观地展示了输入变化对输出的影响。通过状态表,工程师可以快速分析和预测电路在特定输入序列下的行为。

### 2.2.2 特性方程的理解与应用

特性方程描述了JK触发器的输出Q在下一个状态的逻辑表达式。对于JK触发器,特性方程通常表示为:

\[ Q_{(n+1)} = J \cdot \overline{Q_n} + \overline{K} \cdot Q_n \]

这个方程说明了在下一个时钟周期,输出Q的新状态是由J和K输入以及当前输出Q的状态共同决定的。

特性方程的理解与应用是设计和分析基于JK触发器的数字电路的关键。通过将特性方程应用于状态表,可以验证输出状态的正确性,也可以用来设计更加复杂的逻辑电路。

## 2.3 JK触发器的时序波形图

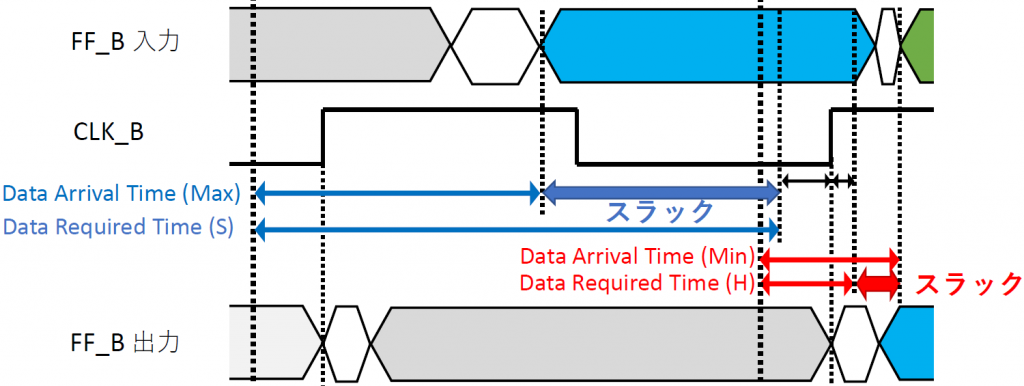

### 2.3.1 同步与异步工作模式

JK触发器可以工作在同步模式或异步模式下。在同步模式中,触发器的状态变化发生在时钟信号的边沿(通常是上升沿或下降沿)。这意味着所有的触发器在同一个时钟信号的边沿同时更新其状态。

而在异步模式中,触发器的状态变化不依赖于时钟信号,而是由输入信号直接控制。异步模式通常用于初始化或复位操作。

### 2.3.2 时序波形的绘制技巧

绘制JK触发器的时序波形图需要遵循一定的步骤和技巧:

1. 确定时钟信号的波形,并标记出其上升沿和下降沿。

2. 根据触发器的工作模式(同步或异步),确定输入J和K的变化时刻。

3. 根据特性方程,分析在每个时钟周期内Q的预期状态变化,并将其反映在波形图上。

4. 记录输出Q和非Q的波形,并与输入信号进行对比,确保逻辑一致性。

时序波形图是JK触发器逻辑分析的重要工具。它不仅帮助理解触发器在不同输入条件下的行为,还对设计更复杂的数字逻辑电路有着至关重要的作用。

# 3. JK触发器的波形图绘制实践

## 3.1 传统手动绘制方法

JK触发器作为一种通用的数字逻辑组件,在工程实践中经常需要通过波形图来分析其工作状态。本章节将详细介绍JK触发器波形图的手动绘制方法,为读者提供一个不依赖于电子模拟软件的实用绘制技巧。

### 3.1.1 绘图工具的准备与使用

在开始绘制之前,我们需要准备一些基础的绘图工具,例如:

- 笔和纸:最基本的工具,适合草图和初步设计。

- 直尺和圆规:用于绘制水平线和精确的圆弧,模拟触发器的时钟信号波形。

- 绘图软件:虽然这里强调手工绘制,但也可以利用一些简易的绘图软件如Paint等来提高精确度。

### 3.1.2 按时间顺序绘制波形

绘制JK触发器的波形图时,首先需要确定时钟周期T,并将其等分成若干个小的时间单元,便于标记不同时间点的状态变化。接下来,按照JK触发器的工作逻辑,标记J、K输入以及Q输出在每个时间单元的变化。具体步骤如下:

1. 画出时钟信号波形:垂直线表示上升沿和下降沿,水平线表示高电平和低电平状态。

2. 标记J和K输入的变化:在对应的时钟周期内,按照设计的输入序列,用“1”表示高电平,“0”表示低电平。

3. 根据JK触发器的状态表和特性方程,确定Q输出的变化,并记录下来。

4. 在每个时钟周期的交界处,根据J

0

0