【深入汇编世界】:多位数加法流程的深度解析

发布时间: 2024-12-27 05:06:04 阅读量: 7 订阅数: 13

20春川大《汇编语言程序设计2238》在线作业1(答案).docx

# 摘要

汇编语言作为一种低级编程语言,对于理解和优化硬件资源的使用至关重要。本文全面介绍了汇编语言的基本概念、多位数加法的理论与实践以及在硬件平台和加密算法中的具体应用。首先概述了汇编语言的基础知识,包括数据表示、指令集以及程序结构。随后深入探讨了多位数加法的理论基础,涉及数字系统转换、无符号和有符号数加法原理、以及错误检测与校验方法。接着,文章详细讲解了多位数加法的汇编实现技术,包括循环与递归实现、并行加法器设计及跨段处理。最后,本文结合实际案例分析了多位数加法在不同平台和领域中的应用,并展望了汇编语言及多位数加法技术的未来发展趋势,特别是在新技术架构中的应用挑战和持续学习的重要性。

# 关键字

汇编语言;多位数加法;数字系统;错误检测;并行加法器;性能优化

参考资源链接:[8086汇编语言:实现多个十进制数相加](https://wenku.csdn.net/doc/1n6sveeu7m?spm=1055.2635.3001.10343)

# 1. 汇编语言概述

汇编语言是一种低级编程语言,它与计算机的机器语言非常接近,但提供了更易于理解的符号指令来代表机器语言的复杂编码。每一个汇编指令通常对应着一条或多条机器指令。汇编语言的编写对于理解计算机硬件的工作原理、软件的性能优化以及与硬件交互的底层操作至关重要。掌握汇编语言能够让开发者深入硬件层面,对提高软件性能和解决底层问题有莫大的帮助。接下来的章节,我们将详细探讨汇编语言的基础知识和多位数加法的实现与应用。

# 2. 汇编语言基础

## 2.1 汇编语言的数据表示

### 2.1.1 数据类型和存储方式

在汇编语言中,数据类型的划分是基础而又至关重要的环节。数据类型决定了一块内存区域中能够存储的数据的性质以及占用的字节数。最基本的汇编语言数据类型包括字节(byte)、字(word)、双字(doubleword)和四字(quadword),它们分别占据1、2、4和8字节的内存空间。

内存中数据的存储方式也会影响数据的表示。数据可以按小端(little-endian)或大端(big-endian)的方式存储。小端存储意味着最低有效字节存储在最低的内存地址上,而大端存储则相反,最高有效字节存储在最低的内存地址上。

汇编语言对数据类型的处理主要是通过特定的指令集来实现。这些指令能够对内存中的数据进行加载、存储、转换等操作。例如,x86架构中使用mov指令来加载和存储数据,而lea指令则用于加载有效地址。理解数据类型和存储方式对于编写高效且正确的汇编代码至关重要。

### 2.1.2 寄存器的作用和分类

寄存器是CPU内部用来存放指令、数据和地址的高速存储单元。在汇编语言编程中,寄存器是性能优化和程序设计的基础。寄存器的分类按照用途大致可以分为以下几类:

- 通用寄存器:用于存储临时数据,执行算术、逻辑、数据传送等操作。

- 段寄存器:用于存储内存段的基地址,如代码段寄存器(CS)、数据段寄存器(DS)等。

- 指针和索引寄存器:用于存储数据的偏移量或指针,如指令指针(IP)、基指针(BP)、源索引寄存器(SI)、目标索引寄存器(DI)。

- 状态和控制寄存器:用于控制CPU的执行状态和指令流,如标志寄存器(FLAGS)。

寄存器的使用直接影响程序的性能。正确地利用寄存器可以减少对内存的访问次数,提高运算速度。此外,现代CPU还引入了诸如XMM、YMM等向量寄存器,用于支持并行数据处理,这些寄存器在处理多媒体数据或进行数学运算时尤为有用。

下面是一个简单的汇编代码示例,展示如何在x86架构中使用寄存器:

```assembly

mov eax, 1 ; 将数字1加载到EAX寄存器中,EAX是一个通用寄存器

add eax, eax ; 将EAX寄存器的值自身加1次,结果存储回EAX寄存器

```

此代码段将数字1加到EAX寄存器中的值上。由于EAX寄存器存储的是加法操作的结果,这个操作利用了寄存器的快速读写能力,显示了寄存器在执行简单算术运算时的重要性。

## 2.2 汇编语言的指令集

### 2.2.1 基本指令的理解与使用

汇编语言指令集是CPU能够识别和执行的最小功能单元集合。基本指令通常包括数据传输、算术运算、逻辑运算和控制流指令等。理解这些基本指令是学习汇编语言的基石。

例如,数据传输指令主要包括MOV、PUSH、POP等,用于在寄存器和内存之间或寄存器内部传递数据;算术运算指令包括ADD、SUB、MUL和DIV等,用于执行加减乘除等基本算术操作;逻辑运算指令则包括AND、OR、XOR和NOT等,它们用于处理布尔运算和位运算。

指令集不仅包含单一功能的指令,还包括复合操作的指令,如ADC(带进位的加法)、SBB(带借位的减法)等,这些指令在进行复杂计算时非常有用。

以x86架构为例,基本指令的使用如下:

```assembly

mov ax, 0x1234 ; 将立即数1234h传送到AX寄存器中

add ax, bx ; 将AX寄存器和BX寄存器的值相加,并将结果存储在AX寄存器中

inc ax ; 将AX寄存器的值加1

```

在上述代码中,我们首先将立即数1234h传送到AX寄存器中,然后与另一个寄存器BX的值相加,最后对AX寄存器的值进行自增操作。这些指令的执行都是在CPU的控制下完成的,指令的执行顺序和结果都会直接影响程序的状态。

### 2.2.2 指令寻址模式的深入探讨

寻址模式是指令如何确定操作数地址的一种方法,是汇编语言的一个重要概念。不同的寻址模式能够为指令提供操作数的不同来源和存储位置。常见的寻址模式包括立即寻址、直接寻址、间接寻址、寄存器寻址、基址寻址、变址寻址以及相对寻址等。

例如,在x86架构中:

- 立即寻址:操作数直接跟在指令后面作为立即数。

```assembly

mov ax, 5 ; 将立即数5传送到AX寄存器中

```

- 直接寻址:操作数的内存地址直接指定在指令中。

```assembly

mov ax, [1234h] ; 将内存地址为1234h的值传送到AX寄存器中

```

- 寄存器寻址:操作数存储在寄存器中。

```assembly

mov ax, bx ; 将BX寄存器的值传送到AX寄存器中

```

- 基址寻址:通过基址寄存器的内容加上偏移量来确定操作数的地址。

```assembly

mov ax, [bx+10h] ; 将以BX寄存器内容加上10h作为地址的内存中的值传送到AX寄存器中

```

- 变址寻址:在基址寻址的基础上加上一个变址寄存器的内容。

```assembly

mov ax, [bx+si] ; 将以BX寄存器内容加上SI寄存器内容作为地址的内存中的值传送到AX寄存器中

```

- 相对寻址:将程序计数器(PC)与一个偏移量结合使用来确定操作数地址。

```assembly

call label ; 调用当前指令后的label地址处的子程序

```

理解不同的寻址模式对于编写高效和功能性强的汇编程序至关重要。不同的寻址模式能够针对不同的操作数位置和大小进行优化,从而提高程序的执行效率和减少资源消耗。

## 2.3 汇编语言的程序结构

### 2.3.1 程序的基本流程控制

汇编语言的程序结构涉及程序的基本流程控制,流程控制是程序设计的核心。主要流程控制结构包括顺序结构、选择结构和循环结构。顺序结构是程序按指令顺序执行的最简单流程控制方式。选择结构允许程序在两个或多个操作之间选择执行,典型的选择结构包括if-else语句。循环结构则是指程序重复执行某段代码直到满足一定条件。

例如,在x86汇编语言中:

```assembly

mov eax, 10 ; 初始化计数器

start_loop:

add eax, 1 ; 增加计数器的值

cmp eax, 20 ; 比较计数器与20

jl start_loop ; 如果小于20,跳转回start_loop继续循环

```

该代码段演示了一个简单的循环结构,通过CMP和JL指令实现了对EAX寄存器值的判断和条件跳转。

### 2.3.2 段式结构和链接的原理

在x86架构的实模式下,程序使用段式结构来组织内存。程序的每个段都由一个段地址和一个偏移地址组成,组合起来就可以定位内存中的任意位置。每个程序通常包含代码段、数据段、堆栈段等,这些段在内存中是分开的。

链接是将不同部分的代码和数据组合成一个完整的可执行文件的过程。链接器负责将目标代码和库文件链接起来,解决符号引用,分配内存地址,并生成最终的可执行文件。

链接过程中的一个重要步骤是重定位,它解决了程序在内存中的实际位置变化问题。链接器在链接过程中,会调整程序中的地址引用,以确保程序在被加载到内存时能正确地执行。

```mermaid

graph LR

A[源代码文件] --> B[编译器]

B --> C[目标代码文件]

C --> D[链接器]

D --> E[可执行文件]

```

在上述流程中,编译器将源代码转换为机器码,产生目标代码文件。链接器则处理所有的目标文件,包括解析符号引用、重定位和最终输出可执行文件。通过这种方式,链接器确保了程序在运行时的完整性和正确性。

# 3. 多位数加法的理论基础

## 3.1 数字系统与多位数表示

### 3.1.1 二进制、八进制和十六进制数的转换

在汇编语言中,理解和掌握不同数字系统之间的转换是至关重要的。二进制、八进制和十六进制是计算机科学中经常使用的三种数制。了解它们之间的转换关系不仅有助于更好地理解计算机内部的存储和处理机制,而且在编程和调试过程中也是必不可少的技能。

以一个具体的例子来说明这些转换关系。考虑一个二进制数 `10110101`,我们可以通过分组的方式将其转换成八进制和十六进制:

二进制转八进制:

- 将二进制数按每三位一组(从右向左)进行分组:`101 101 010`

- 每组转换成相应的八进制数:`5 5 2`

- 所以,二进制数 `10110101` 对应的八进制表示为 `552`

二进制转十六进制:

- 将二进制数按每四位一组(从右向左)进行分组:`1011 0101`

- 每组转换成相应的十六进制数:`B 5`

- 所以,二进制数 `10110101` 对应的十六进制表示为 `B5`

在汇编语言编程中,通常通过直接使用不同的指令和格式来处理这些数制。例如,在x86汇编中,指令如 `MOV` 可以直接处理不同进制的数据,而特定的格式如 `.DB`、`.DW` 和 `.DD` 可以分别用来定义字节、字和双字大小的数据。

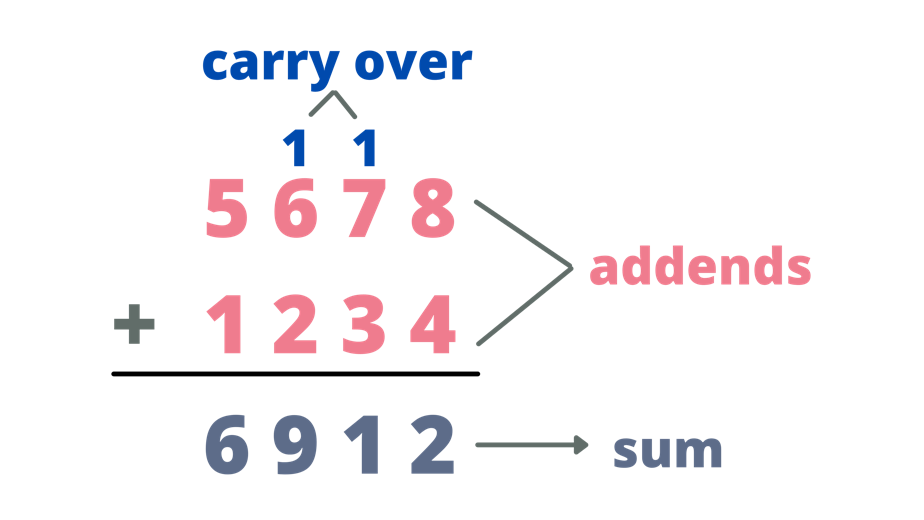

### 3.1.2 位运算基础与进位机制

多位数的加法涉及到位运算的基础知识,包括与(AND)、或(OR)、非(NOT)、异或(XOR)、左移(SHL)和右移(SHR)等。在汇编语言中,这些位运算由相应的指令实现,如 `AND`、`OR`、`NOT`、`XOR`、`SHL` 和 `SHR`。

位运算不仅仅是对单个位进行操作,更关键的是通过这些运算来实现复杂的数据操作和控制逻辑。例如,通过异或操作可以简单实现两个相同数值的加法,因为 `XOR` 操作会根据两个操作数的位值来决定结果位是0还是1,而相同位值的异或结果是0,这本质上相当于位的进位操作。

进位机制在多位数加法中尤为重要。在二进制数中,一个位加另一个位的结果如果是2或3,就需要向左边的高位进位。对于无符号数加法,一个简单的进位规则是:

```plaintext

0 + 0 = 0 (无进位)

0 + 1 = 1 (无进位)

1 + 0 = 1 (无进位)

1 + 1 = 0 (进位1)

```

在进位过程中,每一位的进位会传递到下一位。在汇编语言中,可以通过指令 `ADC`(带进位加法)来处理这种进位情况,其中会考虑前一位的进位结果。

在高级的汇编语言实现中,还可以利用指令如 `ADD`、`SUB` 等结合标志寄存器中的进位标志(carry flag)来实现多位数的加法。

```assembly

; 示例:32位二进制数加法

; 假设EDX:EAX和ECX:EBX是两个32位整数,我们要计算其和

; 结果将存储在EDX:EAX中

ADD EAX, EBX ; 加低32位

ADC EDX, ECX ; 加高32位,考虑进位

```

以上就是多位数加法在汇编语言中的理论基础,它涉及到数字系统的转换、位运算的基础知识以及进位机制的实现。在后续章节中,我们将深入探讨多位数加法的具体汇编实现方法。

# 4. 多位数加法的汇编实现

## 4.1 简单多位数加法实现

### 4.1.1 使用循环结构实现加法

在汇编语言中,实现多位数加法的一个基础方法是通过循环结构。循环可以让我们重复执行加法操作,直至所有位数加完。为了演示这一过程,我们将采用 x86 汇编语言来编写一个程序,实现两个多位数的逐位加法。

```assembly

section .data

num1 db '12345678', 0 ; 定义第一个多位数

num2 db '87654321', 0 ; 定义第二个多位数

sum db '000000000', 0 ; 存储结果的缓冲区

section .text

global _start

_start:

mov esi, 0 ; 初始化索引寄存器

mov ecx, 8 ; 循环次数,因为我们是8位数

; 循环结构开始

LoopStart:

mov al, [num1 + esi] ; 获取第一个数的当前位

mov bl, [num2 + esi] ; 获取第二个数的当前位

add al, bl ; 将两个位相加

aaa ; 根据结果调整AH和AL的值,如果产生了进位则设置进位标志

daa ; 将AL中的十进制调整为二进制表示

; 检查是否有进位,并更新sum

jnc NoCarry ; 如果没有进位,跳过进位处理

inc [sum + esi] ; 如果有进位,增加sum的当前位

NoCarry:

mov [sum + esi], al ; 存储加法结果的当前位

inc esi ; 移动到下一个字符

loop LoopStart ; 循环直到ECX为零

; 此处省略输出结果sum到控制台的代码

; 退出程序

mov eax, 1 ; 系统调用号(sys_exit)

xor ebx, ebx ; 返回值

int 0x80 ; 触发中断

```

以上代码段展示了如何使用循环结构实现两个多位数的加法。我们从最低位开始,逐位相加,并且利用`AAA`(ASCII Adjust after Addition)和`DAA`(Decimal Adjust after Addition)指令调整结果,确保以正确的格式存储。如果相加产生进位,则进位标志将被设置,并且相应地处理它。

### 4.1.2 使用递归实现加法

递归方法提供了一种不同的途径来实现多位数加法。递归函数可以调用自身来实现重复的操作,这种方式在处理数据结构时尤其有用,比如树或链表。下面是使用递归实现多位数加法的一个示例:

```assembly

section .data

num1 db '12345678', 0

num2 db '87654321', 0

sum db '000000000', 0

section .text

global _start

recursive_add:

push ebp

mov ebp, esp

push esi

push edi

push ebx

; 参数检查和准备工作

mov esi, [ebp+8] ; num1字符串的指针

mov edi, [ebp+12] ; num2字符串的指针

mov ebx, [ebp+16] ; sum字符串的指针

mov ecx, 8 ; 数字的位数

; 递归的终止条件检查

dec ecx

jns CallRecursive ; 如果还未完成所有位,则继续递归调用

; 终止条件:没有更多位要加了,直接跳转到清理环境

jmp CleanEnvironment

CallRecursive:

; 递归调用

call recursive_add

; 获取当前位的值

mov al, [esi + ecx] ; num1的当前位

sub al, '0' ; 转换为数字

mov bl, [edi + ecx] ; num2的当前位

sub bl, '0' ; 转换为数字

add al, bl ; 执行加法

aaa ; 调整结果

daa ; 调整为BCD表示

add al, '0' ; 转换回ASCII字符

mov [ebx + ecx], al ; 存储到sum中

jmp CallRecursive ; 递归调用下一个位

CleanEnvironment:

pop ebx

pop edi

pop esi

pop ebp

ret

_start:

; 此处省略调用recursive_add函数的代码

; 此处省略输出结果sum到控制台的代码

; 退出程序

mov eax, 1 ; 系统调用号(sys_exit)

xor ebx, ebx ; 返回值

int 0x80 ; 触发中断

```

在递归实现中,我们首先进行参数检查和准备,然后检查是否已经完成了所有位的加法。如果没有完成,我们进行递归调用,直到递归结束。每次调用都将当前位的值转换为数字,执行加法,调整结果,并将最终结果存回字符串中。

递归方法在逻辑上相对简单,但在实际的汇编语言实现中,递归可能不是最高效的解决方案,特别是在处理大型数字时,因为每次递归调用都会增加堆栈的使用,并且可能导致堆栈溢出。

## 4.2 高级多位数加法技术

### 4.2.1 并行加法器的设计与实现

并行加法器是实现多位数加法的另一个高级技术。并行加法器可以同时处理多个位,大大提升加法操作的效率。在硬件中,这可以通过全加器(full adder)电路实现,而在软件中,我们可以设计特定的算法来模拟这种行为。

在汇编语言中,我们可以利用处理器的多个寄存器同时进行加法操作。例如,在x86架构中,我们可以使用`PADDQ`指令来对64位整数进行并行加法操作。下面是一个简化的例子:

```assembly

section .data

num1 dq 0x1234567812345678 ; 64位数

num2 dq 0x8765432187654321 ; 64位数

sum dq 0x0 ; 存储结果

section .text

global _start

_start:

mov rax, qword [num1] ; 加载第一个64位数

mov rbx, qword [num2] ; 加载第二个64位数

paddq rax, rbx ; 并行加法指令

mov qword [sum], rax ; 存储结果

; 此处省略输出结果sum到控制台的代码

; 退出程序

mov eax, 1 ; 系统调用号(sys_exit)

xor ebx, ebx ; 返回值

int 0x80 ; 触发中断

```

这段代码使用了x86的SSE2指令集中的`PADDQ`指令来执行64位整数的并行加法。然而,由于汇编语言的操作通常限于处理较小的位宽,例如32位或64位,对于更大数字的处理则需要使用特殊的算法和数据结构来分块处理。

### 4.2.2 利用位操作优化加法性能

在某些情况下,我们可以使用位操作来优化加法性能。位操作是非常基础的操作,如位与(&)、位或(|)、位异或(^)和位非(~),它们可以用来实现快速的进位处理和二进制运算。

例如,我们可以通过逐位异或来计算两个数的和,同时使用逐位与来检测进位,然后左移一位再加上。这种方法可以提高加法的效率,特别是当处理的数字位数很多时。下面是一个例子:

```assembly

section .data

num1 db '12345678', 0

num2 db '87654321', 0

sum db '000000000', 0

section .text

global _start

_start:

mov esi, 0 ; 初始化索引寄存器

mov ecx, 8 ; 循环次数

AddLoop:

mov al, [num1 + esi] ; 加载num1的当前位

xor al, [num2 + esi] ; 逐位异或计算和

mov [sum + esi], al ; 存储和的当前位

mov al, [num1 + esi] ; 加载num1的当前位

and al, [num2 + esi] ; 逐位与检测进位

and al, 0x01 ; 限制到最低位

shl al, 1 ; 将进位左移一位

jz NoCarry ; 如果没有进位,跳过

inc [sum + esi] ; 如果有进位,增加sum的当前位

NoCarry:

inc esi ; 移动到下一个字符

loop AddLoop ; 循环直到ECX为零

; 此处省略输出结果sum到控制台的代码

; 退出程序

mov eax, 1 ; 系统调用号(sys_exit)

xor ebx, ebx ; 返回值

int 0x80 ; 触发中断

```

在这个示例中,我们通过异或操作计算了两个数的和,然后通过与操作和移位操作来检测和处理进位。这种方法可以减少一些操作的复杂度,从而优化性能。

## 4.3 跨段多位数加法处理

### 4.3.1 段间数据交换与处理

当处理的数据量超过了汇编程序段的大小限制时,就需要在不同的内存段之间交换和处理数据。在x86架构中,段寄存器如DS、ES、FS和GS可以用来访问不同的内存区域。我们可以利用这些寄存器来在不同的段之间移动数据。

```assembly

section .data

num1 db '12345678', 0

num2 db '87654321', 0

sum db '000000000', 0

section .text

global _start

_start:

; 初始化段寄存器

mov ax, ds ; 将数据段寄存器DS的值加载到AX

mov es, ax ; 将AX的值移动到附加段寄存器ES

; 此处省略加载num1和num2到各自段的代码

; 执行加法操作

; ...

; 此处省略将sum移动回DS段的代码

; 退出程序

mov eax, 1 ; 系统调用号(sys_exit)

xor ebx, ebx ; 返回值

int 0x80 ; 触发中断

```

在处理段间数据时,正确管理段寄存器非常关键,因为错误的段选择可能会导致程序运行失败。此外,跨段操作可能会涉及更复杂的内存管理,包括动态内存分配和段保护。

### 4.3.2 段地址的动态计算与存储

在某些情况下,需要动态计算和存储段地址。例如,当程序需要在运行时确定数据存储的位置时,就需要进行动态计算。在汇编语言中,可以通过基址加变址的寻址模式来实现这种动态计算。

```assembly

section .data

num1 db '12345678', 0

num2 db '87654321', 0

sum db '000000000', 0

section .text

global _start

_start:

; 基址加变址寻址模式动态计算段地址

lea esi, [num1] ; 将num1的地址加载到ESI

lea edi, [num2] ; 将num2的地址加载到EDI

lea ebx, [sum] ; 将sum的地址加载到EBX

; 此处省略加法操作的代码

; 退出程序

mov eax, 1 ; 系统调用号(sys_exit)

xor ebx, ebx ; 返回值

int 0x80 ; 触发中断

```

在这个例子中,`LEA`(Load Effective Address)指令用于加载有效地址到寄存器,这样可以进行动态的地址计算。动态计算段地址是一种有效的数据处理方法,尤其适用于数据存储位置在编译时未知的情况。

请注意,上述示例代码片段可能需要根据实际环境和硬件架构进行适当的调整才能正确执行。以上内容为示例,目的是为了更好地说明汇编语言中多位数加法的实现细节。

# 5. 汇编中的多位数加法应用实例

## 5.1 实际硬件平台上的加法程序

### 5.1.1 嵌入式系统中的应用案例

在嵌入式系统中,汇编语言常用于编写启动代码(Bootloader)、中断处理程序和需要精细控制硬件的场合。在这个层次上,多位数加法是一个基础且频繁的操作,因为它涉及到数据处理、校验和加密等多个方面。例如,在一个嵌入式设备中,可能需要将多个传感器的读数合并,而这通常涉及到多位数加法。

在实际的嵌入式应用中,多位数加法往往伴随着位操作和移位指令,因为这样可以更加精确地控制数据的每一位。例如,当使用汇编语言编程一个微控制器时,可以使用加法指令来实现累加操作:

```assembly

; 假设R1和R2是通用寄存器,包含两个多位数

; R3用于存储结果

MOV R1, #0x01 ; 将数值0x01加载到R1寄存器

MOV R2, #0x02 ; 将数值0x02加载到R2寄存器

ADD R3, R1, R2 ; 将R1和R2的值相加,结果存入R3寄存器

```

在上面的代码片段中,`MOV` 指令将数值加载到寄存器中,而 `ADD` 指令则执行了加法操作。需要注意的是,实际嵌入式系统中,多位数加法可能需要考虑溢出和进位的情况。因此,在使用加法指令时,程序员需要确保有适当的逻辑来处理这些情况。

### 5.1.2 PC平台上的应用程序实例

在个人计算机(PC)平台上,虽然高级语言如C/C++和Java在软件开发中占据主流,但依然有对性能要求极高的应用需要直接使用汇编语言来实现。在这些应用中,例如图形渲染、物理模拟和加密算法,多位数加法仍然是不可或缺的部分。

为了在PC平台上实现高效的多位数加法,开发者通常会利用现代处理器的SIMD(单指令多数据)扩展指令集。例如,在x86架构的处理器上,可以使用SSE(Streaming SIMD Extensions)指令集来实现多个数的并行加法,这能够显著提升性能。

下面是一个使用SSE指令集中的 `PADDB` 指令的例子,该指令用于对两个8位整数数组进行并行加法操作:

```assembly

; 假设MM0和MM1是MMX寄存器,包含两个整数数组

; MM2用于存储加法结果

MOVQ MM0, [esi] ; 将源数组1的值加载到MM0

MOVQ MM1, [edi] ; 将源数组2的值加载到MM1

PADDB MM2, MM0, MM1 ; 对MM0和MM1中的数组进行并行加法操作,并将结果存入MM2

```

在上述代码中,`MOVQ` 指令将内存中的数据加载到MMX寄存器,而 `PADDB` 指令则实现了8位整数的并行加法。SSE指令集大大提高了处理大量数据时的加法操作效率,从而在图形处理、视频编码等领域得到了广泛应用。

## 5.2 多位数加法在加密算法中的角色

### 5.2.1 加法在密码学中的基础地位

在密码学中,加法是构建更复杂算术运算的基础操作之一,特别是在流密码和分组密码算法中。例如,在实现一个简单的流密码时,一个伪随机数生成器(PRNG)可能需要不断地与明文或密文进行加法操作。

由于加密算法对速度和安全性都有极高的要求,因此在这些算法中,多位数加法通常会在数学上进行优化以抵抗某些类型的攻击。例如,一个广泛使用的加密算法RSA涉及到大数的模运算,而模加法则基于普通的加法操作。在实现模加法时,需要特别注意处理模数溢出的问题,保证结果正确。

```assembly

; 假设R1和R2是寄存器,它们的值是两个大数

; R3用于存储模加法的结果,R4包含模数

MOV R1, #largeNumber1

MOV R2, #largeNumber2

ADD R3, R1, R2 ; R3 = R1 + R2

CMP R3, R4 ; 比较R3和R4

JGE overflow_handler ; 如果R3 >= R4,则跳转到溢出处理

MOV R3, R3 ; 如果R3 < R4,则R3就是模加法的结果

```

在上述代码中,`CMP` 指令用于比较两个数的大小,而 `JGE` 指令则用于跳转到溢出处理代码(`overflow_handler`)。

### 5.2.2 实际加密算法中的应用分析

以AES加密算法为例,它在各个步骤中大量使用了加法操作,尤其是在密钥扩展和轮函数中。在密钥扩展中,通过加法和循环移位操作生成子密钥,而在轮函数中,通过与轮常数的加法操作来混合密钥和状态。

例如,在AES算法的一个轮变换中,可以通过一个简单的加法来实现列混淆:

```assembly

; 假设四个32位寄存器,R1, R2, R3, R4分别存储状态的列

; R5包含轮常数

ADD R1, R1, R5 ; 第一列加上轮常数

ADD R2, R2, R5 ; 第二列加上轮常数

ADD R3, R3, R5 ; 第三列加上轮常数

ADD R4, R4, R5 ; 第四列加上轮常数

; 此时R1, R2, R3, R4已经更新为新的状态列

```

在这个例子中,使用了四次 `ADD` 指令来实现四个状态列的加法操作。这种操作在加密算法的实现中非常常见,并且对执行速度和效率有着严格的要求。

## 5.3 多位数加法的性能测试与优化

### 5.3.1 常见性能测试方法

性能测试是评估汇编程序效率的关键步骤。多位数加法作为基本操作,其性能直接影响了整个程序的运行速度。在测试性能时,常用的方法包括基准测试、压力测试和分析工具的使用。

基准测试通常涉及多次运行加法操作并测量执行时间,以此来比较不同实现方法的效率。例如,在测试两个大数加法的性能时,可以运行以下基准测试:

```assembly

; 假设R1和R2是包含大数值的寄存器

; R3用于存储结果,R4是计数器

MOV R4, #1000000 ; 设置循环次数为100万次

test_loop_start:

ADD R3, R1, R2 ; 执行加法操作

DEC R4 ; 减少计数器

JNZ test_loop_start ; 如果计数器非零,继续循环

```

在这个测试中,使用 `JNZ` 指令来实现循环,并通过减少计数器来退出循环。最后,可以通过计算经过的时间来评估加法操作的性能。

### 5.3.2 优化策略与案例研究

在优化多位数加法时,一个常见的策略是利用处理器的缓存和流水线特性。这意味着要确保数据对齐并且尽可能减少分支。例如,通过使用无条件跳转(例如 `JMP`)代替条件跳转(例如 `JE` 或 `JNE`),可以减少流水线的复杂度,从而提升性能。

此外,还可以利用特定的汇编语言特性来改进性能。例如,在x86架构中,可以使用 `LEA`(加载有效地址)指令来替代一些加法操作,因为 `LEA` 可以在执行时不需要实际的算术运算:

```assembly

; 假设R1是基址,R2是偏移量,R3用于存储结果

LEA R3, [R1+R2] ; 计算R1和R2的和,并将结果存入R3

```

在这段代码中,`LEA` 指令执行了一个加法操作,但它实际上只计算地址,并不需要执行算术加法。因此,它通常比 `ADD` 指令执行得更快,特别是在重复执行许多次的时候。

在优化加法操作的过程中,开发者需要仔细评估各种方法的优劣,并根据特定的硬件平台和应用场景选择合适的优化策略。通过实际的性能测试和分析,可以确保优化措施有效且适宜。

# 6. 多位数加法的未来展望与挑战

随着科技的不断进步和计算机架构的发展,汇编语言和多位数加法的应用场景正在不断拓展。未来的展望不仅包括技术进步,也包含在新兴领域的应用前景和技术面临的挑战。

## 6.1 汇编语言的发展趋势

汇编语言作为一种底层语言,它的变化往往预示着处理器架构和计算机科学领域的发展动向。

### 6.1.1 新一代处理器对汇编语言的影响

随着新一代处理器的推出,汇编语言也在不断进化。例如,现代处理器采用多核心架构和更高级的指令集,如AVX512,它们为汇编程序员提供了更强大的计算能力和更宽的数据处理通道。这种变化意味着未来的汇编语言编程将更加注重并行处理和数据向量化。

```assembly

; 示例:使用AVX指令集进行向量加法

vmovaps ymm0, ymmword ptr [src1] ; 加载第一个向量

vaddps ymm1, ymm0, ymmword ptr [src2] ; 向量加法

vmovaps ymmword ptr [dst], ymm1 ; 存储结果

```

### 6.1.2 高级语言与汇编的交互发展

高级语言编译器的进步,如LLVM和GCC,它们生成的汇编代码质量越来越好,且支持更多的平台和架构。同时,高级语言开始提供内联汇编或内联汇编功能,允许在高级语言中直接使用汇编代码。这种交互发展促使汇编语言与高级语言的界限逐渐模糊,为开发者提供了更大的灵活性。

## 6.2 多位数加法在新领域的应用前景

多位数加法作为计算机科学的基础操作,它的应用正在拓展到更多新兴的领域。

### 6.2.1 量子计算中的算术运算

量子计算的出现为多位数加法带来了新的挑战与机遇。在量子计算中,传统的算术运算需要转换成量子比特(qubits)上的操作,而多位数加法在这一过程中扮演着关键角色。量子算法中,如量子傅里叶变换等关键步骤中就需要进行复杂数值计算。

### 6.2.2 生物信息学中的数据处理

生物信息学领域需要处理大量的基因数据,这些数据往往涉及到复杂的数值运算,包括多位数加法。例如,在DNA序列比对、蛋白质结构预测等生物计算任务中,高效的算术运算能够加快计算速度,提升分析效率。

## 6.3 持续学习与技术挑战

面对快速发展的技术领域,汇编语言和多位数加法的从业者需要不断学习和适应新技术。

### 6.3.1 持续教育与技能提升

在计算机科学的任何领域,持续学习都是职业发展的关键。汇编语言和多位数加法相关工作者需要定期更新自己的技能集,以适应不断变化的硬件和软件环境。学习资源包括在线课程、专业书籍、技术研讨会等。

### 6.3.2 面对新型计算架构的适应与挑战

新型计算架构,如异构计算(结合CPU、GPU、FPGA等多种处理器)和内存中心计算(内存与处理器的更紧密集成),对传统的多位数加法提出了新的挑战。程序员需要理解这些架构的特点,并对传统的算法进行优化,以充分利用新型架构的优势。

总结而言,多位数加法的未来是充满机遇与挑战的。无论是在传统计算机架构的优化,还是在量子计算和生物信息学等新领域中的应用,都要求我们不断学习和适应。只有这样,我们才能充分发挥多位数加法在现代计算中的潜力。

0

0