嵌入式系统中I2C集成与调试:高级技巧与实践案例

发布时间: 2024-12-05 02:54:20 阅读量: 35 订阅数: 37

参考资源链接:[I2C总线PCB设计详解与菊花链策略](https://wenku.csdn.net/doc/646c568a543f844488d076fd?spm=1055.2635.3001.10343)

# 1. I2C通信协议原理与架构

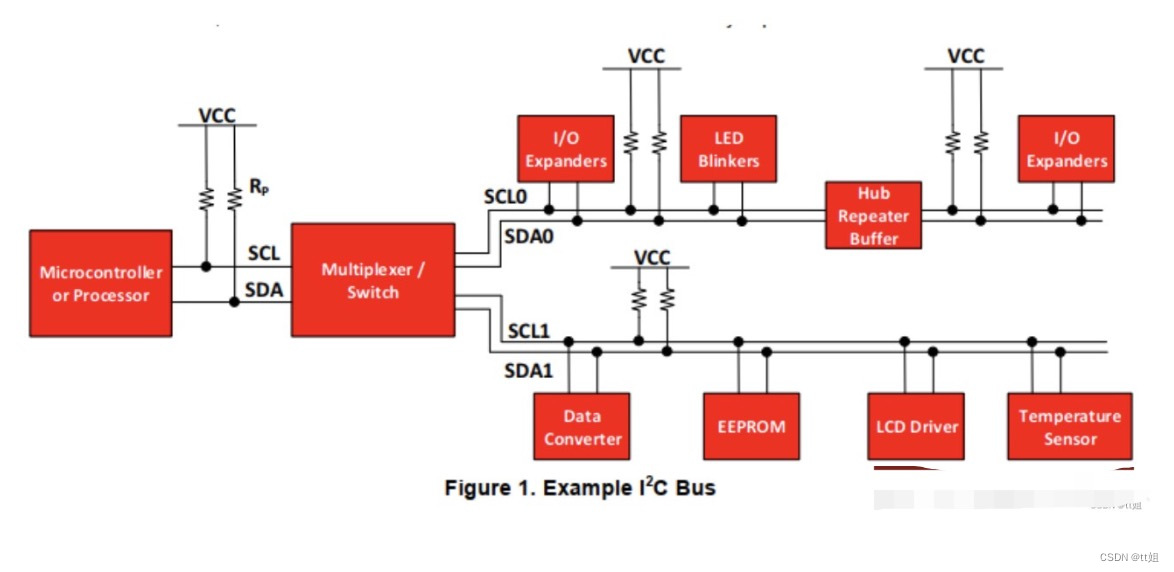

I2C(Inter-Integrated Circuit)是一种由飞利浦半导体公司(现恩智浦半导体)在1982年发起的串行通信协议,它广泛应用于微控制器和各种外围设备之间的短距离通信。该协议允许在一个总线上挂载多个从设备(Slave Devices),通过简单的两线接口,即数据线(SDA)和时钟线(SCL),实现主设备(Master)与从设备之间的数据传输。

## I2C通信协议的两个关键特性

1. **多主多从结构**:I2C支持多主模式,即多个主设备可以控制总线。这允许系统架构更加灵活,可以在主设备之间进行有效的任务分配和数据交换。

2. **地址识别**:每个I2C设备都有一个独特的7位或10位地址。主设备通过发送地址来选择特定的从设备进行通信,这种方式简化了硬件设计,因为不必为每个设备单独设置数据和时钟线。

在下一章节中,我们将深入探讨I2C设备的集成技术,并揭示如何在硬件层面实现I2C接口的配置以及编写与调试I2C设备驱动程序的技巧。

# 2. ```

# 第二章:I2C设备的集成技术

## 2.1 I2C硬件连接与配置

### 2.1.1 物理层接口标准

I2C(Inter-Integrated Circuit)通信协议以其简单的两线接口和多主机功能而广泛应用于微控制器和各种外围设备之间的通信。在硬件层面,I2C使用两条总线线——串行数据线(SDA)和串行时钟线(SCL)。SDA线上数据的传输是双向的,允许在设备之间发送和接收数据。SCL线用于提供时钟信号,以同步数据的发送和接收。

物理层接口标准的关键在于正确连接SDA和SCL线,同时确保I2C总线上连接的所有设备都能够符合规定的电压电平。例如,3.3V设备不能直接连接到5V I2C总线上,否则可能导致设备损坏。为了实现不同电压设备间的兼容,通常会使用电平转换器或具备电压调节能力的I2C缓冲器。

为了保证信号质量,总线上的设备数量和总线长度都需要受到限制。一般情况下,I2C总线长度不应超过10米,并且总线上连接的设备数量不应超过128个。当总线长度超过标准值或设备数量增加时,可能需要增加I2C线驱动器来扩展总线。

### 2.1.2 硬件配置要点

硬件配置要点包括上拉电阻的设置、总线速度的配置以及设备地址的分配。上拉电阻是确保I2C总线在空闲状态时为高电平的重要硬件组件。上拉电阻的阻值大小会直接影响到信号的质量和通信的速度。一般情况下,4.7kΩ或10kΩ的上拉电阻能够在大多数应用场景中提供良好的信号质量。

总线速度的配置关系到通信的效率和稳定性。I2C总线支持多种速率模式,包括标准模式(100kbps)、快速模式(400kbps)以及高速模式(3.4Mbps)。硬件配置时必须确保所有设备支持最高速率,并且在I2C控制器上正确设置了相应的速率。

设备地址的分配决定了I2C网络中每个设备的身份识别码。在设计I2C系统时,需要仔细规划每个设备的地址,以避免地址冲突。为了解决地址冲突,可以通过软件配置或硬件跳线的方式为设备分配唯一的地址。

## 2.2 I2C设备驱动开发

### 2.2.1 驱动框架与设备识别

I2C设备驱动的开发首先要确定驱动框架,以及如何在系统中识别设备。Linux内核中的I2C驱动框架是一种常见的实现方式,它为设备驱动的加载和卸载、设备的识别和数据传输提供了标准化的方法。设备识别在I2C驱动开发中尤为重要,通常通过设备的唯一I2C地址来识别设备。

驱动框架中的关键组件包括I2C适配器(Adapter)和I2C客户端(Client)模型。I2C适配器是指连接I2C总线的控制器硬件,而I2C客户端则是连接到I2C总线上的设备。驱动开发过程中,需要编写适配器驱动以初始化和控制I2C控制器,以及编写客户端驱动来处理具体设备的通信协议。

### 2.2.2 编写与调试设备驱动程序

编写设备驱动程序需要遵循特定的编程接口和协议。I2C设备驱动的编写通常涉及到定义设备描述结构体、初始化设备、以及实现数据的读写操作。例如,在Linux内核中,需要定义一个`i2c_driver`结构体,并实现`probe()`和`remove()`函数来完成设备的初始化和卸载工作。

在驱动程序的开发和调试过程中,可以利用内核提供的打印函数和日志级别来跟踪程序的执行流程和状态。例如,使用`pr_debug()`打印调试信息,通过内核日志级别(KERN_INFO, KERN_WARNING等)来控制信息的输出级别。

此外,编写驱动程序还需要进行单元测试和系统测试。单元测试可以通过模拟I2C通信过程来检查驱动程序的各个函数。系统测试则需要在实际硬件环境中进行,以验证驱动程序对各种情况的处理能力,包括正常通信、通信错误和设备异常等。

## 2.3 I2C通信故障排除

### 2.3.1 常见通信错误分析

I2C通信过程中可能出现的错误包括设备无法响应、通信超时、数据传输错误等。这些错误的出现可能由多种原因导致,包括但不限于硬件故障、配置错误、时序冲突或噪声干扰。

设备无法响应通常是由于设备地址设置错误或设备故障导致。在开发和调试过程中,可以通过发送设备识别命令(如“设备存在检测”命令)来检测设备是否在线和响应。

通信超时可能由软件编程错误、硬件故障或过长的传输距离引起。解决通信超时的方法包括检查硬件连接、降低总线速率、增加超时设置或优化数据传输逻辑。

数据传输错误可能是由于数据格式错误、数据位序列错误或总线噪声干扰引起。在数据传输过程中,应确保数据的完整性和准确性,必要时可以采用数据校验和重传机制。

### 2.3.2 故障诊断工具与方法

故障诊断的常用工具包括逻辑分析仪、数字示波器和专业的I2C分析软件。逻辑分析仪能够捕获并显示SDA和SCL线上信号的时间序列图,帮助开发者分析数据的传输时序是否正确。

数字示波器可以提供更精确的时间和电压测量,通过观察波形图可以判断出信号是否稳定以及是否存在噪声干扰。专业I2C分析软件则提供更为直观的总线监控和数据解码功能,便于用户进行故障分析和调试。

在诊断过程中,需要遵循以下步骤:

1. 首先检查硬件连接是否正确,包括SDA和SCL线是否正确连接,上拉电阻是否安装。

2. 检查设备地址是否设置正确,并确保没有地址冲突。

3. 利用诊断工具监控总线通信,查找不正常的信号波形或时序错误。

4. 通过软件手段,如I2C分析软件或调试工具,捕获总线上的数据并进行分析。

5. 如果问题依然无法解决,应考虑更换硬件或咨询设备制造商的技术支持。

```

# 3. 高级I2C集成技巧

## 3.1 I2C总线速度优化

### 3.1.1 速率匹配和时序调整

I2C协议支持多种速率模式,包括标准模式(100 kbit/s)、快速模式(400 kbit/s)以及最高速率可达3.4 Mbit/s的高速模式。优化I2C总线速度的关键在于实现速

0

0