掌握I2C高速模式设计:HS模式要点与实施策略

发布时间: 2024-12-05 03:04:25 阅读量: 30 订阅数: 37

I2C主机及从机Verilog代码实现.zip

参考资源链接:[I2C总线PCB设计详解与菊花链策略](https://wenku.csdn.net/doc/646c568a543f844488d076fd?spm=1055.2635.3001.10343)

# 1. I2C高速模式简介

I2C(Inter-Integrated Circuit)总线自1980年代初期由飞利浦半导体(现NXP)推出以来,已经成为电子工程中使用最广泛的串行总线之一。它允许不同硬件组件之间进行低速数据交换,广泛应用于微控制器与各种外围设备之间。随着技术进步和数据传输需求的增加,传统的I2C标准已经不能满足所有现代应用的需求。为了提高数据传输速率,I2C引入了高速模式(High-Speed mode,简称HS模式),使其传输速率可达3.4 MHz,这对于需要高数据吞吐量的应用如数字视频、高速模数转换器和先进传感器接口至关重要。本章将概述HS模式的基本特点,为后续章节中的技术细节和应用案例分析打下基础。

# 2. HS模式的技术要点

## 2.1 I2C总线标准的演进

### 2.1.1 传统模式与高速模式的对比

I2C总线的高速模式(High-Speed mode,简称HS mode),是随着对数据传输速率要求不断提高而引入的一种改进模式。传统的I2C标准,如标准模式(Standard-mode)和快速模式(Fast-mode),最高传输速率分别为100kbps和400kbps。在这些速率下,I2C总线足以应对大多数的系统需求。然而,随着高清视频、大数据、以及高速传感器数据等高带宽需求设备的普及,这些速率已经显得力不从心。因此,引入了HS模式,其最大传输速率可达3.4Mbps,极大地提高了I2C总线的数据吞吐量。

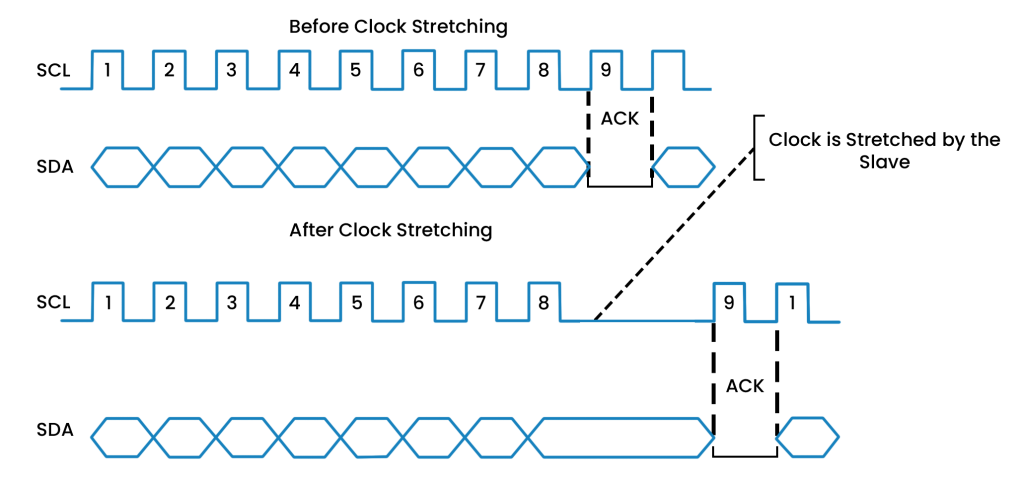

HS模式在硬件上与传统模式相比,最主要的改进是通过提高时钟频率和增加总线上的电流驱动能力来实现高速通信。在软件协议上,HS模式也增加了一些新的信号处理机制,如快速模式中的时钟拉伸(clock stretching)被快速模式加(Fast-mode Plus,简称Fm+)所取代,并在高速模式下进一步优化。

### 2.1.2 HS模式的物理层特性

HS模式的物理层特性主要体现在以下几个方面:

- **时钟频率**:HS模式下的时钟频率最高可达3.4MHz,远远超过传统模式。

- **总线电容**:为了在更高的频率下保持信号的完整性,HS模式对总线电容有更严格的限制。

- **驱动能力**:为了实现快速的信号上升和下降时间,HS模式的设备必须具备更强的驱动能力。

在HS模式下,I2C总线可以支持7位寻址和10位寻址两种模式,支持多主机(multi-master)操作。为了减少信号反射和串扰等高速通信中可能出现的问题,HS模式还引入了斜率控制机制,以减少电磁干扰(EMI)。

## 2.2 I2C高速模式的时序要求

### 2.2.1 容忍时间与保持时间的调整

在高速通信中,信号的时序要求变得更为严格。容忍时间(setup time)和保持时间(hold time)是在高速模式下特别需要注意的两个关键参数。HS模式要求设备在发送数据或时钟变化之前,要有足够的容忍时间以确保信号稳定;同样,数据在时钟边沿到来之前,需要保持稳定状态,以防止错误的信号识别。

由于信号的上升和下降时间变得非常快,HS模式规定了最小容忍时间和保持时间,以避免数据丢失。这些时间的缩短要求控制器和设备能够更加快速准确地处理信号,从而对硬件设计和软件算法提出了更高的要求。

### 2.2.2 高速模式下的启动与停止条件

高速模式下的启动(START)和停止(STOP)条件也有所变化。在标准模式和快速模式下,START和STOP条件由SCL线保持高电平和SDA线从高电平跳变到低电平(或相反)来定义。而在HS模式下,由于高速运行,为了避免误识别,START和STOP条件必须在SCL线为高电平时进行,且在变化之前,SDA线必须处于相反的稳定状态。

这些改变要求I2C控制器在设计时,能够精确控制信号的状态切换时间,以及设备能够正确解析高速条件下的START和STOP状态。

## 2.3 I2C高速模式的信号完整性

### 2.3.1 信号反射与串扰的控制

在高速通信过程中,信号在传输过程中会产生反射和串扰,这会严重影响信号的完整性。因此,在设计HS模式的I2C总线时,需要考虑如何控制这些信号问题。

信号反射是由于信号传输路径上的阻抗不连续性引起的。为了解决这个问题,高速I2C设备通常会采用阻抗匹配技术,确保传输线的特性阻抗与设备的阻抗一致,从而减少信号的反射。

串扰则是由于信号线之间的电磁耦合而产生,特别是在高速信号切换时,这种影响更为显著。为了减少串扰,设计时需要考虑总线布局,使信号线尽量分开,或者采用屏蔽线。

### 2.3.2 终端匹配与电磁兼容性(EMC)策略

为了进一步保证信号的完整性,HS模式下的I2C总线通常需要进行终端匹配。终端匹配技术主要包括并联终端电阻和使用电平转换器等方法。通过在总线末端添加适当的阻抗,可以有效地吸收多余的信号能量,减少信号的振铃现象,提高数据传输的可靠性。

电磁兼容性(EMC)策略则涉及到对高速信号产生的电磁干扰(EMI)的控制。设计时需要遵循相应的EMC设计规范,比如通过布线、PCB布局以及使用屏蔽技术来减少辐射和敏感度,保证设备的正常运行不会受到干扰,同时也不干扰其他设备的正常工作。

接下来的章节将具体讨论HS模式电路设计的硬件选型、布局要点以及电源管理和信号调节策略,这些都是保证高速信号完整性的重要措施。在这些措施的辅助下,I2C HS模式才能在实际应用中充分发挥其高带宽的优势。

# 3. HS模式的电路设计

## 3.1 硬件选择与布局建议

### 3.1.1 高速模式下的I2C芯片选型

选择合适的I2C芯片对于实现高效、稳定的高速模式通信至关重要。高速I2C芯片通常具备高数据吞吐率、低时钟偏差和先进的信号处理能力,以满足HS模式的严格要求。下面是一些

0

0