深入CPU核心:揭秘设计原理与性能指标

发布时间: 2024-12-27 20:23:21 阅读量: 14 订阅数: 11

微机原理与接口技术:手工设计CPU.ppt

# 摘要

CPU作为计算机系统的核心组件,其基础概念、架构设计原理和性能指标直接影响着整个计算平台的效能。本文首先回顾了CPU的基础知识和架构,详细分析了核心设计理念、微架构组成、多核及多线程技术的进步。随后,文章深入解析了CPU性能指标、功耗、散热、扩展性以及兼容性问题。在实际应用优化方面,本文探讨了软件与硬件的协同优化策略以及CPU在服务器、移动设备和游戏领域的应用案例。最后,本文展望了未来CPU技术的发展趋势,包括制程工艺的进步、人工智能与CPU融合的前景,以及可持续计算对CPU设计的新要求。

# 关键字

CPU基础概念;设计原理;性能指标;实际应用优化;技术发展趋势;多核技术;绿色计算

参考资源链接:[(完整word版)计算机组成与系统结构课后答案全(清华大学出版社-袁春风主编).doc](https://wenku.csdn.net/doc/2drb05tvkk?spm=1055.2635.3001.10343)

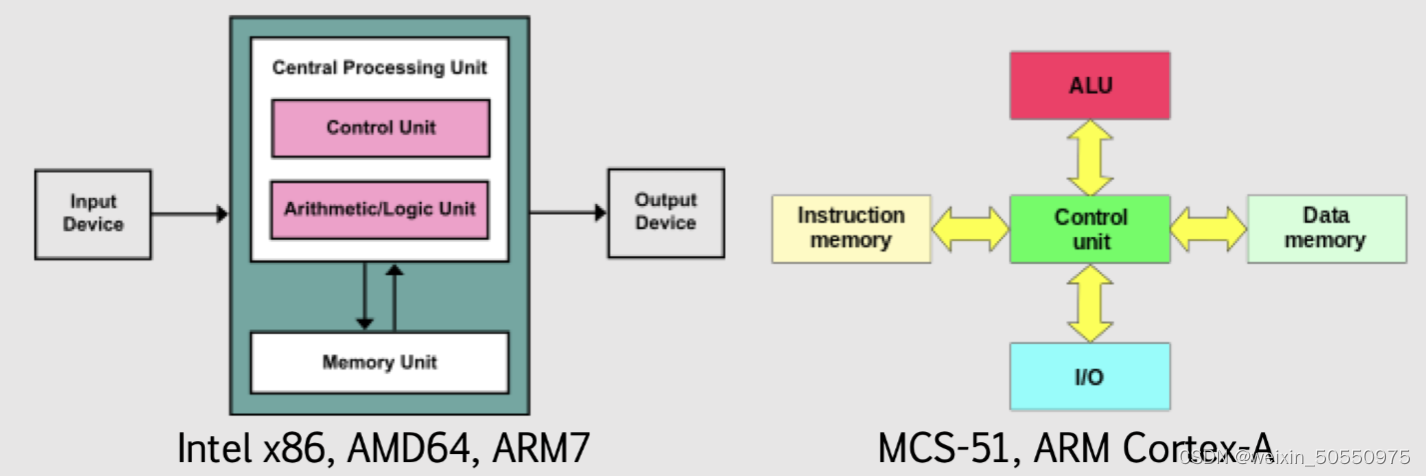

# 1. CPU基础概念与架构

## CPU是什么?

CPU(中央处理器)被称为计算机的大脑,它负责处理、执行指令以及执行计算。无论是在笔记本电脑、台式机、服务器还是移动设备中,CPU都是执行软件程序、提供计算能力的核心组件。了解CPU的工作方式,是优化计算性能和理解新技术发展的前提。

## CPU的基本功能

CPU的基本功能包括数据的读取、处理和存储。其核心功能单元包括算术逻辑单元(ALU)和浮点单元(FPU)用于进行数学运算,缓存系统(L1、L2、L3 Cache)用于快速访问常用数据,以及控制单元管理所有这些组件的工作。每个核心都依赖复杂的控制逻辑,以确保指令能够正确、高效地执行。

## CPU架构的演变

CPU架构已经从简单的单核设计发展到现今的多核处理器。这种演变源于对性能提升的需求以及物理限制(例如发热和功耗)的挑战。现代CPU设计中,多核、超线程技术和先进的指令集架构(ISA)为执行复杂的多任务和高性能计算提供了强大支持。了解架构的发展,有助于把握未来CPU技术的创新方向。

# 2. ```

# 第二章:CPU设计原理

在现代计算机系统中,CPU扮演着至关重要的角色,其设计原理决定着计算性能、能效以及在各种应用场合下的表现。本章将深入探讨CPU的核心设计理念、微架构的组成,以及多核与多线程技术,旨在为读者提供一个全面的理解。

## 2.1 CPU核心的设计理念

CPU的核心设计理念集中体现在其指令集架构(ISA)的选择和流水线技术的实现上,它们共同决定了处理器的性能和兼容性。

### 2.1.1 指令集架构(ISA)的选择与影响

指令集架构是CPU设计中最为基础的概念之一,它定义了处理器能够识别和执行的指令集合。ISA的选择对计算机的性能、功耗、软件生态系统以及硬件实现的复杂度有着深远的影响。

**ISA的分类:**

指令集可以根据其设计哲学分为复杂指令集计算机(CISC)和精简指令集计算机(RISC)两种类型。

- **CISC架构**,如x86架构,采用包含大量复杂指令的设计,可以提供较少的指令完成较多的工作,但可能导致实现复杂、功耗高。

- **RISC架构**,如ARM架构,侧重于通过简单的指令集和统一的指令格式来提升处理速度,减少指令的执行周期数。

**ISA的选择影响:**

选择不同的ISA会影响处理器设计的多个方面:

- **编译器优化**:不同的ISA有不同的设计特点,影响编译器生成更高效代码的能力。

- **硬件复杂度**:ISA复杂度直接影响硬件实现的复杂度和设计成本。

- **性能和功耗**:ISA的设计直接影响CPU的性能和功耗表现。

- **软件生态系统**:不同的ISA有各自的软件支持,包括操作系统、应用程序和开发工具链。

### 2.1.2 流水线技术的演进与优化

流水线技术是现代处理器提高指令执行吞吐率的关键技术。通过将指令执行过程分解为多个阶段,允许在不同阶段并行处理多条指令。

**流水线的工作原理:**

基本的流水线操作分为五个阶段:取指、译码、执行、访存、写回。

- **取指(IF)**:从指令缓存中取出指令。

- **译码(ID)**:对指令进行解析并确定需要的操作数。

- **执行(EX)**:执行指令确定的操作。

- **访存(MEM)**:访问数据存储(可能在执行阶段完成)。

- **写回(WB)**:将结果写回寄存器。

**流水线的优化:**

为了提高流水线的效率,处理器设计者采取了多种优化技术:

- **分支预测**:预测程序分支走向,减少流水线因分支指令造成的空闲。

- **超流水线技术**:通过增加流水线级数来提高每个时钟周期的指令吞吐量。

- **超标量技术**:在一个时钟周期内发射多个指令到多个执行单元。

## 2.2 CPU微架构的组成

CPU微架构是实现指令集架构的具体硬件结构,它涵盖了执行单元、缓存系统和分支预测技术等关键组成部分。

### 2.2.1 执行单元(ALU、FPU)的作用与设计

执行单元是CPU中完成算术和逻辑运算的部分。主要分为算术逻辑单元(ALU)和浮点运算单元(FPU)。

**ALU的设计:**

ALU负责执行整数运算,包括加减乘除、逻辑运算等。设计时会考虑到操作数的来源、结果的写回以及相关的控制逻辑。

```mermaid

flowchart LR

A[fetch instruction] --> B[decode]

B --> C[ALU Operation]

C --> D[write back]

```

**FPU的设计:**

FPU专门用于处理浮点运算,支持科学计算、图形处理等需要高精度计算能力的场景。FPU设计中常使用SIMD技术来提升数据处理的并行度。

### 2.2.2 缓存系统(L1、L2、L3 Cache)的工作原理

缓存系统是CPU内部的一组快速存储单元,用于临时存储频繁访问的数据和指令,减少主存访问延迟。

- **L1缓存**:位于处理器核心内部,访问速度最快但容量最小。

- **L2缓存**:访问速度较快,容量比L1大,可作为L1和L3之间的缓冲。

- **L3缓存**:作为系统缓存,容量更大,为多核心共享。

**缓存的工作机制:**

缓存系统通常采用一种称为“最近最少使用”(LRU)的替换策略,以确保缓存中存储的是最近最有可能再次访问的数据。

### 2.2.3 预取技术和分支预测的实现

预取技术和分支预测技术是现代CPU微架构中提高性能的关键技术。

**预取技术:**

预取是指预测将要访问的数据,并提前从内存中加载到缓存中的过程。这样可以减少处理器等待数据从主存返回的时间。

```mermaid

graph TD

A[检测到访问模式] --> B[预取数据]

B --> C[将数据存储到缓存]

C --> D[处理器请求数据]

D --> E[数据已经缓存,快速读取]

```

**分支预测技术:**

分支预测技术尝试预测程序中条件分支的执行路径,减少因分支指令造成的流水线空闲。现代CPU使用多种高级算法,如两级自适应分支预测算法(TAGE)等,来提高预测的准确性。

## 2.3 多核与多线程技术

随着集成电路技术的发展,多核技术已经成为提高处理器性能的重要手段,而多线程技术则进一步提升了单个核心的效率。

### 2.3.1 多核架构的优势与挑战

多核架构通过将两个或更多的处理器核心集成到单一芯片上,实现了更高的并行处理能力。

**优势:**

- **并行处理能力**:多核架构可以同时处理多个任务,提高系统整体性能。

- **热设计功耗(TDP)管理**:核心可以在低负载时降低功耗,提升能效比。

**挑战:**

- **编程模型**:软件需要支持多线程编程以充分利用多核资源。

- **内存一致性**:多核心间共享内存时,必须维护数据一致性。

### 2.3.2 超线程技术的工作原理与性能提升

超线程(Hyper-Threading)技术是一种允许单个CPU核心同时处理多个线程的技术。

**工作原理:**

超线程技术通过在每个核心内部分离指令执行的资源,实现资源的多线程共享,使得核心可以在等待缓存命中或I/O操作时切换到另一个线程执行。

```mermaid

graph TD

A[指令1] -->|执行| B[核心]

A -->|等待| C[指令2]

B -->|切换| D[指令2]

C -->|执行| B

```

**性能提升:**

超线程技术可以提高CPU的指令吞吐率,特别是在运行多线程或多任务的应用时。对于某些应用程序,这种技术可以提升性能高达30%。

```

在本章中,我们了解了CPU的核心设计理念,包括指令集架构和流水线技术的发展,及其对CPU性能的影响。接着,我们深入探讨了CPU微架构的关键组成,例如执行单元、缓存系统以及预取和分支预测技术。此外,我们还探讨了多核与多线程技术的发展及其在现代CPU设计中的重要性。在下一章,我们将从性能指标的角度,进一步分析CPU的基准测试、功耗、散热、扩展性和兼容性。

# 3. CPU性能指标解析

## 3.1 性能基准测试

### 3.1.1 常用性能测试标准与工具

在现代计算机硬件的发展中,性能基准测试扮演了至关重要的角色。它们为制造商、消费者和企业用户提供了一种衡量和比较不同处理器性能的方法。常用的性能测试标准包括CINEBENCH、PCMark、3DMark、 Geekbench等。这些基准测试涵盖了从图形渲染、系统整体性能、到专业应用等多个方面。

例如,CINEBENCH是一个广泛使用的专业3D渲染性能测试工具,它利用Maxon公司开发的Cinema 4D引擎,来评估CPU在多线程和单线程环境下的性能。而PCMark则侧重于测试计算机在日常任务中的性能表现,诸如网页浏览、视频会议和文档编辑等。

这些工具不仅提供了分数指标,还提供了详细的子系统测试结果,帮助用户深入理解处理器的性能瓶颈,比如在内存访问速度、缓存效率或是特定指令集的执行效率等方面。

```mermaid

graph LR

A[开始测试] --> B[选择基准测试工具]

B --> C[运行标准测试]

C --> D[收集性能数据]

D --> E[生成性能报告]

E --> F[分析性能结果]

F --> G[对比同级别处理器]

```

### 3.1.2 性能指标的解读与对比

性能指标的解读需要结合实际应用场景,因为不同的应用场景会对CPU提出不同的性能需求。例如,在图形设计和视频编辑中,多核和多线程处理能力较为重要;而在科学计算中,单核的浮点运算能力可能更关键。

在对比处理器时,我们不仅仅看分数的高低,还需要分析测试过程中CPU的温度表现、功耗以及在高负载下的稳定性。有时候,高分背后可能是CPU在极限频率下运行,这会导致过高的功耗和发热,长期来看并不利于系统的稳定性和硬件的使用寿命。

## 3.2 功耗与散热

### 3.2.1 功耗管理技术(如Intel的睿频技术)

随着处理器性能的提升,其功耗也相应增加,功耗管理技术因此成为了CPU设计中的一个重要方面。以Intel为例,其睿频技术(Turbo Boost)是一种能够动态调节CPU核心频率的技术。当处理器处于负载较低的情况时,睿频技术可以将部分核心的频率提高,从而提供更好的单线程性能;反之,在多线程负载重时,它又能降低单个核心的频率,以保证功耗不超标,保持散热在可控范围内。

睿频技术的实现依赖于对CPU各个核心和整个芯片的功耗监测。监测系统会实时反馈核心的温度和功耗数据给CPU,以供决策何时开启或关闭睿频。

### 3.2.2 散热解决方案的演变与创新

散热方案的改进与创新也是提升CPU性能的关键。传统的散热方法包括被动散热和主动散热两种形式。随着技术的发展,更多创新的散热技术被引入,例如液态散热、相变冷却等。

液态散热利用了液体的高热导率特性,通过液体循环带走CPU产生的热量。相变冷却则是指通过物质状态改变来吸收热量的冷却方法,例如使用氟利昂等物质在气态和液态之间循环变化时吸收热量。

这些创新的散热技术为高性能CPU提供了更好的散热保障,使得在不增加功耗的前提下提升性能成为可能。

## 3.3 CPU的扩展性与兼容性

### 3.3.1 主板与CPU的兼容性问题

CPU与主板的兼容性问题在选购时至关重要,不匹配可能导致无法安装或者硬件性能不能完全发挥。主板的设计需要考虑到CPU的插槽类型、供电需求、以及特定的芯片组支持等。例如,Intel的LGA 1151插槽的主板就只能兼容特定的Core系列CPU。

要解决兼容性问题,首先需要查看CPU制造商提供的官方兼容性列表,同时也要确认主板的BIOS版本是否支持最新的CPU。有时候,即使是同一系列的CPU,不同代的产品也可能存在不兼容的风险,尤其是在新一代产品发布初期。

### 3.3.2 芯片组与接口技术的升级

芯片组是主板上的一块关键集成电路,负责连接CPU、内存、存储设备及其他周边设备。随着新的CPU架构推出,芯片组也需要进行相应的升级以支持新的技术和功能。例如,从DDR4到DDR5的内存接口技术升级,就需要芯片组提供对应的支持。

在接口技术方面,高速数据传输的需求推动了PCI Express(PCIe)标准的不断演进。从PCIe 3.0到PCIe 4.0,再到未来可能的PCIe 5.0,更高的带宽支持使得CPU能够更高效地与高速存储设备、图形卡和网络接口等外设进行数据交换。

总结而言,CPU的性能指标解析不仅仅是理论上的数字对比,而是一个复杂的分析过程,需要结合基准测试工具、功耗与散热的平衡,以及CPU的扩展性和兼容性等实际应用场景。只有全面地理解和评估这些因素,才能对CPU的性能有一个完整的认识。

# 4. CPU在实际应用中的优化

## 4.1 软件与硬件的协同优化

### 4.1.1 编译器优化与CPU指令集的关系

编译器作为连接软件与硬件的重要桥梁,其对CPU指令集的优化策略直接影响程序的运行效率。在编译过程中,编译器通过分析源代码,将其转化为机器代码,这个过程中编译器会根据目标CPU的指令集特性进行优化。

例如,现代编译器通常会支持内联汇编,允许直接插入特定的CPU指令,或者针对特定的处理器特性进行代码调度,以减少指令流水线的空泡现象。高级的编译器还支持自动向量化,它可以将循环中的数据操作转换为利用SIMD(Single Instruction, Multiple Data)指令集的并行操作,从而充分利用现代CPU的宽执行单元。

通过使用编译器的高级优化选项,比如GCC的`-O3`或`-Ofast`,编译器会尝试更多的优化策略来提高程序性能。但这些优化策略在不同的CPU架构上效果是不同的,因此开发者需要仔细测试以确定最佳的编译器配置。

下面是一个简单的代码示例,展示了如何利用GCC编译器进行基本的优化:

```c

// example.c

#include <stdio.h>

void calculate(int *arr, int size) {

for (int i = 0; i < size; i++) {

arr[i] *= 2;

}

}

int main() {

int size = 10000;

int arr[size];

for (int i = 0; i < size; i++) {

arr[i] = i;

}

calculate(arr, size);

return 0;

}

```

编译该程序并启用优化:

```bash

gcc -O2 example.c -o example

```

在这个例子中,`-O2`参数将启用GCC的二级优化策略,这些策略会包括函数内联、循环展开、指令调度等。

优化效果需要通过实际运行程序并利用性能分析工具(如`perf`、`gprof`)来评估。性能分析结果可能会显示出因编译器优化而带来的指令执行时间减少和缓存命中率提升等积极影响。

### 4.1.2 操作系统调度对CPU性能的影响

操作系统作为资源分配的管理者,其调度策略对CPU性能有着深远的影响。操作系统调度器负责决定哪个进程或线程获得CPU时间片,以实现系统的多任务并行处理。

例如,在Linux系统中,调度器可以基于进程优先级、CPU负载、进程历史执行时间等因素来分配CPU时间。调度器中的一些特性如CFS(Completely Fair Scheduler)确保了不同进程获得公平的CPU时间分配,而实时调度器则允许满足实时性要求的进程获得更高的调度优先级。

在现代多核CPU系统中,操作系统调度器还会考虑CPU亲和性(affinity)来提高缓存的利用效率。通过将进程绑定到特定的CPU核心,可以减少缓存失效和内存访问延迟,从而提高性能。

操作系统调度器的一个关键优化示例是对多线程应用程序的支持。通过合理地分配线程到不同的核心,操作系统可以最大化利用多核CPU的计算资源,避免因线程争抢同一个核心而造成的性能瓶颈。

为了实现这些调度优化,操作系统开发者通常会使用内核参数或者API来调整调度行为。例如,Linux提供了`sched_setscheduler`系统调用来设置特定进程的调度策略和优先级。

```c

// 设置进程调度策略和优先级的示例代码

#include <stdio.h>

#include <sched.h>

int main() {

struct sched_param param;

int max_priority;

// 获取最高实时优先级

max_priority = sched_get_priority_max(SCHED_FIFO);

// 设置调度参数

param.sched_priority = max_priority;

// 设置调度策略为FIFO,并赋予最高优先级

if (sched_setscheduler(0, SCHED_FIFO, ¶m) == -1) {

perror("sched_setscheduler");

}

// ... 进程主代码 ...

return 0;

}

```

这段代码将当前进程的调度策略设置为FIFO(先进先出),并且赋予了最高实时优先级,这意味着该进程将尽可能获得CPU时间。

通过理解和应用操作系统调度器的特性,开发者可以更高效地利用CPU资源,优化应用性能。系统性能分析工具如`top`、`htop`、`mpstat`等可用于监控系统调度和资源使用情况,帮助开发者发现并解决可能的性能瓶颈。

# 5. 未来CPU技术的发展趋势

随着技术的不断进步,CPU的发展也在不断向前推进。未来的CPU将不仅仅是一个简单的处理器,而是会变得更加智能、高效,并且更加注重可持续性。在本章中,我们将探讨未来CPU技术的几个发展趋势,以及这些趋势对IT行业可能产生的影响。

## 5.1 制程工艺的进步与挑战

### 5.1.1 从硅到新材料的探索与应用前景

随着摩尔定律的推进,传统的硅材料在接近物理极限,研究人员和工程师正在探索其他新材料以推动制程工艺的进步。例如,使用石墨烯、氮化镓等材料,这些新材料具有更好的电导性和热导性,可能在未来替代硅成为主流半导体材料。

```mermaid

graph LR

A[硅技术] --> B[石墨烯]

A --> C[氮化镓]

B --> D[更高的电导性和热导性]

C --> E[更宽的能带间隙]

D --> F[提升计算性能]

E --> G[降低功耗]

```

### 5.1.2 量子计算对传统CPU技术的冲击

量子计算的崛起预示着传统CPU技术将面临巨大的变革。量子比特的并行性和叠加态使得量子计算机在处理某些特定问题时,比传统CPU快上数百万倍。量子计算的发展可能会促使CPU技术朝着与量子计算相结合的方向发展,以便在处理复杂计算任务时获得显著的性能提升。

## 5.2 人工智能与CPU的融合

### 5.2.1 AI专用加速器与传统CPU的互补

为了适应人工智能计算的需求,许多公司开始在传统CPU中整合AI专用加速器。这些加速器针对深度学习算法进行优化,可以显著提高特定AI任务的执行效率。未来的CPU可能会更多地融合这种专用硬件,与传统计算单元相辅相成,形成更加强大的计算平台。

### 5.2.2 深度学习对CPU架构的影响

深度学习算法对数据处理有很高的要求,因此推动了CPU架构向更高的并行性和更大的内存带宽发展。现代CPU开始增加更多的计算核心,并优化内存层级和缓存结构,以适应深度学习工作负载。这一变化不仅对CPU设计产生影响,也对编程模型和算法设计提出了新的要求。

## 5.3 可持续计算与CPU设计

### 5.3.1 绿色计算对CPU性能与效率的要求

随着全球对环保意识的增强,绿色计算成为CPU设计的重要考量因素。未来的CPU将需要在保持高性能的同时,尽可能降低能耗。这要求CPU架构不仅要高效,还要能够在低功耗状态下运行。为此,可能会采用更多节能技术和智能功耗管理策略。

### 5.3.2 可持续计算在未来CPU设计中的角色

可持续计算不仅仅是关于节能,还涉及到设备的整个生命周期,从生产、使用到回收的每一个环节。CPU设计在未来可能更多地考虑材料的可回收性、生产过程的碳足迹以及设备的耐用性。这意味着CPU的设计将是一个综合考量性能、效率和环境影响的多维度过程。

在总结本章内容之前,我们可以看到,未来CPU技术的发展将受到新材料、AI技术以及可持续计算等因素的深远影响。这些发展趋势预示着CPU将从单一的处理器角色,进化为更为复杂和多功能的计算平台,以应对日新月异的技术挑战和应用需求。而IT行业从业者需要紧跟这些趋势,为未来的变化做好准备。

0

0