存储系统的未来:PCI Express 3.0应用研究与实战技巧

发布时间: 2024-12-21 13:36:40 阅读量: 2 订阅数: 3

# 摘要

PCI Express 3.0作为一种高速串行计算机扩展总线标准,已经成为现代计算机系统不可或缺的组成部分。本文从技术概述开始,详细介绍了PCI Express 3.0的硬件基础,包括其物理结构、信号协议及电源管理机制。随后深入探讨了PCI Express 3.0在软件开发方面的基础,配置空间操作及性能调优方法。通过实战应用案例分析,本文展示了PCI Express 3.0在高性能计算、虚拟化环境和高速网络中的关键应用和优化方法。最后,本文展望了PCI Express技术的未来发展,分析了新的发展趋势,面临的挑战以及应对策略,并提供了最佳实践和资源推荐。整体而言,本文为读者提供了一个全面了解和应用PCI Express 3.0的蓝图。

# 关键字

PCI Express 3.0;硬件基础;软件开发;性能调优;实战应用案例;技术发展趋势

参考资源链接:[PCI Express技术详解:3.0版](https://wenku.csdn.net/doc/3z3m7dyw3h?spm=1055.2635.3001.10343)

# 1. PCI Express 3.0技术概述

PCI Express 3.0是一种高速串行计算机扩展总线标准,是 PCI Express (PCIe) 第二代技术的延续。它在保持原有PCIe架构的基础上,将带宽翻倍至8 GT/s (Gigatransfers per second),每通道的理论传输速率可达约1 GB/s(双工)。这种技术广泛应用于现代计算机系统中,特别是在需要高数据传输速率的场景,如图形处理、数据存储以及网络通信领域。

PCI Express 3.0的推出,不仅提升了单通道传输速率,而且还通过改善信号的电气特性来降低功耗,使得设备在维持高性能的同时也具备良好的能效比。此外,它还支持诸如精确时间测量(Precision Time Measurement)等新功能,以满足特定应用领域的需求。

接下来的章节,我们将深入探讨PCI Express 3.0的硬件基础、软件开发、实战应用案例以及未来发展趋势,为读者提供全面的技术剖析和实用建议。

# 2. PCI Express 3.0硬件基础

在深入探讨PCI Express 3.0的硬件基础之前,了解其物理结构、信号协议以及电源管理机制是至关重要的。这些基础知识为PCIe技术的实践应用与性能优化提供了理论支撑和实施指导。

## 2.1 PCI Express 3.0的物理结构

### 2.1.1 PCIe卡的形态和尺寸

PCI Express插槽与卡(通常称为PCIe卡或卡)是PCI Express技术实现的核心组件。在PCIe的多个版本中,定义了不同的卡形态和尺寸,以满足不同应用需求。

- **形状和尺寸**:PCIe卡有多种形状,包括全高、半高以及全高全长、半高半长。这些卡的尺寸定义了它们占用的空间和散热需求。

- **卡类型**:例如,PCIe x16卡主要用于图形处理器,而x1卡则常用于小型网络或声卡。不同类型的PCIe卡在带宽和性能上有所不同,适应不同的应用场景。

下面表格展示了常见的PCIe卡类型和它们的属性:

| 类型 | 描述 | 带宽(单向) | 应用场景 |

| --- | --- | --- | --- |

| PCIe x1 | 单通道,低带宽 | 250 MB/s | 声卡、网卡等 |

| PCIe x4 | 四通道,中等带宽 | 1 GB/s | 固态硬盘、高速网卡 |

| PCIe x8 | 八通道,较高带宽 | 2 GB/s | 存储加速、专业图形 |

| PCIe x16 | 十六通道,高带宽 | 4 GB/s(3.0规范) | 图形处理、高性能计算 |

了解PCIe卡的这些属性对于在特定硬件环境中选择合适的PCIe卡至关重要,以确保达到最优性能。

### 2.1.2 连接器和接口类型

PCI Express连接器的设计使得其能够适用于多种类型的设备。随着PCIe技术的发展,接口类型也逐渐增多,例如常见的有:

- **PCIe插槽**:安装在主板上的PCIe插槽用来容纳相应的PCIe卡。插槽的版本与卡的版本必须匹配。

- **M.2接口**:一种小型化接口,常见于笔记本电脑和紧凑型PC,支持M.2规格的SSD和Wi-Fi模块等。

- **U.2接口**:用于连接SSD的接口,支持多种标准的SSD,如SATA和PCIe。

不同接口类型的PCIe卡在安装和使用上有差异,但都遵循PCIe规范。例如,M.2 SSD若采用PCIe通道,则使用NVMe(非易失性内存快速路径)接口标准,以充分利用PCIe通道的高速数据传输能力。

## 2.2 PCI Express 3.0的信号和协议

### 2.2.1 信号传输的电气特性

PCI Express 3.0在信号传输方面有一些独特的电气特性。PCIe 3.0的传输速率为8 GT/s(千兆传输每秒),这意味着每个通道可以实现大约1 GB/s的单向带宽。信号传输的电气特性包括电压、阻抗、信号完整性和时序等要求。

- **信号传输电压**:标准电压是0.8伏特,使用低压差分信号(LVDS)技术进行传输。

- **阻抗匹配**:为了确保信号质量,传输线路的阻抗必须严格匹配,通常使用100欧姆的差分阻抗。

- **信号完整性**:为了保证信号的完整性,需要使用高质量的PCB板,并采取特定的布线策略。此外,使用终端匹配和均衡器可以减少信号的损耗和干扰。

### 2.2.2 协议栈和数据传输过程

PCI Express采用分层的协议栈结构,主要包括事务层、数据链路层和物理层。数据在PCIe协议栈中传输的过程如下:

- **事务层**:负责定义数据传输的协议和包格式,比如读写请求。

- **数据链路层**:确保数据的可靠传输,通过序列号和CRC校验来检测和纠正错误。

- **物理层**:负责将数据包转换为能够在物理介质上传输的信号。

数据包在事务层被封装成事务层包(TLP),然后经过数据链路层封装成数据链路层包(DLLP),最后在物理层转换成在物理介质上传输的比特流。

```

+-----------------+

| Application |

+-----------------+

|

+-----------------+

| Operating |

| System |

+-----------------+

|

+-----------------+ +-----------------+

| Device Driver | -> | Firmware | -> Hardware

+-----------------+ +-----------------+

| | |

+-----------------+ +-----------------+ +-----------------+

| Transaction | | Data Link | | Physical |

| Layer | | Layer | | Layer |

+-----------------+ +-----------------+ +-----------------+

```

通过上述的协议栈,PCIe实现了一套高效、可靠的数据传输机制。理解这个过程对于调试和优化系统性能至关重要。

## 2.3 PCI Express 3.0的电源管理

### 2.3.1 电源管理机制

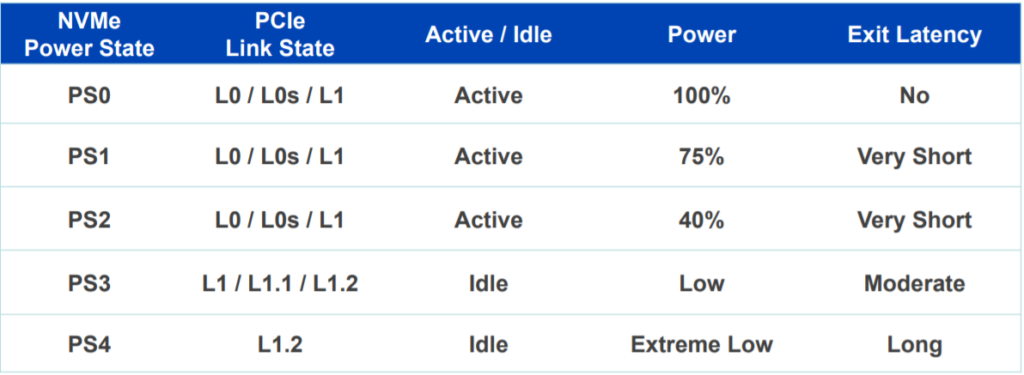

PCI Express规范定义了电源管理机制,以保证PCIe设备在低能耗状态下仍能维持通信。这一机制通常依赖于以下特性:

- **低功耗状态**:PCIe设备能够进入几种低功耗状态,例如L0s和L1等状态,以降低功耗。

- **主动状态电源管理(ASPM)**:这是一种动态电源管理技术,它能够在不需要数据传输时减少设备的功耗。

### 2.3.2

0

0