逻辑综合与芯片设计:专家解析面临的挑战与解决方案

发布时间: 2025-01-03 01:38:39 阅读量: 4 订阅数: 12

AIMP2 .NET 互操作插件

# 摘要

随着技术进步,芯片设计正面临前所未有的挑战,尤其是在逻辑综合过程中对复杂性、时序和功耗的控制。本文概述了芯片设计的基本原理和所面临的挑战,重点分析了逻辑优化技术、时序约束以及针对技术节点缩小、电源与信号完整性以及特定应用需求的创新解决方案。文章还展望了芯片设计的未来,探讨了人工智能、可持续设计以及持续集成和部署(CI/CD)在提升设计效率和性能方面的潜力。最终,本文为芯片设计领域的研发人员和工程师提供了深入的技术见解与未来发展方向。

# 关键字

逻辑综合;芯片设计;时序优化;电源管理;可持续设计;AI设计自动化

参考资源链接:[逻辑综合流程详解:从RTL代码到门级网表](https://wenku.csdn.net/doc/7n4afhgnzt?spm=1055.2635.3001.10343)

# 1. 逻辑综合与芯片设计概述

## 1.1 芯片设计的重要性与目标

芯片设计是现代电子技术的基石,它关乎到电子产品的性能、效率和可靠性。芯片设计旨在将复杂的电路逻辑转化为实际的硬件产品。其核心目标是将系统功能从抽象的算法和协议转变为可制造、测试和可靠运行的物理集成电路。芯片的性能直接影响到整个电子设备的运行效率和稳定性,因此芯片设计的复杂性和精确性要求日益增高。

## 1.2 逻辑综合在芯片设计中的角色

逻辑综合是将高层次的描述(如硬件描述语言HDL)转换为低层次、可制造的门级网表的过程。这一过程对于芯片设计至关重要,因为它直接影响到芯片的最终性能、功耗和面积。在逻辑综合中,工程师需要对设计进行优化,以满足时序、面积和功耗等多方面的约束,确保最终产品能够在现实条件下高效运行。逻辑综合不仅涉及算法的运用,还涉及电路设计的策略选择和权衡,它是连接抽象设计与物理实现的关键桥梁。

# 2. 芯片设计中的逻辑综合原理

### 2.1 逻辑综合的基本概念

逻辑综合是一种将高层次的抽象设计转换为低层次实现的技术,它在数字集成电路设计流程中扮演关键角色。逻辑综合将硬件描述语言(HDL)编写的算法或功能描述转换为门级网表,这是实现芯片制造前的最后一个步骤。

#### 2.1.1 逻辑综合的目的和作用

逻辑综合的目的是将设计人员通过HDL(比如Verilog或VHDL)编写的抽象功能描述转化为可以在芯片上实现的具体物理结构。逻辑综合过程涉及将高级的逻辑表达式转换为门级逻辑结构。通过这样的转换,设计可以评估并优化面积、功耗和性能等关键参数。

逻辑综合的作用还在于它能显著地影响最终芯片的性能。它能够:

- 降低逻辑门的数量,从而减少芯片面积。

- 优化时序,提高电路的运行频率。

- 优化功耗,延长设备的电池寿命。

#### 2.1.2 逻辑综合的数学模型和算法基础

逻辑综合通常依赖于布尔代数和图论中的一些算法。布尔代数允许综合工具进行逻辑优化,而图论则用于分析电路的拓扑结构。在这个过程中,图的节点代表逻辑门,边代表连接信号。

例如,使用卡诺图(Karnaugh Map)可以简化布尔函数,减少逻辑表达式的复杂度。再比如,算法如Quine-McCluskey或Espresso算法用于逻辑优化,以寻找更简化的逻辑表达式。此外,启发式搜索算法用于解决复杂的优化问题,如A*或遗传算法,它们通过不断迭代选择和交叉生成更好的解。

### 2.2 逻辑优化技术

#### 2.2.1 逻辑优化的目标和方法

逻辑优化旨在改进设计在面积、速度和功耗等方面的性能。优化的目标包括最小化逻辑门的数量、缩短关键路径长度、以及减少功耗。

逻辑优化的主要方法包括:

- 删除冗余逻辑,减少不必要的门。

- 逻辑等价变换,使用更简单的逻辑结构替换复杂结构。

- 重新映射技术,优化逻辑门之间的连接,减少延时。

#### 2.2.2 逻辑等价变换和映射优化

逻辑等价变换是指在保持逻辑功能不变的前提下,通过数学变换简化逻辑表达式。这包括布尔最小化、代数简化等技术。例如,德摩根定律可用来将复杂的AND-OR逻辑结构简化为更简单的结构。

映射优化通常涉及到将HDL描述的逻辑映射到实际可用的硬件模块,如查找表(LUT)和基本逻辑门。综合工具会尝试找出最佳的映射方案,以满足时序和面积等约束条件。

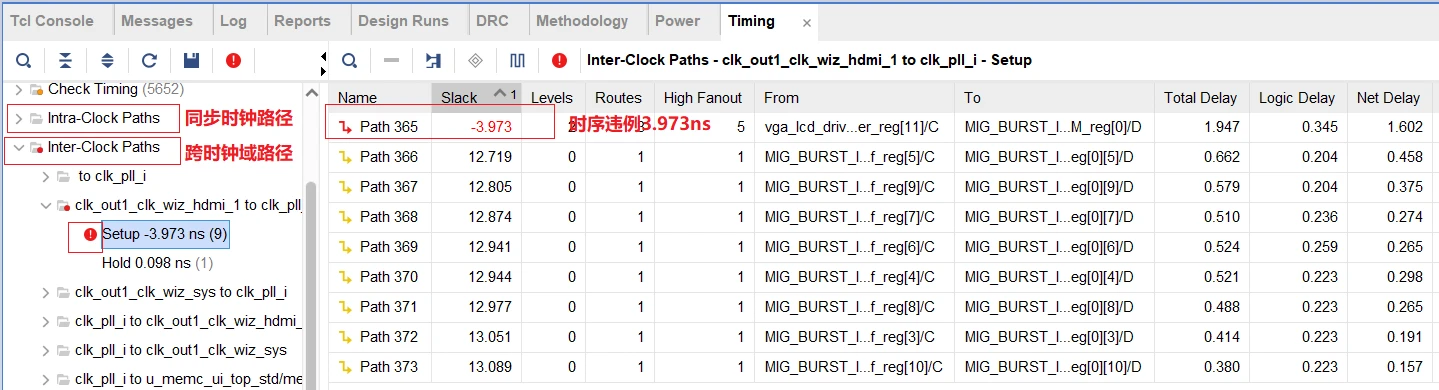

### 2.3 时序约束与优化

#### 2.3.1 时序约束的概念和重要性

时序约束是指对设计中的信号路径进行定义和限制,以确保在一定的时钟频率下电路能够正确运行。时序约束主要描述了寄存器之间的信号传输时间,以及信号必须满足的最小和最大延迟。

时序约束的重要性在于确保设计的稳定性和可预测性。没有严格的时序约束,即使逻辑设计在功能上是正确的,电路也可能无法按预期的速度稳定工作。时序问题通常在物理设计阶段被识别,但逻辑综合阶段就进行优化可以显著减少后续调整的复杂性和工作量。

#### 2.3.2 时序优化策略和工具

时序优化涉及调整逻辑结构和门级布局,以满足设计的时序要求。常用的时序优化策略包括:

- 重新排列逻辑顺序,减少关键路径的延迟。

- 使用pipelining技术,在数据路径中插入额外的寄存器以改善时序。

- 提高电路中的并行度,同时保持时序约束的满足。

时序优化工具如STA(静态时序分析)工具会分析电路的时序信息,提供报告指出违反时序要求的部分,帮助工程师进行优化。

下面是一个示例代码块,展示了一个简单的时序约束的例子以及对应的代码解释和参数说明。

```tcl

# 时序约束示例

set_max_delay -from [get_ports clk] -to [get_ports data_out] 10

```

在这个示例中,`set_max_delay` 命令用于设置从 `clk` 端口到 `data_out` 端口的最大延时。这个约束确保了信号路径在10纳秒内完成传输。这是保证数据及时到达接收寄存器的重要步骤,防止了数据丢失或错误。

逻辑综合与芯片设计是高度技术化的领域,涉及到大量的理论知识和实际操作。在本小节中,我们详细探讨了逻辑综合的基本概念、逻辑优化技术和时序约束与优化的策略。在后续章节中,我们将继续深入这些主题,同时探讨芯片设计面临的挑战以及应对这些挑战的解决方案。

# 3. 芯片设计面临的主要挑战

在当今高度发展的科技时代,芯片设计领域不断推陈出新,层出不穷的创新技术使得芯片的设计与制造面临前所未有的挑战。本章将详细探讨芯片设计过程中遇到的主要挑战,分析其背后的技术动因,并针对每一项挑战提出可能的解决方案。

## 3.1 技术节点缩小带来的问题

随着摩尔定律的不断推演,芯片的设计已经到达了纳米甚至更小的技术节点。这样的进步虽然为高性能计算、移动设备等提供了强大的推动力,但同时也带来了一系列设计和制造上的挑战。

### 3.1.1 制造

0

0