逻辑综合中的约束管理:精确控制设计输出的终极指南

发布时间: 2025-01-03 01:47:10 阅读量: 5 订阅数: 12

AIMP2 .NET 互操作插件

# 摘要

约束管理在现代电子设计自动化(EDA)领域扮演着核心角色,对于确保设计质量和提升设计效率至关重要。本文系统性地分析了约束管理的基本概念及其在逻辑综合中的应用,探讨了时序约束、设计约束以及约束冲突的诊断和解决策略。此外,本文详细介绍了当前约束管理工具和技术,并通过案例分析提供了最佳实践。文章最后讨论了约束管理的未来趋势,包括新兴技术的影响以及应对未来挑战的策略。本文旨在为设计工程师和项目管理者提供深入的洞见,帮助他们在复杂的设计环境中更有效地运用约束管理,以推动技术进步和创新。

# 关键字

约束管理;逻辑综合;时序约束;设计冲突;自动化工具;最佳实践

参考资源链接:[逻辑综合流程详解:从RTL代码到门级网表](https://wenku.csdn.net/doc/7n4afhgnzt?spm=1055.2635.3001.10343)

# 1. 约束管理的基本概念和重要性

## 1.1 约束管理的定义

约束管理是电子设计自动化(EDA)领域的重要组成部分,它涉及到在设计过程中对资源使用、性能指标和设计实现施加一系列规则和限制。这些约束确保设计按照既定参数,满足功能、时序和物理实现的要求,是成功设计的关键。

## 1.2 约束管理的重要性

有效的约束管理能够引导设计朝着预期目标发展,减少设计迭代次数,缩短产品上市时间。它在优化电路性能,保证设计可靠性,以及降低设计复杂性方面发挥着至关重要的作用。

## 1.3 约束与现代设计流程

随着设计复杂性的增加,约束管理越来越依赖于自动化工具,以便更有效地处理大量数据和复杂的约束关系。在未来,随着新技术的发展,如人工智能和机器学习,约束管理有望实现更加智能化的管理和预测性维护。

# 2. 逻辑综合中的约束类型及应用

## 2.1 时序约束的定义与设置

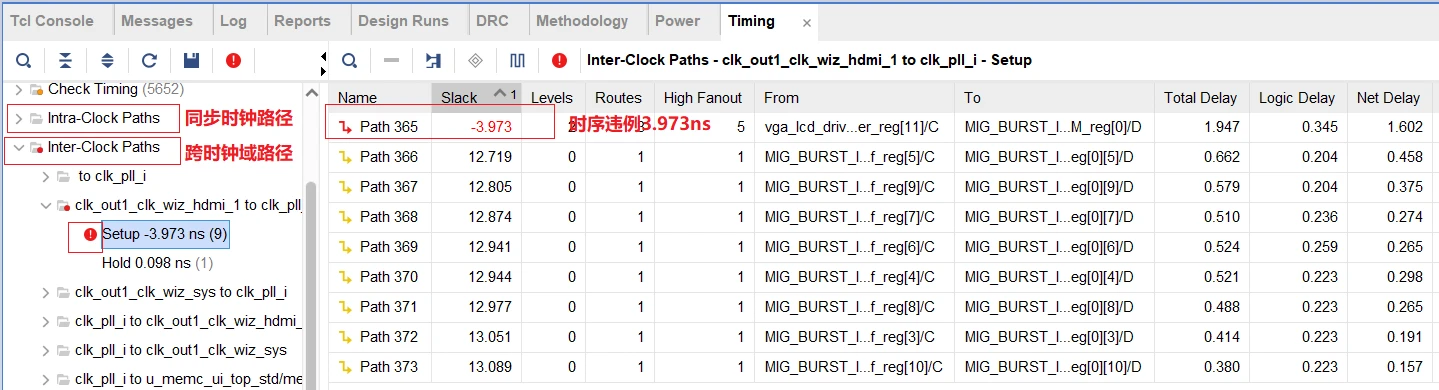

### 2.1.1 时钟域和时钟域交叉

时钟域交叉(CDC, Clock Domain Crossing)是指在数字电路中,来自两个或多个不同时钟域的信号进行交互时产生的问题。由于时钟域之间存在不确定的相位关系,这可能导致信号在采样时出现亚稳态,进而引发数据丢失、数据错误甚至系统崩溃。

在设计阶段,我们需要明确识别所有时钟域并设置适当的约束,以确保信号在时钟域间正确传递。这通常包括指定时钟域之间的同步机制,例如使用双触发器或同步器链来防止亚稳态的出现。

```verilog

// 示例代码:时钟域交叉的同步器

module CDC_Synchronizer(

input wire clk_A, // 来自时钟域A的信号

input wire clk_B, // 时钟域B的同步时钟信号

input wire signal, // 时钟域A的信号

output reg signal_sync // 同步到时钟域B的信号

);

reg [1:0] sync_reg; // 使用两位触发器进行同步

always @(posedge clk_B) begin

sync_reg[0] <= signal; // 第一个上升沿捕获信号

sync_reg[1] <= sync_reg[0]; // 第二个上升沿传递信号

end

assign signal_sync = sync_reg[1]; // 输出同步信号

endmodule

```

在上述代码中,我们使用了两个D型触发器对信号进行同步。这个过程确保了信号从`clk_A`域到`clk_B`域的正确同步。

### 2.1.2 输入/输出延迟约束

输入/输出延迟约束是为了保证信号在芯片的输入/输出引脚和内部逻辑之间能够满足时序要求。这包括对信号的建立时间(setup time)和保持时间(hold time)进行约束。

```sdc

# 输入延迟约束示例

set_input_delay -max -clock clk [get_ports {data_in}] 2.0

set_input_delay -min -clock clk [get_ports {data_in}] 1.0

# 输出延迟约束示例

set_output_delay -max -clock clk [get_ports {data_out}] 2.5

set_output_delay -min -clock clk [get_ports {data_out}] 0.5

```

在上面的SDC(Synopsys Design Constraints)脚本中,我们使用`set_input_delay`和`set_output_delay`命令来指定输入和输出的延迟约束。这样可以确保信号在正确的时钟周期内稳定,并在时序分析中满足时序要求。

### 2.1.3 管脚分配与布局约束

管脚分配和布局约束对于物理层面的电路板或芯片设计至关重要。这包括了芯片或电路板上的物理位置安排,以保证信号能够以最小的延迟和干扰进行传输。

```sdc

# 管脚分配约束示例

set_location_assignment PIN_10 -to [get_ports {clk}]

set_location_assignment PIN_11 -to [get_ports {reset}]

```

上述SDC命令用于为特定的信号指定位在芯片或电路板的特定引脚上。这种约束对于满足时钟信号和复位信号的特定要求非常关键。

## 2.2 设计约束的制定与实现

### 2.2.1 功能约束的基本原则

功能约束是描述硬件描述语言(HDL)设计的行为约束,以确保设计满足预期的功能规范。这些约束可能包括设置逻辑门、触发器的初始状态等。

```verilog

// 功能约束示例

initial begin

reg a = 1'b0; // 定义寄存器a并初始化为0

reg b = 1'b1; // 定义寄存器b并初始化为1

// 表达式和行为描述

c = a & b; // c的值为a和b的与结果

end

```

在该代码段中,`initial`块用来在仿真的开始设置信号的初始状态,以满足功能上的特定要求。

### 2.2.2 面向功耗的约束条件

在现代电子设计中,功耗已经成为一个重要的约束条件。设计时需要考虑诸如时钟门控、动态电压调节和多电压域设计等技术来降低功耗。

```sdc

# 功耗约束示例

set_dont_touch_network [get_ports {clk}]

set_dont_touch_network [get_ports {reset}]

```

通过SDC命令`set_dont_touch_network`,可以指定某些网络(信号线)不进行优化以减少功耗,如上面的时钟和复位信号。

### 2.2.3 资源和面积的约束考量

资源和面积的约束通常涉及到芯片上的逻辑单元、存储器块或引脚数量的限制。在FPGA设计中,这些约束尤为重要,因为FPGA的资源是有限的。

```sdc

# 面积约束示例

create_pblock pb1

set_pblock_range -add {X4 Y4 X10 Y10}

set_fp_property -name core_utilization 80 [get_pblocks pb1]

```

在该SDC示例中,我们定义了一个位置限制区域`pblock`,并设置了一个面积利用率上限,以此来控制FPGA内部资源的分配。

## 2.3 约束冲突的诊断与解决

### 2.3.1 常见约束冲突案例

在逻辑综合和布局布线阶段,常见约束冲突案例包括时序约束与实际布局的不匹配、资源限制导致的逻辑无法映射,以及功耗约束与性能要求的冲突。

### 2.3.2 解决约束冲突的策略

解决约束冲突需要综合考虑设计的各个方面,包括修改设计逻辑、调整时序预算、优化资源分配,以及重新评估和修改功耗约束。

```sdc

# 解决冲突的策略示例

remove_clock {

```

0

0