【提高FFT实时处理能力】:FPGA算法优化的实践指南

发布时间: 2025-01-05 20:23:20 阅读量: 13 订阅数: 18

verilog流水线256点fft算法

# 摘要

快速傅里叶变换(FFT)是一种高效计算离散傅里叶变换(DFT)及其逆变换的算法,对于信号处理和数据分析至关重要。随着技术的发展,现场可编程门阵列(FPGA)因其灵活性和高性能并行处理能力成为FFT实现的理想选择。本文首先介绍了FFT的基础知识和重要性,然后深入探讨了FPGA在FFT处理中的应用理论,包括硬件描述语言(HDL)的基础知识以及FPGA并行处理FFT的优势与挑战。接着,文章详细描述了FPGA上FFT算法的设计与优化实践,强调了数据流和控制流的设计,以及管线化、并行化技术和数值精度权衡的重要性。此外,本文还分析了FFT在高性能计算、通信系统和视频处理等特定领域的优化案例,并探讨了未来发展趋势,包括新兴技术对FFT优化的影响,以及硬件发展和软硬件协同设计所面临的挑战与可能的解决策略。

# 关键字

快速傅里叶变换(FFT);现场可编程门阵列(FPGA);硬件描述语言(HDL);并行处理;算法优化;软硬件协同设计

参考资源链接:[FPGA实现的高效基4-FFT算法与1024点设计详解](https://wenku.csdn.net/doc/nxk0qryhch?spm=1055.2635.3001.10343)

# 1. 快速傅里叶变换(FFT)基础与重要性

## 1.1 FFT的基本概念

快速傅里叶变换(FFT)是数字信号处理(DSP)中的核心算法之一,它是离散傅里叶变换(DFT)的高效算法实现。FFT通过减少计算量,使得从时域到频域的转换更加迅速,对于处理大规模数据集至关重要。

## 1.2 FFT的应用场景

FFT在信号处理、图像分析、音频处理以及生物信息学等多个领域有着广泛应用。由于其高效性,FFT成为分析和处理信号频域特性的首选工具。

## 1.3 FFT的重要性

在处理实时性要求极高的应用中,比如雷达信号处理、无线通信等,FFT的重要性尤为突出。它不仅提高了信号处理速度,而且降低了设备成本,使得高性能计算成为可能。

FFT算法将信号的时域分析转换为频域分析,从而简化了对信号特征的识别和处理。它在多领域的广泛应用也反映了其在数字信号处理中的核心地位。

# 2. FPGA在FFT处理中的应用理论

## 2.1 FPGA技术概述

### 2.1.1 硬件描述语言(HDL)基础

硬件描述语言(HDL),如VHDL和Verilog,是用于描述电子系统结构和行为的语言。在FPGA设计中,HDL允许工程师以文本形式描述逻辑电路,并通过综合工具转换成可在FPGA上实现的硬件配置。

```verilog

// Verilog代码示例:简单的2输入与门

module and_gate(

input wire a,

input wire b,

output wire out

);

assign out = a & b;

endmodule

```

在这个Verilog代码段中,我们定义了一个名为`and_gate`的模块,它接受两个输入`a`和`b`,并输出它们的逻辑与`out`。`assign`语句用于指定输出`out`的逻辑表达式,即`a`和`b`的与运算。

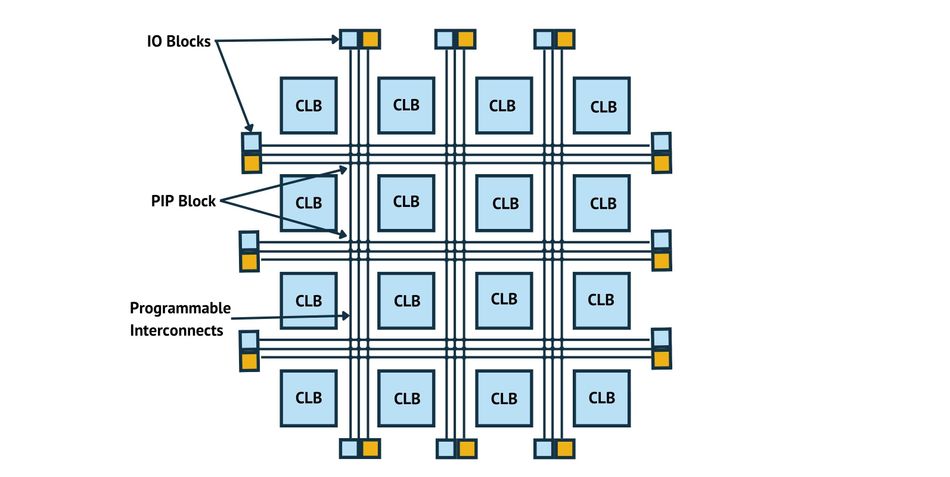

### 2.1.2 FPGA的并行处理能力

FPGA区别于CPU和GPU的一个重要特性是其并行处理能力。FPGA内部由大量的逻辑单元组成,这些单元可以被配置为实现特定功能的硬件电路。因此,FPGA能够同时执行多个计算任务,而不像CPU那样按顺序执行。

```mermaid

graph LR

A[输入数据] -->|并行处理| B(FPGA内部多个逻辑单元)

B -->|运算结果| C[输出数据]

```

如上图所示,数据流经FPGA时,可以被分配到内部不同的逻辑单元中进行并行处理,最终汇总成结果输出。这种能力使得FPGA在处理FFT这类可以高度并行化的算法时表现出色。

## 2.2 FFT算法原理详解

### 2.2.1 离散傅里叶变换(DFT)介绍

离散傅里叶变换(DFT)是将信号从时域转换到频域的一种数学方法。对于一个长度为N的离散时间信号,其DFT定义为:

```math

X[k] = \sum_{n=0}^{N-1} x[n] \cdot e^{-\frac{j2\pi}{N}kn}, k=0,1,...,N-1

```

其中,`x[n]`是时域信号,`X[k]`是对应的频域表示,`e`是自然对数的底,`j`是虚数单位。

DFT在频谱分析、信号处理等领域有广泛的应用。然而,DFT的计算复杂度为O(N^2),对于大型数据集来说效率低下。

### 2.2.2 FFT算法与DFT的关系

快速傅里叶变换(FFT)是对DFT的一种优化,通过分治策略显著减少了运算量。Cooley-Tukey算法是最著名的FFT算法之一,它将长度为N的DFT分解为两个长度为N/2的DFT。

```mermaid

graph TD

A[输入数据] --> B[蝴蝶操作]

B --> C[第一级DFT]

C --> D[第二级DFT]

D --> E[输出结果]

```

在上图中,数据通过一系列蝴蝶操作后,被分批处理成更小的DFT。这样,原本需要O(N^2)的运算量降低到了O(NlogN)。

## 2.3 FPGA实现FFT的优势与挑战

### 2.3.1 实时数据处理的优势

FPGA实现FFT的一个主要优势是其能够处理实时数据流。由于FPGA具有几乎无延迟的硬件级别并行处理能力,因此它能够对连续的数据样本进行实时处理,非常适合于需要快速响应的应用场景,如雷达信号处理或高频交易系统。

### 2.3.2 硬件资源限制与优化策略

尽管FPGA提供了强大的并行处理能力,但其资源是有限的。FPGA的逻辑单元、存储资源和I/O引脚都是有限的,而且一旦设计被部署,这些资源的配置就不能更改。

```table

| 资源类型 | 描述 |

| ------ | ---- |

| 逻辑单元 | 实现逻辑函数的硬件单元 |

| 存储块 | 内部RAM模块,用于数据存储 |

| DSP块 | 乘法器和累加器,用于数字信号处理 |

| I/O引脚 | FPGA与外部电路的接口 |

```

为了优化FPGA上的FFT实现,设计者需要采取多种策略,比如利用更高效的算法来减少逻辑单元的需求,或者调整数据宽度来平衡性能和资源使用。

# 3. FPGA上FFT算法设计与优化实践

## 3.1 基于FPGA的FFT算法设计

### 3.1.1 数据流设计

在FPGA上实现FFT算法时,数据流设计是关键步骤之一。数据流设计是指确定数据在FPGA内部的流动路径和处理方式。对于FFT算法,这意味着我们需要设计数据的输入、内部处理以及输出过程。

FFT算法在FPGA上的数据流设计通常包含以下几个方面:

- **输入模块**:负责将外部数据源的信号按照FFT算法的要求进行串行到并行的转换,以适应FPGA的并行处理特性。

- **内部计算模块**:包括蝶形运算单元、位逆序单元等,其中蝶形运算单元是FFT算法核心。

- **输出模块**:负责将处理后的数据进行并行到串行的转换,并输出到外部设备。

一个典型的数据流设计流程可以表示为以下步骤:

1. 数据接收:将输入数据经过缓冲存储到FPGA内部。

2. 位逆序重排:根据FFT算法要求对数据进行位逆序重排。

3. 进行FFT蝶形运算:通过迭代的方式逐步完成所有蝶形运算。

4. 数据输出:计算完成的数据通过输出模块传递给外部。

数据流设计的优化对提高整个FFT算法在FPGA上的性能至关重要。例如,在设计位逆序模块时,可以采用特殊的存储结构来实现快速位逆序操作,从而减少运算的延迟。

### 3.1.2 控制流设计

控制流设计指的是在FFT算法的实现过程中,对各种运算单元进行时序控制和数据流动的同步控制。控制流的设计决定了FFT算法的执行顺序和各模块之间的协调工作。

在FPGA上实现FFT算法的控制流设计主要包括:

- **控制信号生成**:根据FFT算法的执行阶段,生成

0

0