High-Level Synthesis面临的测试与验证问题:解决方案大揭秘

发布时间: 2025-01-03 05:46:00 阅读量: 10 订阅数: 18

# 摘要

高阶综合技术是现代数字系统设计的关键步骤,涉及从高层次设计到硬件实现的转换。本文旨在为读者提供一个全面的高阶综合测试与验证框架。文章首先概述了高阶综合技术,并讨论了测试与验证的理论基础,包括测试策略、验证框架和标准。接着,文章深入分析了测试与验证的实践案例,比较了综合前后验证的差异,并通过具体项目案例详细介绍了测试与验证策略的实施。此外,文章详细探讨了验证方法的自动化、加速技术以及测试工具的集成策略。最后,文章展望了高阶综合测试与验证的未来趋势,重点分析了新兴技术的应用前景和标准化的必要性。本文对于理解高阶综合测试与验证技术的当前状态和未来发展提供了有价值的视角。

# 关键字

高阶综合;测试与验证;自动化验证;验证加速;标准化;形式化验证

参考资源链接:[《从算法到数字电路:高级综合指南》](https://wenku.csdn.net/doc/1asfzsnxd9?spm=1055.2635.3001.10343)

# 1. 高阶综合技术概述

高阶综合技术在IT行业中扮演着至关重要的角色,特别是在现代电子系统设计中。通过将高级编程语言的算法转换成硬件描述语言(HDL),该技术极大提升了设计的抽象级别,允许开发者在更高层次上对系统进行建模、模拟和验证。本章节旨在为读者提供高阶综合技术的宏观概览,探讨其在快速迭代和复杂系统设计中的应用,并分析高阶综合技术如何在保证功能正确性的前提下,显著提升设计效率。

## 高阶综合技术的起源与发展

高阶综合技术起源于上世纪80年代,最初目的是为了简化硬件设计流程。随着技术的演进,它已经从简单的逻辑合成工具发展成为能够处理复杂算法和大规模设计的强大工具集。现代高阶综合不仅仅关注硬件逻辑的实现,还涵盖了时序优化、资源分配和功耗管理等多个维度。

## 高阶综合在现代设计中的作用

在现代电子系统设计中,高阶综合技术提高了设计过程的效率与可靠性。它允许设计师在系统级别进行抽象思考,然后利用综合工具自动实现底层硬件细节,从而缩短产品上市时间并降低设计错误的风险。此外,高阶综合技术也支持设计重用和模块化,这进一步加速了设计流程并增强了设计的灵活性。

## 面临的挑战与发展趋势

尽管高阶综合技术带来了许多便利,但同时也面临诸如语言表达能力、设计空间爆炸和验证复杂性等挑战。为了应对这些挑战,行业正在不断地研究与开发新的算法和工具,以提高设计质量和开发效率。未来,我们有望看到更多人工智能与机器学习技术被集成到高阶综合流程中,进一步提升自动化水平和优化性能。

# 2. 测试与验证理论基础

## 2.1 高阶综合中的测试方法论

### 2.1.1 测试策略的基本类型

在高阶综合中,测试策略的选择至关重要,因为不同的测试策略将直接影响到验证的效率和覆盖率。测试策略可以分为静态测试和动态测试两大类:

**静态测试** 不需要运行代码,通过分析代码结构,检查规范一致性,以识别潜在的错误。在高阶综合的上下文中,静态测试通常用于早期阶段,以评估设计的可综合性和符合性。举例来说,使用静态分析工具,如 lint 工具,可以对设计代码进行语法和规范检查。

**动态测试** 涉及运行代码,通过执行实际的测试用例来检验程序的行为是否符合预期。在硬件设计的验证中,动态测试包括功能仿真和硬件仿真,确保硬件描述语言(HDL)代码在逻辑上正确执行。

### 2.1.2 验证的理论框架和标准

验证理论框架主要通过定义一系列的步骤和方法来确保设计能够被正确实现。ISO/IEC 19761 "CMMI for Development" 是一个广泛被认可的软件工程和系统工程过程改进框架。该标准涉及验证和确认过程,为验证的计划、设计、实施提供了指导。

在硬件设计验证领域,IEEE 1800-2017 SystemVerilog 标准是一套广泛使用的语言和验证框架。它提供了一个统一的硬件描述、设计和验证语言,支持从行为级到门级的硬件建模。

## 2.2 验证的复杂性分析

### 2.2.1 验证环境的构建与管理

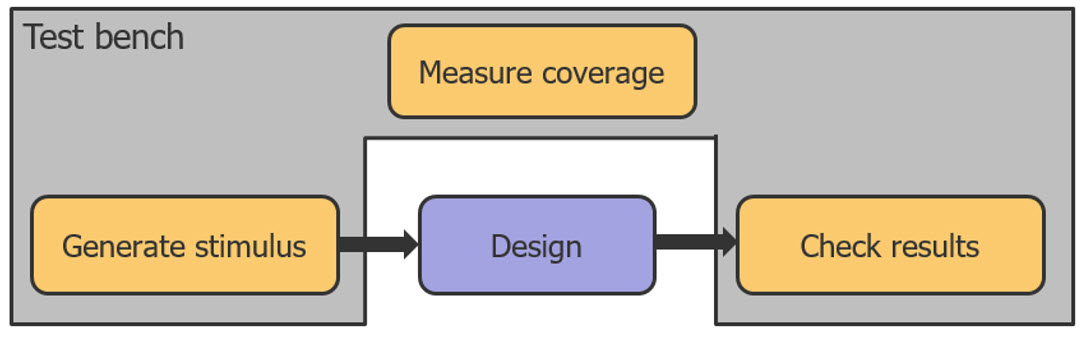

在高阶综合中构建验证环境是一个复杂过程,它涉及对各种硬件和软件组件的整合。验证环境包括:

- **激励生成器(Generator)**:产生测试向量,模仿真实世界中可能发生的输入。

- **监视器(Monitor)**:用来捕获和分析输出,确保其符合预期。

- **参考模型(Reference Model)**:提供一个行为上的参考,用于比较输出。

- **覆盖率模型(Coverage Model)**:衡量测试集达到的覆盖率。

为了管理和构建这样的验证环境,工程师经常采用商用的验证环境框架,如UVM(Universal Verification Methodology)。UVM提供了一系列的类和接口,帮助设计可重用、可配置的验证环境。

### 2.2.2 验证覆盖度量与分析

覆盖率分析用于衡量测试用例集是否充分覆盖了设计的所有方面。高阶综合的验证过程通常涉及以下几种覆盖率类型:

- **代码覆盖率(Code Coverage)**:检查是否执行了代码的每个语句、分支、条件等。

- **功能覆盖率(Functional Coverage)**:验证是否达到了特定的功能点和边界条件。

- **断言覆盖率(Assertion Coverage)**:确保断言在所有可能的情况下都被检查。

借助于覆盖率工具,设计者可以分析哪些部分已经通过测试验证,哪些部分还未覆盖。根据覆盖率的分析结果,设计者可以进一步优化测试用例集,提高验证的完备性。

## 2.3 高阶综合中的验证挑战

### 2.3.1 验证难题的类型和来源

在高阶综合的验证过程中,设计者面临各种挑战,主要可分为以下几类:

- **状态空间爆炸**:随着设计复杂度的增加,可能的状态数量呈指数级增长,使得全面验证变得不切实际。

- **异步控制逻辑验证**:在包含多个时钟域的复杂系统中,异步控制逻辑验证变得尤为困难。

- **接口协议一致性**:验证各种接口协议是否按照规范正确实现。

解决这些难题的策略包括:

- **抽象化技术**:通过抽象化降低状态空间的复杂性。

- **形式化验证**:使用数学方法来验证设计的正确性,特别是在关键协议和接口的验证上。

- **设计分块与分层验证**:将复杂设计分解成可管理的块,分别验证后整合。

### 2.3.2 面对挑战的理论解决方案

**抽象化技术** 通过移除设计中不影响验证结果的细节,简化模型。例如,可以将复杂的算术逻辑简化为更简单的形式,仅在需要的时候考虑具体的位宽和溢出效应。

**形式化验证** 依赖于数学证明来验证系统属性。例如,可以通过属性定义语言(PDL)来描述接口协议的预期行为,并使用形式化工具来检查设计是否符合这些属性。

**设计分块与分层验证** 允许验证人员在不同的设计层次上,从顶层到底层逐步进行验证。这种方式有助于更早地发现设计中的问题,避免在后期才发现导致整个项目延期。

```markdown

| 挑战类型 | 描述 | 解决方案 |

|-----------------|------------------------------------------|-------------------------------|

| 状态空间爆炸 | 随着设计复杂度增加,可能的状态数量激增。 | 抽象化技术、形式化验证 |

| 异步控制逻辑验证 | 在多时钟域系统中,异步控制逻辑验证复杂。 | 形式化验证、自定义验证平台 |

| 接口协议一致性 | 验证各种接口是否遵循规范 | 形式化验证、协议检查工具 |

```

通过这些理论解决方案的实施,设计者可以克服验证过程中的困难,提高验证的效率和覆盖率。在实践中,这些方法常常结合

0

0