【PCIe 3.0与存储技术】:快速数据访问的实现方法

发布时间: 2025-01-04 03:29:05 阅读量: 6 订阅数: 12

PCIE 3.0规范

# 摘要

本文深入探讨了PCIe 3.0技术及其在现代存储系统中的应用。文章首先概述了PCIe 3.0的基础架构,详细解析了其信号机制、层次模型以及扩展性和兼容性。随后,探讨了存储技术的基础知识,以及PCIe 3.0如何在存储系统中发挥作用,并促进了与存储技术的协同优化。第四章着重讨论了PCIe 3.0实现快速数据访问的方法,包括数据缓存优化、与非易失性内存(NVM)的整合,以及在存储网络中的应用案例。第五章则侧重于PCIe 3.0在实际应用中的性能测试、评估和在虚拟化环境中的角色,同时展望了PCIe存储技术的未来趋势。最后,文章分析了提升存储性能面临的技术挑战,并提出了相应的解决方案,包括诊断存储瓶颈、高可用性和数据保护策略,以及存储技术的生态发展和标准制定。本文为PCIe 3.0的深入理解和有效应用提供了全面的分析和指导。

# 关键字

PCIe 3.0;信号机制;存储技术;快速数据访问;性能测试;技术挑战;优化策略

参考资源链接:[PCIe specification revison3.0.pdf](https://wenku.csdn.net/doc/646074b45928463033adf8d0?spm=1055.2635.3001.10343)

# 1. PCIe 3.0技术概述

PCIe,全称 Peripheral Component Interconnect Express,是一种高速串行计算机扩展总线标准,主要用于连接主板和高速外围设备。PCIe 3.0作为该技术的第三代产品,相较于前两代,它显著提高了数据传输速率,达到了8 GT/s(Giga Transfers per second),提供了双倍于PCIe 2.0的带宽。PCIe 3.0的出现是为满足日益增长的数据处理需求,其技术特点包括更高的带宽效率、优化的电源管理机制以及改进的数据传输协议。

PCIe 3.0的设计允许设备在更短的时间内交换大量数据,这对于诸如图形处理、存储以及网络通讯等多种应用领域都至关重要。由于它的高效率和高性能,PCIe 3.0在数据中心和高性能计算环境中的应用变得越来越普遍。本章将从PCIe 3.0的基本概念和核心优势入手,为读者提供技术的初步认识,并为进一步深入研究PCIe 3.0技术打下基础。

# 2. PCIe 3.0架构深入解析

## 2.1 PCIe 3.0的信号机制

### 2.1.1 链路初始化和训练过程

PCI Express(PCIe)3.0是一种高速串行计算机扩展总线标准,它使用了点对点串行通信,允许数据以全双工方式传输。PCIe总线的初始化和链路训练过程是确保设备间通信正确建立的关键步骤。在PCIe 3.0标准中,这一过程遵循一系列精心设计的步骤来检测和配置链路。

链路初始化和训练开始于电气初始化,其中硬件设备会调整电压和时钟频率以满足PCIe规范的要求。一旦电气条件满足,链路将进入物理层链路初始化状态。在这里,链路会通过一系列的信号交换来确定连接的两端是否都是活跃的,并且确认它们是否支持PCIe 3.0标准。

接下来是链路训练和状态协商(LTSSM)阶段。LTSSM负责管理PCIe链路的各个状态,包括探测(Polling)、配置(Configuration)、启用(Recovery)等。在探测阶段,链路双方交换能力信息,并通过一系列的训练序列确定数据速率、通道数量以及数据流的方向。这一阶段还包含了对通道质量的评估,以确保通信质量满足标准要求。

链路的训练过程必须能够处理各种错误情况,如通道失配、速度不匹配等问题。在训练过程中,如果检测到错误,LTSSM会退回到较低的速率进行重试,直到链路可以稳定运行。训练过程的设计目标是实现最大化的链路宽度和速度,同时保证数据传输的完整性和可靠性。

```mermaid

graph LR

A[电气初始化] --> B[探测状态]

B --> C[配置状态]

C --> D[启用状态]

D --> E[数据传输状态]

E --> F{检查链路质量}

F -->|不满足| D

F -->|满足| G[链路训练完成]

```

### 2.1.2 数据包传输机制和流量控制

一旦链路初始化和训练过程成功完成,PCIe 3.0链路就可以开始数据传输。PCIe的数据包传输机制包括事务层包(TLPs)、数据链路层包(DLLPs)和事务层流量控制(Credit-based Flow Control)。

事务层包(TLPs)是数据包传输中的核心单元,它们负责携带请求或完成信息。TLPs包括地址、数据和控制信息。数据链路层包(DLLPs)则用于链路管理功能,例如链路的确认、错误检测和报告等。

事务层流量控制机制是PCIe 3.0中用来管理数据包流动的一种机制。流量控制使用“信用”系统,它为每个可能的事务方向分配信用值。发送方在发送数据前必须获得足够的信用值,这保证了接收方有足够缓冲区来处理接收到的数据。这是一种有效的流量控制机制,它可以避免数据包的溢出和丢包,同时最大化带宽利用率。

PCIe 3.0还采用了基于信用的流量控制来确保链路不会因发送方发送太多数据而过载。每个TLP在发送前需要从接收方获取相应的信用,而DLLP则包含信用更新信息。这样,发送方在任何时候都不会发送超出接收方处理能力的数据量。

```mermaid

graph LR

A[事务层包 (TLPs)] --> B{流量控制检查}

B -->|有足够信用| C[发送TLP]

B -->|信用不足| D[等待信用更新]

C --> E[数据链路层包 (DLLPs)确认]

E --> F[接收方处理TLP]

```

流量控制机制的实现涉及精确的信用管理。当TLP被成功接收后,接收方会向发送方发送DLLP以更新信用。这样,发送方可以实时了解接收方的缓冲区状况,并据此调整发送速度。

这些机制共同确保了PCIe 3.0链路能够高效、可靠地传输数据,为现代计算机系统提供了高速的I/O连接解决方案。

# 3. 存储技术基础及其与PCIe的关系

## 3.1 存储技术的关键概念

在深入探讨PCIe 3.0技术在存储系统中的应用之前,了解存储技术的基础概念至关重要。存储技术不仅仅是物理硬件的集合,还包括了与数据存储、检索和传输相关的各种协议和标准。

### 3.1.1 存储介质与I/O接口

存储介质是数据存储的基础,它包括了从传统的硬盘驱动器(HDD)到固态驱动器(SSD)的各种类型。每种存储介质的性能、可靠性和成本都有所不同。I/O接口则定义了存储介质与计算机系统之间数据传输的方式,如SCSI、SATA、SAS等。

### 3.1.2 存储协议和标准化

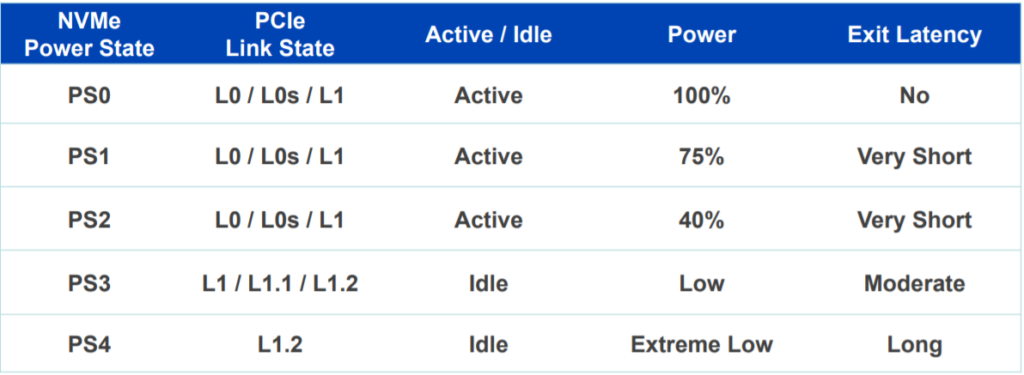

为了确保不同硬件和软件之间的兼容性,存储协议和标准化变得尤为重要。像ATA(Advanced Technology Attachment)、SCSI(Small Computer System Interface)以及近年来发展迅速的NVMe(Non-Volatile Memory Express)都是标准化协议的代表。

## 3.2 PCIe在存储系统中的作用

PCIe(

0

0