十进制计数器设计新思维:创新理念挑战传统设计

发布时间: 2025-01-06 17:38:52 阅读量: 8 订阅数: 16

FPGA与数字系统设计:实验八 使用ECS绘制六十进制计数器.doc

# 摘要

本文旨在全面介绍十进制计数器的设计原理、实践创新及性能优化。首先,概述了十进制计数器的基本概念和理论基础,包括其工作原理和数学模型。接着,深入探讨了计数器设计在硬件和软件方面的创新实践,以及用户界面的创新设计思路。随后,文章重点分析了性能评估的标准与方法,并提出了相应的优化策略。案例研究展示了优化措施的效果与价值。最后,展望了计数器设计未来的发展趋势,强调了技术创新和社会责任的重要性。本文通过理论与实践的结合,为十进制计数器的设计提供了全面的参考和指导。

# 关键字

十进制计数器;理论基础;设计创新;性能评估;优化策略;未来趋势

参考资源链接:[西南交通数电实验:1位十进制计数器与显示电路设计](https://wenku.csdn.net/doc/840oeaf8eq?spm=1055.2635.3001.10343)

# 1. 十进制计数器设计概述

在数字电子技术飞速发展的今天,十进制计数器作为一种基础的数字电路,其设计和应用贯穿于我们的日常工作和生活中。本章将对十进制计数器的设计进行概览性介绍,从而为后续章节中更深入的理论分析和实践案例探讨奠定基础。

## 十进制计数器的基本功能

十进制计数器的主要功能是按照十进制数制进行计数,能够在电子系统中实现从0计数到9的循环。它广泛应用于计时器、频率计、数字仪表以及各种计数控制场合。

## 设计目标与考量

设计一个高效、稳定的十进制计数器需要考虑多个方面,包括其计数速度、准确性、稳定性以及能耗等因素。合理的设计能够确保计数器在不同环境下都能可靠工作。

## 技术挑战与发展方向

十进制计数器的技术挑战主要包括提高计数速度、减少能耗、缩小体积等方面。未来的发展方向则可能聚焦在集成度更高、智能化控制以及与新型电子技术的融合上。

# 2. 十进制计数器的理论基础

## 2.1 十进制计数器的工作原理

### 2.1.1 传统十进制计数器的机制

传统十进制计数器是数字电子系统中不可或缺的一部分,它们在功能上模拟了自然数的计数过程。传统计数器通常通过一系列触发器(flip-flops)来实现,这些触发器按照特定的逻辑顺序相互连接。每达到一个特定的状态,触发器就会改变其输出,从而代表一个进位或数值的增加。

计数器的计数状态可以通过同步或异步方式来实现。在同步计数器中,所有的触发器在同一时钟信号下同步触发,这使得计数动作协调一致,但对时钟信号的稳定性要求较高。而在异步计数器中,触发器的触发并不需要依赖于同一个时钟信号,这降低了对时钟信号的依赖,但会引入额外的延迟。

### 2.1.2 计数器的数学模型与分析

从数学模型的角度看,十进制计数器通常表现为一个模数为10的有限状态机。每个状态代表一个特定的数值,当计数器从一个状态过渡到下一个状态时,它相当于数值加1。当计数器达到它的最大值(即9)后,下一个状态将回到0,并且可以产生一个进位信号。

该数学模型可以使用状态转移图来表示,图中的节点对应于计数器的状态,节点之间的有向边表示状态转换。通过分析状态转移图,我们可以了解计数器如何在不同状态之间进行转换,以及何时产生进位。

```

0000 (0)

↑ ↓

0001 (1)

↑ ↓

0010 (2)

↑ ↓

1000 (8)

↑ ↓

1001 (9)

↑ ↓

0000 (0) with carry out

```

从上图可以观察到,每一个状态通过增加1而转移,当到达1001后,下一个状态返回到0000,并且有一个进位输出。

## 2.2 创新设计概念

### 2.2.1 摒弃传统设计理念的必要性

尽管传统十进制计数器在电子系统中有着广泛的应用,但它们存在诸多局限性,如功耗、尺寸和速度等。随着微电子工艺的进步,新的设计理念和创新技术开始涌现,使得我们可以对传统计数器进行重新设计和优化。

例如,使用新材料如碳纳米管或石墨烯制造的新型晶体管,可以显著提高计数器的运行速度和减少功耗。同时,通过采用先进的集成电路设计方法,例如3D集成电路技术,可以在保持高集成度的同时减小芯片面积。

### 2.2.2 新思维下的设计原则

新的设计原则强调低功耗、高性能、高集成度和高可靠性。在设计过程中,需要综合考虑工艺技术、电路架构、系统集成等多个因素。例如,在电路架构设计中,可以考虑采用动态电源管理技术来降低能耗,同时通过优化逻辑门的设计来提高电路的工作频率。

设计原则还包括了对设计工具和自动化流程的依赖,如利用现代EDA(电子设计自动化)工具进行电路的仿真和验证,确保设计的正确性和可靠性。

## 2.3 计数器设计的挑战与机遇

### 2.3.1 当前技术限制的分析

在设计十进制计数器时,我们面临着诸多技术挑战。比如,随着集成度的增加,电路的热管理成为一大难题。高密度集成的芯片往往需要有效的散热方案来保证其性能和寿命。

此外,制造工艺的微缩化也带来了可靠性问题。随着特征尺寸的缩小,量子效应和材料缺陷的影响变得更加显著,这些都需要在设计阶段进行深入考虑。

### 2.3.2 创新思维如何解决传统问题

创新思维可以采用多方面的手段解决这些传统问题。比如,可以采用新材料和新的半导体技术来改善器件性能,从而解决功耗和速度的问题。对于热管理问题,可以设计集成式的散热结构,或者采用新型的散热材料。

同时,通过优化电路设计,可以在保持性能的同时减少功耗。例如,利用门控时钟技术可以有效减少不必要的功耗。对于可靠性问题,则可以通过增加冗余设计或采用错误检测和纠正算法来提高电路的鲁棒性。

在下一章节中,我们将通过具体的实践案例,深入了解十进制计数器设计的创新实践及其优化。

# 3. 十进制计数器设计的实践案例

## 3.1 硬件设计的创新实践

### 3.1.1 新型计数器电路设计实例

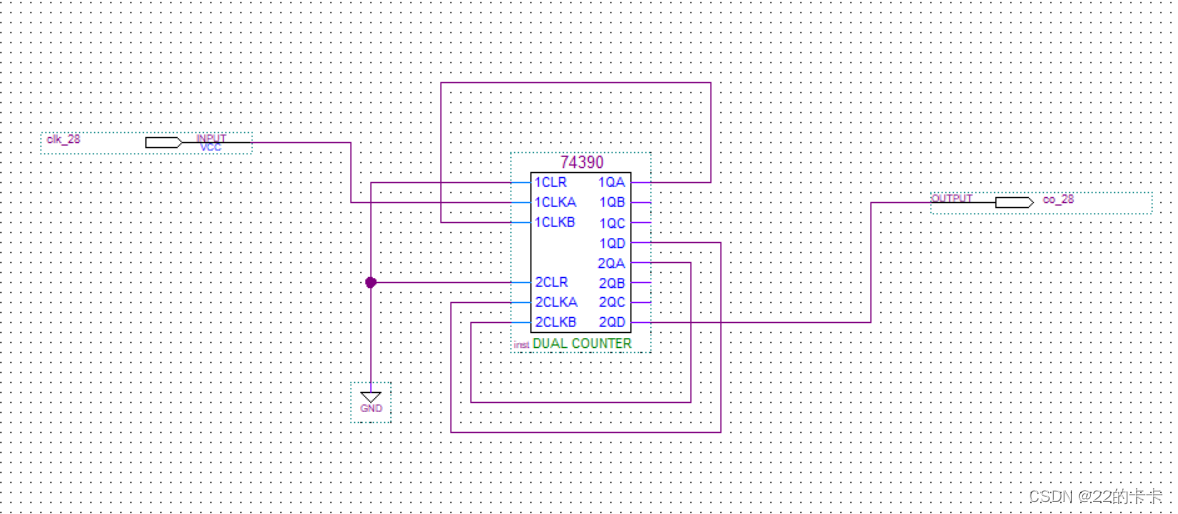

在数字电路设计领域,十进制计数器的硬件实现是一个经典的课题,它涉及到逻辑门电路的组合和时序逻辑电路的设计。随着集成电路技术的发展,传统的74系列芯片逐渐被可编程逻辑设备如FPGA和CPLD所取代。这里,我们将探索一个基于FPGA的新型十进制计数器硬件设计方案。

为了实现一个十进制计数器,我们需要一个可以计数从0到9的电路

0

0