数字电路设计要点:1位十进制计数器关键技术分析

发布时间: 2025-01-06 17:25:25 阅读量: 17 订阅数: 13

# 摘要

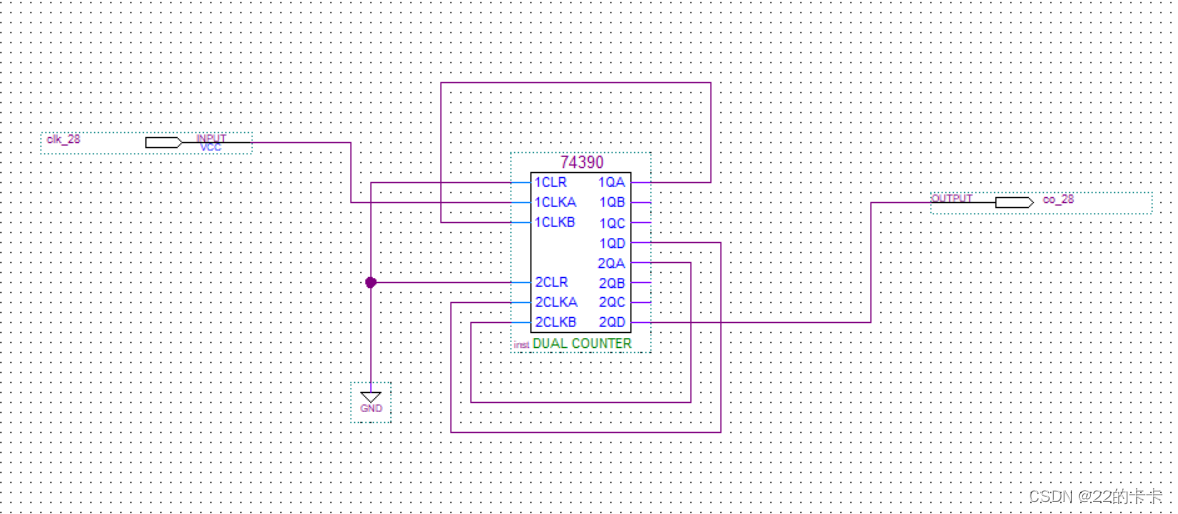

数字电路设计是电子工程领域的基础,其中1位十进制计数器的设计对于实现数字系统至关重要。本文首先介绍了数字电路设计的基础知识,然后详细探讨了1位十进制计数器的概念、组成以及理论分析,包括计数器的工作原理、逻辑设计和模数与状态转换。在实践方面,文章着重讲述了电路元件的选择与搭建,以及设计实现与验证过程,包括使用仿真软件进行电路模拟和实际电路搭建与测试。最后,本文还讨论了优化策略和计数器功能的扩展应用,如减少功耗、延迟以及实现多位十进制计数器的级联方法,旨在提升计数器性能和可靠性。

# 关键字

数字电路设计;1位十进制计数器;理论分析;逻辑设计;电路模拟;性能优化

参考资源链接:[西南交通数电实验:1位十进制计数器与显示电路设计](https://wenku.csdn.net/doc/840oeaf8eq?spm=1055.2635.3001.10343)

# 1. 数字电路设计基础

在数字电路设计的广阔天地中,基础概念和原理是构建任何复杂系统所不可或缺的基石。数字电路通常由组合逻辑电路和时序逻辑电路组成,涉及逻辑门、触发器、计数器等基本组件。了解这些组件的工作原理和如何将它们组合在一起,对于设计高效、稳定的数字系统至关重要。本章将从基本的数字电路概念讲起,涵盖布尔代数、逻辑门的基础知识,以及触发器在数字电路中的作用,为后续章节中1位十进制计数器的设计与优化提供理论支撑。让我们一起步入数字电路设计的世界,探索其奥秘。

# 2. 1位十进制计数器的概念与组成

### 2.1 计数器的定义与基本原理

计数器是数字系统中的一种基本组成元件,它的核心功能是记录输入脉冲的数量,并将这些脉冲转换为相应的数字输出。在我们的日常生活中,计数器被广泛应用于时钟、计时器、计算设备等领域。简单来说,计数器可以看作是一个能够执行基本计数操作的电子电路。

根据计数器能够存储的位数,我们可以将计数器分为1位计数器、多位计数器等。1位十进制计数器,顾名思义,是能够对0到9这十个数字进行计数的装置,它能以十进制形式表示0到9这十个数字。

计数器的基本工作原理通常涉及两个主要操作:计数和复位。当计数器接收到一个计数脉冲,它会根据当前状态进行状态转换,例如从“0”变为“1”,从“9”变为“0”。而当接收到复位信号时,计数器将重置至初始状态,通常是“0”。

### 2.2 1位十进制计数器的组成

一个典型的1位十进制计数器主要由以下几个部分组成:

- 触发器(Flip-Flops):触发器是构成计数器的基本单元,通常使用的是T触发器或JK触发器。触发器具有记忆功能,能够保存1位二进制信息,并根据输入脉冲改变状态。

- 解码器(Decoder):解码器用于将触发器的二进制输出转换为十个输出线上的单个激活信号,每个输出线代表一个十进制数位。

- 逻辑门(Logic Gates):逻辑门电路用于产生触发器的时钟信号和复位信号,并对计数器的状态进行必要的控制。

### 2.3 计数器的主要类型

根据触发方式的不同,计数器可以分为两种主要类型:同步计数器和异步计数器。

#### 同步计数器

同步计数器的特点是,其所有的触发器都是由同一个时钟脉冲信号控制的。这意味着所有触发器的状态转换几乎在同一时刻发生,因此,同步计数器可以实现高速的计数操作。由于触发器间没有延迟差异,同步计数器也易于设计和分析。

#### 异步计数器

异步计数器的各个触发器由不同的时钟脉冲信号控制,这些时钟信号通常是前一个触发器的输出。因此,相对于同步计数器,异步计数器在状态转换时会有延迟,但这使得它们在设计上更为简单,且对时钟的要求不如同步计数器那么严格。

总结起来,同步计数器适合于高速和高精度的应用,而异步计数器则适合于成本和设计复杂度受限的场合。1位十进制计数器可以是同步的,也可以是异步的,具体取决于设计需求和应用场景。

在接下来的章节中,我们将详细介绍1位十进制计数器的工作原理、逻辑设计、设计实践、优化与扩展。每个章节都会深入分析计数器的工作细节,并探讨实现计数器时需要考虑的各种因素。

通过本章节的介绍,我们已经对1位十进制计数器有了一个基础的认识。在下一章中,我们将深入探讨计数器的工作原理,包括同步与异步计数器的区别,以及计数器的模数与状态转换的详细分析。

# 3. ```

```

0

0