IIC总线与FPGA结合:HDL实现细节的全面剖析(硬件编程高级教程)

发布时间: 2024-12-13 23:09:21 阅读量: 12 订阅数: 32

基于FPGA的可配置IIC总线接口设计-论文

参考资源链接:[I2C总线协议详解:从标准到高速模式](https://wenku.csdn.net/doc/2cqtoantss?spm=1055.2635.3001.10343)

# 1. IIC总线与FPGA结合的理论基础

## 1.1 通信协议与硬件平台的融合

在现代电子系统设计中,IIC总线作为一种广泛使用的串行通信协议,与FPGA的结合为工程师提供了灵活性与高性能的双重优势。本章将概述IIC总线的基本原理,并探讨其与FPGA结合时的理论基础,为后续章节深入讨论具体实现和应用案例打下坚实基础。

## 1.2 IIC总线简介

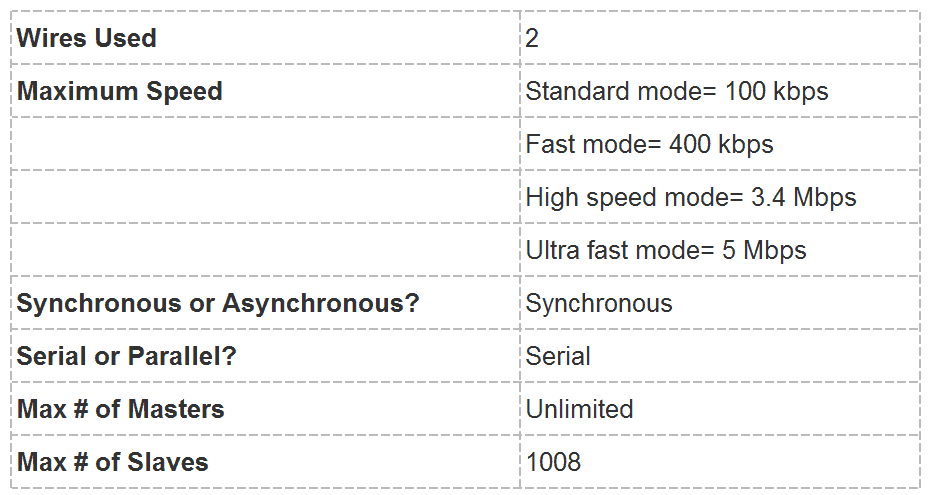

IIC(Inter-Integrated Circuit)总线是由Philips半导体公司在1980年代初期开发的一种多主机、多从机、串行总线接口。其旨在简化微控制器与各种外围设备之间的连接,广泛应用于嵌入式系统中。IIC总线使用两条线(一条数据线SDA和一条时钟线SCL)实现数据的串行传输,而且支持多个从设备的寻址。

## 1.3 FPGA在IIC总线应用中的作用

现场可编程门阵列(FPGA)是现代数字电路设计的基石之一,其在IIC总线应用中的作用主要体现在提供高度定制化的逻辑控制,以及处理复杂的时序和协议转换。通过FPGA,工程师能够实现IIC总线协议控制器的设计,从而与IIC兼容的外围设备进行通信,或实现高性能数据处理和传输。随着FPGA技术的进步,其在IIC总线应用中的角色愈发重要,特别是在要求高速、实时处理的应用场合。

## 1.4 理论与实践的结合

理解IIC总线与FPGA结合的理论基础是实践的前提。首先,我们将探讨IIC总线的工作原理,包括信号线、协议规则和时序要求。接着,我们将深入了解FPGA的基本原理,特别是其可编程性和硬件描述语言(HDL)设计流程。通过本章的学习,读者应能够掌握将IIC总线集成到FPGA项目中的基本知识和技能,为后续章节的深入讨论做好准备。

# 2. FPGA的基础知识和开发环境搭建

FPGA(现场可编程门阵列)是现代电子设计领域中不可或缺的组成部分。由于其可编程特性,FPGA能够实现复杂系统的快速原型开发和灵活配置。在本章节中,我们将详细探讨FPGA的基本概念、特性以及如何搭建一个有效的FPGA开发环境。

## 2.1 FPGA的基本概念和特性

### 2.1.1 可编程逻辑器件的发展历程

可编程逻辑器件的发展经历了从最初的可编程逻辑阵列(PLA)到复杂PLA(CPLD),再到FPGA的演进。FPGA以其高密度、高性能、灵活的编程能力成为了工业界和学术界的标准选择。

最初的PLA是一种可以由用户定义逻辑门组合的集成电路。随后出现的CPLD提供了更密集的逻辑单元和更丰富的互连结构,但与之相比,FPGA提供了更高的集成度和更丰富的资源,包括RAM、DSP、处理器内核等。

### 2.1.2 FPGA的内部结构和工作原理

FPGA由可编程逻辑块、可编程互连以及输入输出模块组成。逻辑块通常由查找表(LUTs)、触发器和专用的乘法器等构成。通过配置这些逻辑块,用户可以实现所需的逻辑功能。

FPGA的可编程互连允许用户定制信号在芯片内部的流向。这些互连资源包括通用的开关矩阵和专用的长线资源。FPGA的配置存储在芯片内的非易失性存储器中,包括SRAM、闪存或反熔丝等。

## 2.2 FPGA开发工具和仿真环境

### 2.2.1 Xilinx Vivado设计套件的介绍

Xilinx Vivado是FPGA设计领域广泛使用的设计套件。它提供了一套完整的工具集,包括逻辑设计、IP集成、综合、实现以及针对FPGA的硬件调试等。

Vivado的设计流程开始于逻辑设计阶段,支持HDL代码的输入和模块化设计。综合阶段将HDL代码转换为逻辑门级描述,并进行优化。实现阶段包括布局布线、时序分析和生成用于配置FPGA的比特流文件。

### 2.2.2 ModelSim仿真软件的使用技巧

ModelSim是业界领先的仿真软件,用于验证FPGA设计的功能正确性。它支持多种HDL语言,包括VHDL和Verilog,并提供了强大的测试平台。

仿真过程包括编写测试台、编写测试向量、运行仿真以及分析结果。ModelSim具有分层仿真的能力,可以模拟整个系统的不同部分。此外,它还提供了波形查看器和代码覆盖工具,有助于调试和改进设计。

## 2.3 FPGA设计流程详解

### 2.3.1 设计输入和代码编写

设计输入通常通过HDL代码来完成,代码编写需要遵循特定的设计风格和编码规范。HDL代码一般包括模块声明、端口映射、信号和变量定义、结构描述和行为描述等部分。

良好的编码习惯有助于提高代码的可读性和可维护性,比如使用有意义的命名、避免重复代码和模块化设计。设计输入后,需要使用仿真工具检查代码是否存在逻辑错误。

### 2.3.2 功能仿真和时序分析

功能仿真主要检查设计是否符合预期的逻辑功能。编写测试台对设计进行激励,验证输出是否符合设计输入的预期。时序分析则确保设计满足时序要求,避免出现时序违规。

时序分析通常在综合后进行,考虑了实际的路径延迟和时钟偏斜。通过分析报告,设计者可以识别关键路径和时序瓶颈,并进行相应的优化。

### 2.3.3 硬件调试和实际应用

在硬件调试阶段,将生成的比特流文件下载到FPGA中,并进行实际操作。这包括查看逻辑分析仪输出、使用嵌入式调试工具(如Xilinx的ChipScope)或者LED和开关等简单接口检查设计状态。

在实际应用中,FPGA设计需要根据应用场景进行必要的调整。这可能包括修改引脚分配、调整时钟网络以及优化功耗等。测试环境应模拟实际工作条件,确保设计在目标应用中稳定运行。

在下一章节中,我们将详细介绍IIC总线协议的细节以及如何在FPGA中实现它。IIC总线作为一种广泛使用的串行通信协议,在现代电子系统中发挥着重要的作用。通过FPGA实现IIC协议,可以进一步扩展其在各种应用中的可能性。

# 3. ```

# 第三章:IIC总线协议详解及HDL实现

## 3.1 IIC总线协议的核心要素

### 3.1.1 通信协议的基本概念

在深入IIC总线协议之前,首先需要对通信协议有一个基础的理解。通信协议定义了数据交换的格式、时序、通信规则等,确保了不同设备间能够有序高效地进行数据传输。IIC总线协议,作为一种被广泛使用的串行通信协议,有其独特之处。

### 3.1.2 IIC总线的信号线和时序分析

IIC总线使用两条信号线,分别是串行数据线SDA和串行时钟线SCL。SDA线负责数据的传输,而SCL线用于时钟同步。在数据传输过程中,数据线的每个状态变化都需要在时钟线的一个周期内完成。

为了深入理解IIC总线的工作方式,下面将通过一个简单的数据传输时序图来进行分析:

```

SDA __/``\__/``\__/``\__/``\__/``\__/``\__/``\__/``\__/``\_

______________________ ____________________

SCL _/ \_/ \_/ \_/ \_/ \_

```

如上图所示,SDA线上的数据在SCL线的高电平期间保持稳定。开始信号定义为SDA从高电平跳变到低电平,结束信号则相反。数据在SCL的高电平期间发送,每个字节数据后跟随一个应答位。数据按位从MSB到LSB传输。

在实际设计HDL代码时,必须严格遵守这个时序规则,以确保数据的正确传输。

## 3.2 IIC总线在FPGA中的HDL实现

### 3.2.1 IIC主控制器的设计实现

IIC主控制器是整个通信的核心,负责发起数据传输和产生时钟信号。在FPGA中实现时,需要设计状态机来管理不同的通信状态,如空闲、启动、发送数据、接收数据、停止等。

下面是一个简化版的IIC主控制器的状态机伪代码实现:

```vhdl

type IIC_MASTER_STATE is (IDLE, START, SEND, RECEIVE, STOP);

signal state : IIC_MASTER_STATE := IDLE;

begin

process(SCL, SDA)

begin

case state is

when IDLE =>

-- 进入空闲状态逻辑

0

0