PCB设计中的IIC总线注意事项:避免常见错误的技巧(PCB设计高级指南)

发布时间: 2024-12-13 23:14:09 阅读量: 57 订阅数: 32

I2C总线PCB设计总结

参考资源链接:[I2C总线协议详解:从标准到高速模式](https://wenku.csdn.net/doc/2cqtoantss?spm=1055.2635.3001.10343)

# 1. IIC总线基础与原理

## 1.1 IIC总线简介

IIC(Inter-Integrated Circuit)总线,又称I2C总线,是一种由飞利浦公司(现为NXP半导体公司)在1982年推出的一种串行通信总线。由于其简单、高效和易用的特性,IIC总线广泛应用于现代电子设备中,特别是在微控制器和各种外围设备之间的通信。

## 1.2 IIC总线核心特性

IIC总线支持多主机和多从机架构,允许在同一总线上挂载多个主控器和从属设备。通信过程遵循主从模式,即主设备发起通信,从设备响应请求。核心特性包括:

- **串行数据传输**:使用两条线(一条数据线SDA,一条时钟线SCL)实现数据和控制信号的传输。

- **地址识别**:每个从设备都有唯一的地址,主设备通过地址识别目标从设备以进行数据交换。

- **时钟同步**:SCL时钟线由主设备产生,确保数据在所有设备间同步传输。

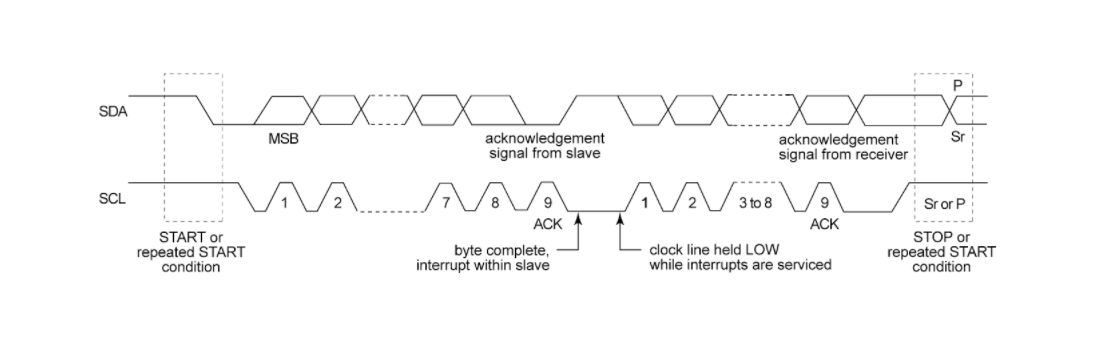

## 1.3 IIC总线通信原理

IIC总线基于主从通信模型,其通信过程通常包括如下步骤:

1. **启动信号**:主设备通过改变SDA和SCL线的电平状态生成启动信号。

2. **发送地址**:主设备发送目标从设备的地址以及传输方向(读或写)。

3. **数据传输**:在从设备确认地址后,主设备与从设备之间按照时钟信号进行数据的发送和接收。

4. **结束信号**:通信结束后,主设备发出停止信号以结束通信。

为了深入理解IIC总线的工作机制,下一章节将讨论IIC总线硬件设计中的电气特性和连接规则。

# 2. IIC总线硬件设计注意事项

在设计IIC总线硬件时,工程师需要考虑的方面远不止电气连接那么简单,从信号电平的兼容性到总线的物理布局,每一步都会对系统的稳定性和性能产生影响。这一章节将深入探讨硬件设计中应注意的要点,包括电气特性、连接规则和地址分配。

## 2.1 IIC总线的电气特性

### 2.1.1 信号电平与兼容性

IIC总线使用的是开漏输出和上拉电阻来实现电平的拉高和低电平的输出。这一特性要求所有连接到总线上的设备都必须使用兼容的逻辑电平。

上拉电阻的作用至关重要,因为它决定了IIC总线的空闲状态和有效状态。在没有设备输出低电平的时候,上拉电阻将保持总线在高电平状态。使用不当的上拉电阻值可能导致信号上升时间过长,无法满足IIC的定时要求,或者由于电流过大而损坏设备。

在设计时,需要根据IIC设备的输入电平门限和总线容量来计算上拉电阻值。为了确保信号的正确识别,一般推荐使用1.8V至3.3V的设备,并注意不同厂商设备的兼容性。

```markdown

| 设备电压 | 最小高电平 | 最大低电平 | 上拉电阻推荐值 |

|----------|------------|------------|----------------|

| 1.8V | 1.35V | 0.45V | 2.2kΩ |

| 3.3V | 2.5V | 0.8V | 2.2kΩ |

```

### 2.1.2 传输速率与定时要求

IIC总线支持不同的传输速率,包括标准模式(100kHz)、快速模式(400kHz)以及更快的快速+模式(1MHz)和高速模式(3.4MHz)。随着速率的增加,对信号的稳定性和上升时间的要求也变得更加严苛。

定时要求对于高速通信尤为重要。例如,快速模式下,总线设备必须能够提供足够的驱动电流,确保在规定的时间内完成信号状态的切换。设计时要充分考虑这些因素,确保在最恶劣的工作条件下设备都能满足定时要求。

## 2.2 IIC总线的连接规则

### 2.2.1 上拉电阻的选择与计算

在IIC总线上,上拉电阻的大小直接影响到总线的电气性能。上拉电阻的选择应根据总线上的设备数量、电流驱动能力以及走线电容等因素进行计算。

一个常用的公式是:

\[ R = \frac{V_{dd} - V_{ol}}{I_{ol} + I_{sc}} \]

其中:

- \(V_{dd}\) 是供电电压。

- \(V_{ol}\) 是输出低电平时的最大电压。

- \(I_{ol}\) 是输出低电平时的最大允许电流。

- \(I_{sc}\) 是总线短路电流。

### 2.2.2 总线长度与布线策略

总线长度会对信号质量产生显著影响,尤其是在高速模式下。较长的线路会产生较大的电感和电容,影响信号的完整性。在设计时,应尽量缩短走线长度,并避免不必要的锐角或90度弯角。

在布线时需要考虑以下策略:

- 尽量使用双绞线或者在信号线周围使用地平面来减少串扰。

- 避免在总线附近布置高速信号线,以减少电磁干扰。

- 在PCB设计中,为总线预留足够的空间,以便于调试和后续维护。

## 2.3 IIC总线的地址分配

### 2.3.1 硬件地址的确定方法

IIC总线上的每个设备都有一个固定的7位或10位硬件地址。地址的确定方法通常在设备的数据手册中提供,这些信息是确保设备能够正确通信的关键。

在设计时,需要仔细分配每个设备的地址,确保在同一总线上不会有地址冲突。一些设备可能具有可编程地址引脚,可以通过硬件连接来设置不同的地址。

### 2.3.2 软件地址的配置技巧

除了硬件地址之外,一些IIC设备还支持软件配置的地址。这种方法为地址分配提供了更多的灵活性,但也增加了配置的复杂性。

在配置软件地址时,应遵循设备手册的指导,并确保在设备上电或复位后完成地址的配置。一些设备可能需要特定的通信协议来设置地址,比如发送特定的命令序列。

通过这些硬件设计注意事项的详细了解,我们可以确保设计出稳定可靠的IIC总线系统。在下一章中,我们将探讨如何在软件层面实现IIC总线的通信协议和数据传输操作。

# 3. IIC总线软件设计实践

在深入理解IIC总线通信协议和硬件设计要点之后,软件设计实践成为实现高效、稳定IIC总线通信的关键一步。本章将详细介绍IIC总线通信协议的软件层面理解、数据传输操作以及接口编程的实际应用。

## 3.1 IIC总线通信协议理解

### 3.1.1 数据帧结构与传输规则

IIC总线的数据帧结构设计简洁,主要由起始信号、数据帧和停止信号组成。数据帧内包含设备地址和数据位,每个字节数据后跟随一个应答位(ACK)。理解这些细节对于编写符合协议的软件至关重要。

```mermaid

sequenceDiagram

participant Master

participant Slave

Master->>Slave: Start + Address + R/W + Data1 + ACK

Master->>Slave: Data2 + ACK

Master->>Slave: Data3 + ACK

Master->>Slave: DataN + ACK

Master->>Slave: Stop

```

在上述流程图中,可以看到数据帧从主设备发出起始信号后,紧接着是设备地址以及读写标志位(R/W),然后是数据字节和应答位。每个数据字节后都要等待应答信号,才能进行下一个字节的传输,最后以停止信号结束。

### 3.1.2 启动与停止条件的实现

启动和停止条件是IIC通信中非常重要的部分,它们标志着一次数据传输的开始和结束。在软

0

0