【Verilog与VHDL的区别】:Verdi加载时的5个注意事项

发布时间: 2024-12-26 20:18:05 阅读量: 4 订阅数: 10

verdi加载vhdl和verilog混合RTL设计的详细方法

# 摘要

本论文深入探讨了硬件描述语言(HDL)在数字电路设计领域中的应用,特别关注了Verilog和VHDL这两种主流语言。通过对Verilog与VHDL的基本差异、高级特性和加载注意事项的分析,本文揭示了两种语言在语法结构、设计方法学、设计流程和工具链以及高级设计概念上的不同表现和优势。同时,论文还讨论了在实际应用中,如何有效加载和优化Verilog与VHDL代码,避免常见错误,并提出了性能优化的策略。最后,本文对Verilog与VHDL的发展前景进行展望,并提供了选择合适设计语言的建议,以适应不同项目需求和技术趋势。

# 关键字

硬件描述语言;Verilog;VHDL;设计方法学;性能优化;代码加载;技术融合

参考资源链接:[verdi混合RTL设计加载三步法:解决vhdl与verilog整合难题](https://wenku.csdn.net/doc/6468b7565928463033dd2583?spm=1055.2635.3001.10343)

# 1. 硬件描述语言概述

硬件描述语言(HDL)是电子系统设计的基础,它允许设计师以文本形式描述电子系统的行为和结构。HDL的出现极大地简化了复杂的电子系统设计过程,允许设计师通过软件仿真来验证设计逻辑的正确性,减少了实际硬件原型制作的时间和成本。HDL主要分为两大类:行为级描述语言和结构级描述语言。行为级语言侧重于描述电路的功能和行为,而不关心具体的硬件结构,如Verilog和VHDL;结构级语言则侧重于描述电路的物理实现,如VHDL-AMS和SystemVerilog。随着集成电路复杂度的提升,HDL的应用范围也不断扩展,它已成为现代数字逻辑设计不可或缺的一部分。

# 2. ```

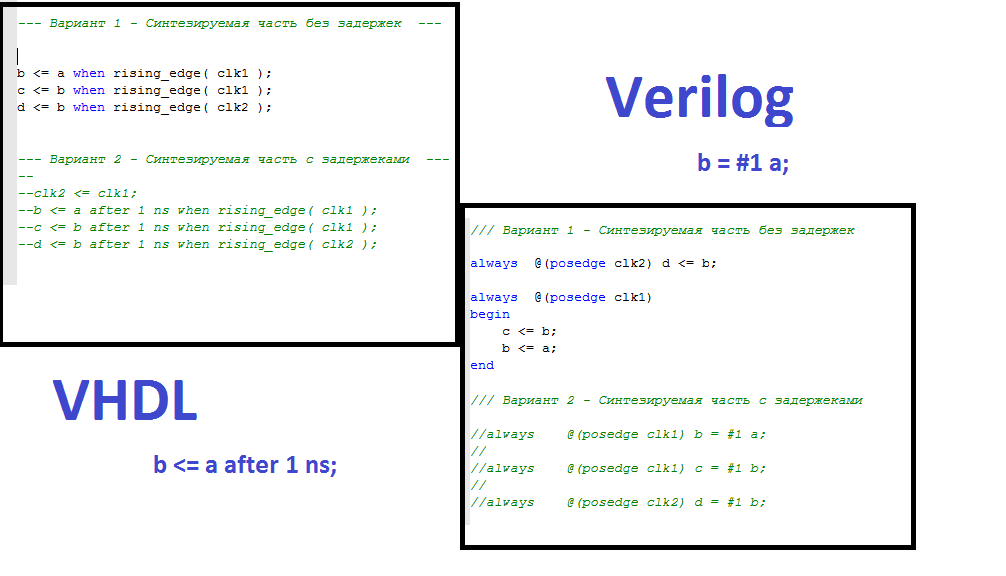

# 第二章:Verilog与VHDL的基本差异

## 2.1 语法结构的对比

### 2.1.1 基本语法元素的比较

在硬件描述语言(HDL)的世界里,Verilog和VHDL作为两大主流语言,各有其鲜明的语法特点。Verilog的语法借鉴了C语言,易于编写和理解,非常适合进行硬件级的建模和仿真。例如,在Verilog中,我们使用关键字`module`来定义一个模块,而`endmodule`用来标记模块的结束。

```verilog

module my_module(input a, input b, output reg c);

// 模块实现逻辑

endmodule

```

另一方面,VHDL的语法则显得更为严密和复杂。它深受Ada语言的影响,使用更为正式的结构来描述硬件设计,比如用`entity`和`architecture`块来定义组件和行为。

```vhdl

entity my_entity is

port(

a : in std_logic;

b : in std_logic;

c : out std_logic

);

end entity my_entity;

architecture behavior of my_entity is

begin

-- 设计实现部分

end architecture behavior;

```

### 2.1.2 模块和实体定义方式的对比

在定义模块和实体时,两种语言的定义方式也有所不同。Verilog使用端口列表来声明模块的输入和输出,其语法简洁直观。VHDL中,模块被称作`entity`,其端口声明在`entity`声明中独立进行,然后在`architecture`块中进行实现。

这种差异不仅体现在语法上,更是两种语言设计理念的体现。Verilog更加注重于快速原型和硬件描述的简洁性,而VHDL则强调设计的结构化和清晰性。

## 2.2 设计方法学的差异

### 2.2.1 数据流描述方法

数据流描述方法侧重于描述硬件中信号之间的流动关系。在Verilog中,可以通过连续赋值语句或运算符来实现数据流描述,如下示例展示了使用运算符实现的4位加法器。

```verilog

module adder_4bit(

input [3:0] a, b,

input cin,

output [3:0] sum,

output cout

);

assign {cout, sum} = a + b + cin;

endmodule

```

而在VHDL中,数据流描述通常是通过信号赋值语句实现的,例如:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity adder_4bit is

Port ( a : in STD_LOGIC_VECTOR (3 downto 0);

b : in STD_LOGIC_VECTOR (3 downto 0);

cin : in STD_LOGIC;

sum : out STD_LOGIC_VECTOR (3 downto 0);

cout : out STD_LOGIC);

end adder_4bit;

architecture dataflow of adder_4bit is

begin

sum <= a + b + cin;

cout <= '1' when (a + b + cin) > 15 else '0';

end dataflow;

```

### 2.2.2 行为描述方法

行为描述方法关注于描述硬件的行为本身,而不直接描述其结构。Verilog通过`always`块和敏感列表来描述行为,这允许设计师用过程性代码来表达复杂的控制逻辑。

```verilog

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

// 同步复位逻辑

end else begin

// 正常工作逻辑

end

end

```

VHDL则使用`process`块来实现类似的功能,提供了对信号状态变化的监听。

```vhdl

process(clk, rst_n)

begin

if rst_n = '0' then

-- 同步复位逻辑

elsif rising_edge(clk) then

-- 正常工作逻辑

end if;

end process;

```

### 2.2.3 结构化描述方法

结构化描述方法使用模块的层次化组装来实现复杂的硬件系统。在Verilog中,我们可以使用模块实例化来构建层次化设计。

```verilog

module top_module(

input clk,

input rst_n,

// 其他输入输出端口

);

sub_module instance_1(.clk(clk), .rst_n(rst_n));

// 其他子模块实例化

endmodule

```

VHDL中,层次化设计是通过组件声明和实例化来实现的,它允许设计师通过配置`component`声明来连接不同的模块。

```vhdl

architecture structural of top_module is

component sub_module

port(

clk : in std_logic;

rst_n : in std_logic;

-- 其他端口声明

);

end component;

signal clk, rst_n : std_logic;

-- 其他信号声明

begin

U1 : sub_module port map(clk => clk, rst_n => rst_n);

-- 实例化其他子模块

end architecture structural;

```

## 2.3 设计流程和工具链

### 2.3.1 集成设计环境的比较

在集成设计环境中,Verilog和VHDL都拥有广泛支持的工具,如Xilinx的Vivado、Intel的Quartus、Altera的ModelSim等。这些工具对于两种语言都提供了编译、仿真、调试和综合等功能。尽管如此,每种工具对两种语言的支持程度和用户体验可能会有所不同。

### 2.3.2 编译、仿真和综合工具的选择

对于编译和综合,由于两种语言的语法和设计哲学的差异,不同的工具可能对每种语言有不同程度的优化能力。例如,某些综合工具可能在将VHDL代码综合为门级网表时更加高效,而另一种工具可能对Verilog代码的优化更加出色。

```mermaid

graph LR

A[设计输入] --> B[编译]

B --> C[仿真]

C --> D[综合]

D --> E[布局与布线]

E --> F[生成比特流]

F --> G[下载到FPGA]

```

仿真阶段是验证设计的正确性的重要步骤,不同的仿真工具对Verilog和VHDL的支持程度也不尽相同。了解各种工具在编译、仿真和综合方面的优劣,有助于设计师根据项目需求做出更好的工具选择。

# 3. Verilog与VHDL的高级特性对比

## 3.1 参数化设计和模块化

参数化设计和模块化是硬件描述语言中重要的高级特性,它们能够显著提高设计的灵活性和重用性。在本节中,我们将深入探讨Verilog与VHDL在这一方面的差异和应用。

### 3.1.1 Verilog中的generate语句和参数化

在Verilog中,`generate`语句允许设计者根据参数化的值生成重复的硬件结构。这在处理参数化模块时尤其有用,例如,在创建RAM存储器或可配置的算术逻辑单元时。通过参数化,设计者可以定义模块的行为和结构,而不必为每种可能的配置编写独特的代码。

```verilog

module parameterized_adder #(

parameter WIDTH = 8

)(

input wire [WIDTH-1:0] a,

input wire [WIDTH-1:0] b,

output wire [WIDTH:0] sum

0

0