Verdi加载工具深度剖析:5个高效处理RTL代码的策略

发布时间: 2024-12-26 19:21:30 阅读量: 4 订阅数: 10

verdi加载vhdl和verilog混合RTL设计的详细方法

# 摘要

本文介绍了Verdi加载工具和RTL代码的基础知识及其在集成电路设计中的重要性。首先,概述了RTL代码的定义、特性以及其在集成电路设计中的关键作用,并分析了RTL代码质量对芯片性能的影响。随后,探讨了Verdi工具的理论框架,包括其工作原理、核心功能、优势与局限性。文章进一步提出了高效处理RTL代码的多种策略,涵盖了代码质量保证、故障检测与调试以及性能优化。通过对Verdi应用案例的分析,展示了工具在实践中的应用效果和集成方式。最后,展望了Verdi工具的未来发展趋势,包括技术更新、人工智能和云平台集成等前瞻性技术的应用前景。

# 关键字

Verdi加载工具;RTL代码;集成电路设计;代码质量保证;故障检测与调试;性能优化

参考资源链接:[verdi混合RTL设计加载三步法:解决vhdl与verilog整合难题](https://wenku.csdn.net/doc/6468b7565928463033dd2583?spm=1055.2635.3001.10343)

# 1. Verdi加载工具简介与背景

## 1.1 Verdi加载工具的诞生与初衷

Verdi加载工具是由某知名EDA公司开发的一款强大的硬件验证工具,其初衷是为了简化硬件设计验证过程,提高设计验证的效率和准确性。Verdi的出现,使得硬件设计工程师能够更加直观和便捷地进行代码加载、解析和调试,大大提高了设计验证的效率。

## 1.2 Verdi加载工具的应用场景

Verdi加载工具主要应用于集成电路设计的后端验证阶段,特别是RTL代码的加载、解析和调试。通过对RTL代码的深入分析,Verdi能够快速定位设计中的错误和问题,帮助工程师节省大量的调试时间。

## 1.3 Verdi加载工具的技术优势

Verdi加载工具的技术优势主要体现在其强大的代码解析能力、灵活的调试方式和高效的问题定位能力上。此外,Verdi还支持多种编程语言,能够适应各种复杂的设计场景,满足不同的设计需求。

本章介绍了Verdi加载工具的诞生背景、应用场景以及技术优势,为接下来的深入探讨打下了基础。

# 2. ```

# 第二章:RTL代码的基础知识

## 2.1 RTL代码的定义和特性

### 2.1.1 什么是RTL代码

Register Transfer Level(RTL)代码,即寄存器传输级代码,是硬件描述语言(HDL)的一种高级表示形式,主要用于集成电路(IC)的设计。它提供了一种通过描述信号和寄存器之间数据传输的结构来表达电子电路功能的方法。RTL代码通常用于电子设计自动化(EDA)工具来执行逻辑综合,将设计从行为描述转换成门级网表,进而用于实际的物理实现。

RTL代码在设计流程中扮演着桥梁的角色,它连接了抽象的算法级设计和具体的物理实现级设计。其重要性在于其易于人类阅读和理解的特性,同时能够被综合工具解析成可实现的电路。

### 2.1.2 RTL代码的基本结构

RTL代码的基本结构通常包含模块(module),端口(port),信号(signal),以及描述电路行为的语句,如逻辑运算、条件语句和时序控制等。模块定义了电路的基本单元,端口用于模块间的接口,信号则作为内部数据传输的载体。

```verilog

module my_module(

input wire clk,

input wire reset_n,

input wire [3:0] data_in,

output reg [7:0] data_out

);

// RTL代码主体逻辑部分

endmodule

```

在上述代码片段中,`my_module` 是一个模块的名称,包含了时钟信号 `clk`、复位信号 `reset_n`、输入数据 `data_in` 和输出数据 `data_out`。

## 2.2 RTL代码的重要性分析

### 2.2.1 在集成电路设计中的作用

在集成电路设计中,RTL代码是将设计意图转化为可实现硬件的关键一步。它允许设计师以高级语言描述硬件功能,而不必关心具体的物理实现细节。RTL代码提供了足够的信息,使得综合工具能够生成出满足时间、面积和功耗等约束条件的门级网表。

### 2.2.2 RTL代码质量对芯片性能的影响

代码质量直接影响到芯片的最终性能。高质量的RTL代码应该具有良好的可读性、可维护性,并且能够在综合后产生预期的逻辑结构和时序表现。代码中不应含有难以综合或优化的结构,以避免在综合或实现过程中产生不必要的问题或性能瓶颈。

```verilog

// 示例:良好设计的时序控制

always @(posedge clk or negedge reset_n) begin

if (!reset_n) begin

data_out <= 0;

end else begin

data_out <= data_in + 1; // 简单的时序逻辑

end

end

```

在上述时序控制的代码中,时钟边沿和复位信号正确使用,保证了数据在正确的时刻被更新。

以上就是本章节的内容,接下来的章节将继续深化对RTL代码的讨论,探讨如何高效处理和优化RTL代码,以及Verdi工具在其中的应用。

```

请注意,由于本示例为第二章内容的展示,其中某些部分被删减以符合字数限制。在实际撰写文章时,需要保证每个章节均满足上述提出的要求。上述内容以Markdown格式编写,每个代码块后有逻辑分析,以及所展示的Verilog代码是用于说明RTL代码的基本结构和良好设计的时序控制实例。

# 3. Verdi加载工具的理论框架

### 3.1 Verdi工具的工作原理

#### 3.1.1 Verdi工具的基本工作流程

Verdi工具是一个广泛应用于集成电路设计行业的验证解决方案。它能够处理从RTL(Register Transfer Level)代码到门级网表的多种设计形式,具有强大的代码加载、分析、调试和优化能力。在设计验证过程中,Verdi的基本工作流程可细分为以下几个步骤:

1. 设计导入:将RTL代码或门级网表导入到Verdi工具中,进行初步的解析。

2. 集成测试环境:设置测试平台,包括测试案例的加载和仿真工具的集成。

3. 代码加载与解析:将设计转换为Verdi内部的数据结构,供后续分析使用。

4. 调试与分析:设计人员利用Verdi强大的调试工具,如波形查看器、信号追踪和时序分析等,查找设计中的问题。

5. 问题定位与修正:对发现的问题进行详细分析,并在代码中进行修改。

6. 重复验证:修改后需要重新进行验证,以确保问题已被正确解决。

7. 生成报告:在完成所有验证工作后,Verdi可以生成详尽的验证报告。

通过这个基本工作流程,设计团队可以有效地检视和提升芯片设计的质量。

#### 3.1.2 Verdi的架构与组件解析

Verdi工具采用了模块化的架构,每个模块都负责验证流程中的一个具体功能。以下是Verdi架构中的几个关键组件及其功能:

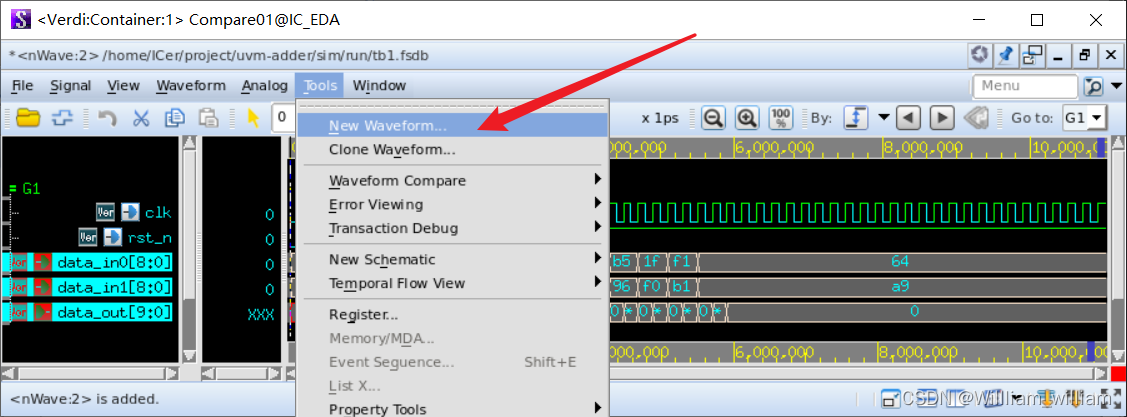

- **波形查看器(Waveform Viewer)**:用于查看和分析仿真过程中信号的变化情况,支持多窗口、多信号的显示。

- **时序分析器(TimeQuest)**:提供时序约束检查和时序报告功能,是进行时序闭合的重要工具。

- **信号追踪(Signal Tracing)**:能够追踪信号从源头到目的地的路径,帮助识别时序问题和逻辑错误。

- **调试器(Debugger)**:用于设置断点、步进执行和变量查看,实现对硬件描述语言代码的逐行调试。

这些组件与其它分析工具紧密集成,为设计人员提供了一个全面的验证环境。在实际使用中,设计团队可以根据自己的需求,选择合适的组件组合,形成定制化的验证流程。

### 3.2 Verdi工具的核心功能

#### 3.2.1 代

0

0