LPDDR4的电源管理:JESD209-4D标准影响下的优化策略

发布时间: 2024-12-17 16:05:29 阅读量: 3 订阅数: 6

参考资源链接:[JESD209-4D - LPDDR4](https://wenku.csdn.net/doc/53k2xuc4ts?spm=1055.2635.3001.10343)

# 1. LPDDR4技术概述及其重要性

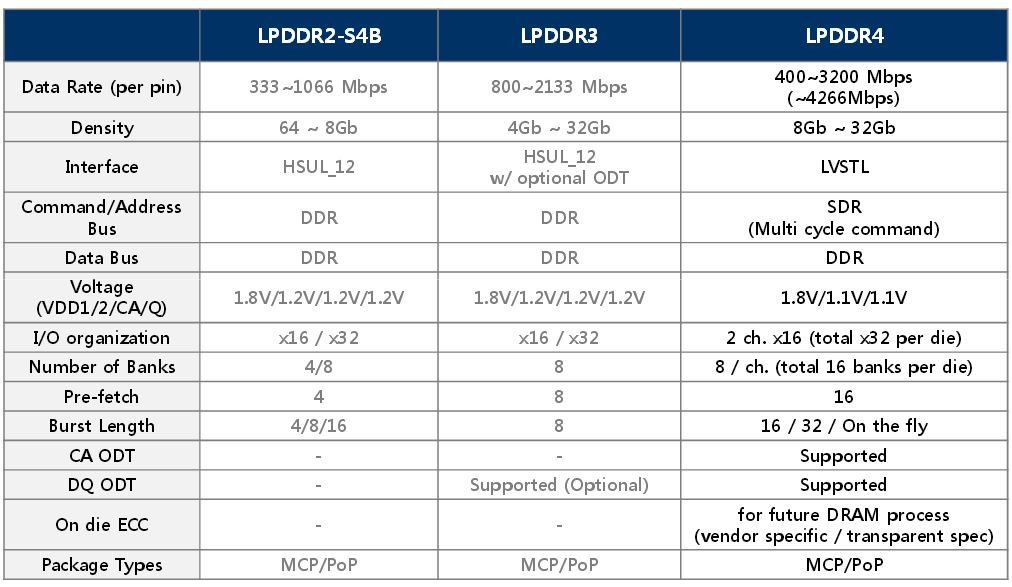

LPDDR4(Low Power Double Data Rate version 4)作为一种先进的内存技术,对现代移动计算设备和高性能计算应用具有至关重要的作用。相较于前代技术,LPDDR4具有更高的数据传输速率、更低的功耗和更优化的电源管理机制。这些特性使得LPDDR4成为智能手机、平板电脑、笔记本电脑以及嵌入式系统中不可或缺的核心组件。

随着移动互联网的快速发展,设备对内存的容量、速度以及功耗提出了更高的要求。LPDDR4技术的出现,既满足了对数据处理速度的需求,也极大提升了设备的电池使用效率,延长了设备的使用寿命,为移动用户带来了更好的使用体验。

本章将深入探讨LPDDR4的基本工作原理、关键性能指标以及它如何在不同的应用领域中发挥其关键作用,从而展示其在现代计算领域的突出重要性。

# 2. 电源管理的基本理论

在现代电子系统设计中,电源管理是实现高性能、高效率和低功耗的关键因素。随着移动设备、嵌入式系统和数据中心对能效的需求不断增长,电源管理技术的改进和优化显得尤为重要。本章将深入探讨电源管理的基本理论,包括其重要性、设计挑战、标准发展历程以及目前广泛采用的JESD209-4D标准要点。

## 2.1 电源管理的重要性与挑战

电源管理对系统的性能有着直接的影响。良好的电源管理能够延长电池寿命、降低热量生成、提高系统稳定性和可靠性。然而,在设计过程中,工程师们面临着众多挑战。

### 2.1.1 电源管理对系统性能的影响

电源管理技术的核心目标是确保电子设备在不同的工作模式下都能够获得合适的电力供应。这涉及到电压和电流的精确控制,以及在设备空闲时能够迅速进入低功耗状态。这对于延长电池寿命至关重要,尤其是在便携式设备中,如智能手机、平板电脑和笔记本电脑。然而,保证性能不降低的同时实现这一点是具有挑战性的。

### 2.1.2 设计挑战与当前解决方案

设计中的主要挑战之一是处理器和存储器的性能需求与电源供应之间需要达到一个平衡。例如,高性能计算任务需要高电流,但同时也会增加功耗。当前解决方案包括采用多层次电源管理策略,例如动态电压频率调整(DVFS),以及使用更高效的电源转换器和稳压器。

## 2.2 电源管理标准的发展历程

电源管理标准是随着技术的发展和行业需求的改变而进化的。了解这些标准的演变有助于深入理解当前电源管理实践的背景。

### 2.2.1 早期标准回顾

在LPDDR4和JESD209-4D标准出现之前,早期的电源管理标准主要集中在基本的电源转换和分配上。例如,早期的电源管理集成电路(PMIC)提供了电压调节功能,但并没有针对低功耗和高效率进行优化。

### 2.2.2 JESD209标准的演变

JEDEC固态技术协会发布的JESD209系列标准,特别是JESD209-4D,代表了电源管理技术的一大进步。这一标准详细规定了LPDDR4内存的电源管理要求,包括电源状态转换、电压调节和时钟管理等方面。

## 2.3 JESD209-4D标准要点解析

JESD209-4D标准为LPDDR4内存的电源管理设定了新的基准。本小节将解析该标准的核心规范及其对电源管理的影响。

### 2.3.1 标准核心规范

JESD209-4D标准定义了LPDDR4内存的电源状态、电压和时序要求。这些规范指导了设备制造商在设计电源管理解决方案时必须遵守的框架。

### 2.3.2 标准对电源管理的影响

该标准要求设备能够在不同的电源状态下灵活切换,以及在不牺牲性能的前提下进行高效的电源分配。这为电源管理硬件和软件的设计提供了新的机遇和挑战。

通过深入理解这些电源管理的基本理论,我们不仅能够更好地领会LPDDR4技术的重要性,而且能够为设计出更高效、更优化的电源管理方案奠定基础。在接下来的章节中,我们将探讨在JESD209-4D标准指导下的LPDDR4电源管理优化策略。

# 3. JESD209-4D标准下的LPDDR4电源管理优化策略

## 3.1 电源状态管理优化

### 3.1.1 低功耗状态的转换机制

LPDDR4在设计上引入了多种低功耗状态以优化电源管理,这些状态包括深度睡眠模式(Deep Sleep Mode)、待命状态(Power-Down)和部分阵列刷新模式(Partial Array Refresh)。低功耗状态的转换机制是关键所在,它确保了在不影响性能的前提下,尽可能地减少系统的能耗。

在JESD209-4D标准下,LPDDR4的低功耗状态转换机制被进一步优化。例如,当设备不再需要访问内存时,可以快速进入深度睡眠模式,此时,内存控制器和内存子系统会关闭所有未使用的部分,以最小化静态功耗。当有访问请求时,内存子系统能够迅速从深度睡眠状态唤醒,减少延迟时间。

### 3.1.2 动态电压频率调整(DVFS)策略

动态电压频率调整(DVFS)是一种有效的电源管理策略,通过动态调整处理器和内存的电压和频率来优化能效。在LPDDR4中,DVFS策略与电源状态管理紧密集成,以实现更细粒度的能耗控制。

DVFS策略在LPDDR4中采用两种主要方式实现:一是基于工作负载的变化动态调整工作频率和电压;二是利用内存的时序特性,允许在不影响性能的前提下,适当延长内存操作的时序。通过合理设置电压和频率的转换阈值,DVFS能够确保在满足性能需求的同时,减少不必要的能耗。

## 3.2 时钟管理优化

### 3.2.1 时钟门控技术

时钟门控技术是一种减少集成电路中未使用部分功耗的技术。在LPDDR4和JESD209-4D标准下,时钟门控技术被广泛应用于时钟域的动态管理。通过精确控制时钟信号的开启和关闭,可以有效避免无效的时钟切换,减少动态功耗。

例如,在LPDDR4设备中,当某个内存bank不在被访问时,相关的时钟信号可以被门控,从而在降低功耗的同时不会影响到其他正在运行的部分。这样的管理不仅减少了能耗,同时也减小了电磁干扰,提升了整体的信号完整性。

### 3.2.2 时钟树的优化方法

时钟树的优化是减少时钟网络功耗和改善信号完整性的关键手段。在LPDDR4中,通过精确的设计和分析时钟树,可以最小化时钟信号的skew(偏差)和jitter(抖动),保证在高频率下的稳定操作。

优化时钟树时,设计者通常会考虑到时钟网络的负载平衡、路径长度匹配等因素。一些时钟树优化技术,如自适应时钟补偿(ACC),可以帮助动态调整时钟信号,以应对在不同工作条件下的变化,例如温度波动和电源噪声。通过精心设计的时钟树优化,

0

0