LPDDR4内存控制器设计:JESD209-4D标准的硬件实现详解

发布时间: 2024-12-17 15:28:11 阅读量: 3 订阅数: 6

JESD209-4D, LPDDR4 JEDEC SPEC, June 1, 2021 最新版本。

参考资源链接:[JESD209-4D - LPDDR4](https://wenku.csdn.net/doc/53k2xuc4ts?spm=1055.2635.3001.10343)

# 1. LPDDR4内存控制器概述

LPDDR4内存控制器是现代移动计算设备中的关键组件,其设计旨在提升低功耗和高性能的内存访问能力。本章节将简要介绍LPDDR4内存控制器的定义、用途以及在现代系统架构中的角色。我们将探讨其性能参数,以及它如何满足日益增长的数据密集型应用需求。此章节为后续深入探讨LPDDR4内存控制器的技术细节和应用场景打下基础。

## 1.1 LPDDR4技术背景与发展

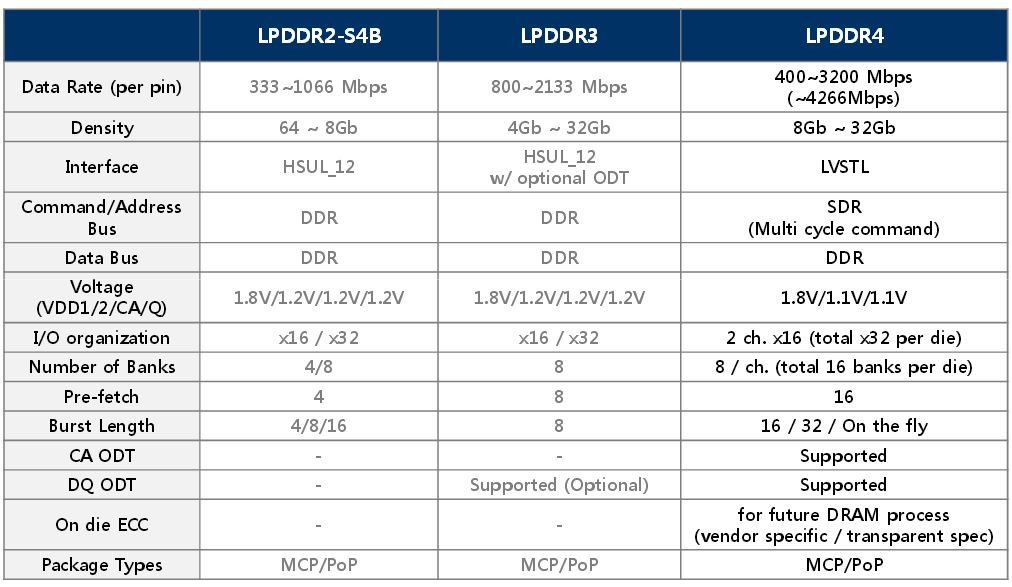

LPDDR4(Low Power Double Data Rate 4)是为了解决移动设备中功耗和速度的折衷而设计的内存标准。相较于之前的LPDDR版本,LPDDR4在数据传输速率和能效上有了显著的提升。

## 1.2 LPDDR4内存控制器的主要功能

控制器的主要功能是管理内存访问,保证数据的高速传输,同时最小化能耗。在硬件层面,LPDDR4内存控制器处理地址映射、命令生成和时序控制等任务。

## 1.3 LPDDR4内存控制器在系统中的地位

LPDDR4内存控制器位于处理器和内存模块之间,是连接这两者的桥梁。它确保了数据可以以最优化的方式在系统中流动,同时保持与设备其他组件的同步和兼容。

接下来的章节将更深入地探讨LPDDR4内存控制器的技术细节,包括遵循的JESD209-4D标准、硬件实现、软件协同以及实际应用案例和未来展望。

# 2. JESD209-4D标准的技术细节

### 2.1 JESD209-4D标准的核心特性

#### LPDDR4的性能提升要点

LPDDR4内存控制器带来的性能提升主要体现在以下几个方面:

- **速度提升**:LPDDR4通过采用更先进的数据传输技术,如16位数据传输,实现了更高的传输速率,相比较LPDDR3有明显的性能提升。

- **更低的功耗**:引入了多种节能模式,并且优化了电源管理技术,从而降低了操作时的功耗,延长了移动设备的电池寿命。

- **容量和密度提升**:LPDDR4内存能够提供更大的存储容量和更高的内存密度,满足了市场对于更高性能移动设备的需求。

#### 标准化的通信协议与接口

为了实现设备间的互操作性,JESD209-4D标准定义了严格的通信协议与接口:

- **统一的信号协议**:规范了信号传输的电压水平、时序参数以及接口协议,确保不同制造商生产的LPDDR4内存模块可以无缝集成。

- **高速接口**:采用DQ总线实现高速数据传输,支持更宽的数据带宽以适应高性能计算环境。

- **低功耗特性**:引入了多级功率管理特性,如低功耗自刷新(LPASR)技术,确保在待机状态下能够进一步降低功耗。

### 2.2 内存控制器的关键组件

#### 时序控制与数据路径设计

- **时序控制**:在内存控制器中,时序控制电路是确保数据同步和准确传输的关键。它通过精确的时间管理来保证数据在正确的时刻被读写。

- **数据路径设计**:数据路径的设计需要考虑信号完整性和传输延迟。合理的数据路径设计可以有效减少数据冲突和传输错误,提高整体的性能。

#### 电源管理技术与节能策略

电源管理是LPDDR4控制器设计中的重要组成部分,主要包含以下几个方面:

- **动态电源调节**:根据处理器的负载动态调整内存控制器的工作电压和频率,实现节能。

- **低功耗状态**:内存控制器能够进入多种低功耗状态,如深度休眠模式和待机模式,以便在不活动期间降低能耗。

- **功率门控技术**:在不需要时关闭部分电路的电源,减少静态功耗。

### 2.3 JESD209-4D兼容性要求

#### 设备与系统级的兼容性分析

JESD209-4D标准的设备级和系统级兼容性涉及多个方面:

- **设备间兼容性**:确保不同制造商的LPDDR4内存模块能够与各种处理器兼容。

- **系统级兼容性**:涉及操作系统、驱动程序和应用程序对LPDDR4的支持,以及这些组件之间的协同工作。

#### 测试与验证标准

为了保证LPDDR4内存控制器与系统的兼容性,JESD209-4D标准设定了严格的测试与验证标准:

- **协议一致性测试**:确保内存控制器的行为与JESD209-4D标准完全一致。

- **性能和稳定性测试**:评估内存控制器在各种条件下的性能和稳定性,确保在高温、高压等极端环境下也能正常工作。

为了保证内容的连贯性和深度,每个小节后将包含相应技术或概念的详细解释、图表、代码示例或mermaid流程图。在接下来的内容中,将深入探讨内存控制器硬件实现的各个方面。

# 3. LPDDR4内存控制器硬件实现

## 3.1 控制器硬件架构设计

### 3.1.1 架构组件与数据流

LPDDR4内存控制器的硬件架构设计是确保高效数据传输与处理的关键。架构由多个组件构成,包括数据缓冲器、命令生成器、时序控制器、接口模块等。数据流在这些组件间流动,以实现数据的读取、写入和刷新操作。

- **数据缓冲器**:负责临时存储正在传输的数据,以缓冲数据读写的速率差异。

- **命令生成器**:根据请求生成相应的命令,控制内存操作的流程。

- **时序控制器**:确保数据流在正确的时间点进入或离开控制器。

- **接口模块**:包括与内存颗粒连接的接口以及与CPU连接的接口,确保数据可以正确地在CPU和内存间传输。

数据流的优化直接影响LPDDR4内存控制器的性能,通常采用高速通道和先进的同步技术来减少延迟和提高传输速率。

### 3.1.2 控制器硬件接口规范

硬件接口规范定义了LPDDR4内存控制器与内存颗粒和CPU间的连接标准,包括电气特性和信号协议。为了支持LPDDR4的高速特性,硬件接口规

0

0