【网络处理流程的硬件加速】:Xilinx Tri-Mode MAC实例与分析

发布时间: 2024-12-28 20:08:46 阅读量: 4 订阅数: 7

Tri-mode_Ethernet_MAC.zip_ethphytestbench_mac ip核_tri-mode-ether

# 摘要

本文全面介绍了网络处理与硬件加速的结合点,特别是针对Xilinx Tri-Mode MAC核心的设计和实现进行了深入探讨。文章首先概述了网络处理与硬件加速的概念,接着详细阐述了Tri-Mode MAC核心的工作原理、架构特点及其在各种网络协议中的应用。进一步地,本文深入到Tri-Mode MAC的设计细节,包括硬件设计基础、硬件配置和性能优化策略,并通过实例与实践环节展示了如何搭建和测试该核心。最后,文章对Tri-Mode MAC在高速网络数据处理及新兴领域中的应用前景进行了展望,并讨论了未来硬件加速技术的发展趋势和可能遇到的挑战。

# 关键字

网络处理;硬件加速;Xilinx Tri-Mode MAC;硬件设计;性能优化;高速数据流

参考资源链接:[Xilinx Tri-Mode Ethernet MAC FPGA IP核设计指南](https://wenku.csdn.net/doc/52kcqurwqn?spm=1055.2635.3001.10343)

# 1. 网络处理与硬件加速概述

在当今数字化世界,数据通信是支撑我们生活和工作的重要基础。网络处理和硬件加速是现代信息系统的两大关键技术,它们在确保高速、安全和可靠的数据传输方面发挥着至关重要的作用。网络处理是指通过网络设备和软件对数据包进行分类、转发、控制等操作,保证数据能够正确、快速地从源头传送到目的地。而硬件加速则是利用特定设计的硬件来提高计算效率,尤其是在数据密集型和时间敏感性的场景下,比如数据中心、云计算以及通信系统中的网络加速器等。

## 1.1 网络处理的重要性

网络处理是任何数据通信系统的核心,它包括对数据包进行分析、转换和转发等操作。数据在网络中的快速流动需要高效的处理机制来确保实时性和可靠性。网络处理器(NPU)和网络加速卡(NIC)常用于优化网络处理性能,尤其是在处理复杂网络协议和大量数据流时,硬件加速显示出了显著的优势。

## 1.2 硬件加速的作用

硬件加速通过专用硬件电路,比如FPGA(Field-Programmable Gate Array)或ASIC(Application-Specific Integrated Circuit),实现对特定计算任务的加速。与通用CPU相比,硬件加速器能在特定操作上提供更高的性能和更低的延迟。这在处理大规模数据包、加密、压缩等网络功能时尤为重要。

## 1.3 网络处理与硬件加速的结合

网络处理和硬件加速的结合为现代网络系统带来了前所未有的性能提升。硬件加速技术在现代网络设备中的应用,如路由器、交换机和无线基站等,可以显著提升数据处理效率,减少网络拥塞,提升用户体验。在未来,随着网络需求的持续增长,两者结合的深度将进一步加深,为网络技术的创新和应用开辟新的路径。

网络处理与硬件加速的概述为理解后续章节打下了基础,这些章节将深入探讨Xilinx Tri-Mode MAC这一技术细节,以及在现代网络通信中的具体应用和优化方法。

# 2. Xilinx Tri-Mode MAC核心概念

## 2.1 MAC层的基础知识

### 2.1.1 MAC层的作用与功能

在计算机网络的OSI模型中,MAC(媒体访问控制)层位于数据链路层,负责控制数据如何在物理链路上进行传输。MAC层的主要作用是确保网络上的设备可以无冲突地发送和接收数据包,通过地址识别和访问控制等功能,维护网络通信的秩序。

MAC层的主要功能包括:

- **地址管理**:每块网络接口卡(NIC)都有一个全球唯一的MAC地址,用于在局域网内标识设备。

- **帧封装与解析**:在数据链路层,数据被封装成帧,并在接收端被解析出来。

- **流量控制**:MAC层负责流量控制,以避免因信息过载而导致的网络拥堵。

- **错误检测与纠正**:通过帧尾部的校验序列,检测数据传输过程中可能出现的错误。

- **信道访问控制**:在共享介质的网络中,如以太网,MAC层决定了设备如何获取访问信道的权限。

### 2.1.2 MAC地址的概念与管理

MAC地址也称为物理地址,它是一个48位(6字节)的地址,用于局域网内部设备的唯一识别。MAC地址由两部分组成:组织唯一标识符(OUI)和网络接口控制器指定的序列号。

在MAC地址管理中,以下几点值得注意:

- **静态配置**:通常在系统或网络设备的固件中手动设置MAC地址。

- **动态分配**:在某些网络环境中,如DHCP,可以动态分配MAC地址。

- **地址解析协议(ARP)**:将网络层的IP地址映射到MAC地址。

- **MAC地址过滤**:网络安全策略中常用,只允许特定的MAC地址访问网络资源。

## 2.2 Xilinx Tri-Mode MAC简介

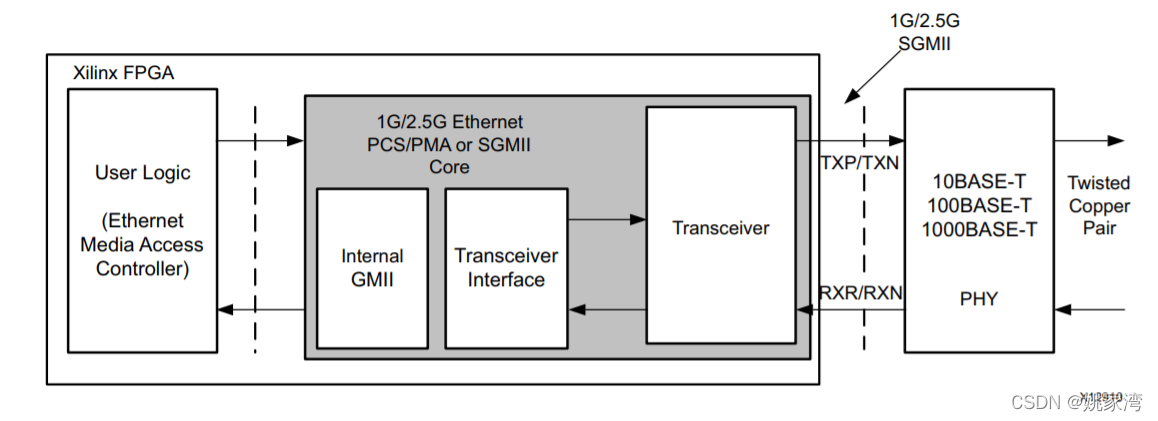

### 2.2.1 Tri-Mode MAC的架构特点

Xilinx Tri-Mode MAC是一种灵活的FPGA内嵌IP核,其设计允许它在三种不同标准的以太网环境中运行:10/100/1000 Mbps。Tri-Mode MAC的核心特点在于其可配置性,这使得设计者能够根据需要在10M、100M和1000M的速度之间切换,实现对多速率以太网的支持。

Tri-Mode MAC架构的关键特点包括:

- **可配置性**:能够配置为工作在多种速度模式下。

- **时钟恢复**:从接收信号中恢复时钟,以确保数据完整。

- **错误检测与处理**:能够检测和报告常见的网络错误。

- **高性能**:优化的数据吞吐率和处理能力。

- **流控制**:支持全双工和半双工操作,并包括对流量控制机制的支持。

### 2.2.2 硬件加速在Tri-Mode MAC中的应用

在Xilinx Tri-Mode MAC中,硬件加速是一个重要的概念。它指的是使用硬件逻辑来执行特定的处理任务,这比传统的软件处理要快得多。Tri-Mode MAC使用专用的硬件逻辑来处理一些以太网协议中的关键功能,如数据包的接收和发送、FIFO缓冲管理等,从而提升性能。

硬件加速的关键优势包括:

- **提升性能**:通过并行处理提高数据传输效率。

- **减少延迟**:硬件加速可以减少处理数据包的时间。

- **功耗优化**:在硬件层面完成任务,减少了CPU的负荷,从而降低功耗。

- **系统资源优化**:释放CPU资源,可以用于执行其他关键任务。

## 2.3 网络通信协议与硬件加速

### 2.3.1 以太网协议基础

以太网是一种局域网(LAN)技术,它是基于广播媒介的最广泛使用的网络技术之一。以太网规定了如何在共享媒介上进行数据传输,包括数据帧的结构、发送和接收的方式以及物理层和数据链路层的要求。

以太网的关键特性包括:

- **CSMA/CD协议**:载波侦听多路访问/冲突检测是早期以太网中用于防止冲突的技术。

- **帧结构**:以太网帧包含目的地址、源地址、类型、数据和校验码等字段。

- **速度标准**:从10 Mbps的原始以太网,发展到100 Mbps的快速以太网,再到1000 Mbps的千兆以太网。

### 2.3.2 硬件加速在不同网络协议中的角色

硬件加速不仅仅局限于以太网,在多种网络协议和应用场景中也扮演了关键角色。通过使用专用硬件执行复杂的数据处理任务,可以在保持高速率和低延迟的同时,保证网络服务质量。

硬件加速在不同网络协议中的应用包括:

- **TCP/IP处理**:在网络层和传输层,硬件加速用于优化TCP和IP数据包的处理。

- **SSL/TLS加速**:在安全连接中,通过专用硬件加速SSL/TLS加密和解密过程。

- **网络存储**:在SAN(存储区域网络)中,硬件加速用于提升数据在光纤通道上的传输速度。

以上便是第二章的详细内容。通过深入分析MAC层的基础知识、Xilinx Tri-Mode MAC的核心概念,以及网络通信协议与硬件加速的关系,读者可以全面理解MAC层在现代网络中的重要性,以及Xilinx Tri-Mode MAC如何利用硬件加速技术提升网络性能。在下一章中,我们将探讨Xilinx Tri-Mode MAC的设计与实现,继续深入硬件加速的应用和优化。

# 3. Xilinx Tri-Mode MAC的设计与实现

## 3.1 硬件设计基础

### 3.1.1 硬件描述语言与FPGA设计

在讨论Xilinx Tri-Mode MAC的设计之前,必须理解硬件描述语言(HDL)在FPGA设计中的核心地位。硬件描述语言,特别是Verilog和VHDL,允许设计师在

0

0