【大型FPGA设计中的Xilinx Tri-Mode MAC嵌入指南】:案例分析与实践

发布时间: 2024-12-28 19:33:52 阅读量: 5 订阅数: 7

Tri-mode_Ethernet_MAC.zip_ethphytestbench_mac ip核_tri-mode-ether

# 摘要

本文全面介绍了FPGA与Xilinx Tri-Mode MAC的原理、设计、实现和性能优化。首先概述了FPGA和Xilinx Tri-Mode MAC的基础知识,包括MAC协议、以太网帧结构、MAC地址以及Xilinx FPGA平台的特点和相关工具链。其次,详细阐述了Tri-Mode MAC IP核的架构、功能及配置选项。在设计与实现部分,讨论了IP核集成、硬件描述、高级特性的配置、功能验证与仿真方法。接着,文章重点分析了性能优化策略、实际案例、问题诊断与解决技巧。最后,展望了Tri-Mode MAC在大型FPGA设计中的应用前景,包括面临的挑战、未来发展方向以及在推广和教育方面的展望。本文旨在为设计者提供深入理解与应用Xilinx Tri-Mode MAC的参考。

# 关键字

FPGA;Xilinx Tri-Mode MAC;MAC协议;硬件描述语言;性能优化;案例分析;网络协议支持

参考资源链接:[Xilinx Tri-Mode Ethernet MAC FPGA IP核设计指南](https://wenku.csdn.net/doc/52kcqurwqn?spm=1055.2635.3001.10343)

# 1. FPGA与Xilinx Tri-Mode MAC概述

## 1.1 FPGA简介

在现代电子设计领域,现场可编程门阵列(FPGA)因其高度的灵活性和性能成为不可或缺的一部分。不同于传统的ASIC(专用集成电路)和微处理器,FPGA可以在制造后重新配置,以实现特定的应用需求。这种灵活性允许设计师对硬件电路进行编程,以执行复杂的逻辑操作和数据处理任务,而无需承担额外的硬件成本。

## 1.2 Xilinx公司的FPGA

Xilinx是FPGA技术的先驱和领导者,提供广泛的FPGA产品系列,包括Spartan系列、Artix系列、Kintex系列和Virtex系列等。Xilinx FPGA不仅提供了高性能的数字信号处理能力,还集成了丰富的存储资源、高速串行收发器和强大的逻辑单元,因此非常适合于需要高速数据处理能力的应用场景,比如网络通信、视频处理和云计算等。

## 1.3 Xilinx Tri-Mode MAC的作用

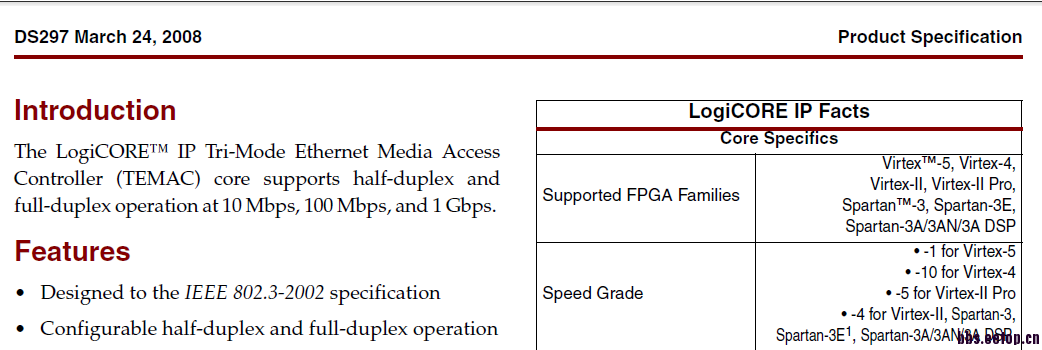

随着网络速度的不断提升,MAC(媒体访问控制)层的处理能力对整个系统的性能至关重要。Xilinx Tri-Mode MAC IP核是专为Xilinx FPGA设计的,它支持三种最广泛使用的以太网标准:10/100/1000 Mbps Ethernet,能够适应不断演进的网络技术。该核心模块不仅简化了设计流程,还大大缩短了产品上市时间,是网络通信设计不可或缺的一部分。

通过本章,我们将理解FPGA在现代电子设计中的核心地位,同时探讨Xilinx公司所提供的FPGA产品以及其在高速网络通信中应用的核心IP模块——Xilinx Tri-Mode MAC。这将为后续章节深入介绍该IP核的功能特性和设计实现奠定基础。

# 2. Xilinx Tri-Mode MAC的基础知识

## 2.1 MAC协议基础

### 2.1.1 MAC协议的工作原理

介质访问控制(Media Access Control,MAC)协议是数据链路层的一部分,负责控制网络上的设备如何接入物理介质进行数据传输。在以太网中,MAC层的主要任务是确保数据包能够正确地发送和接收,它通过以下方式来实现这一目标:

- **帧封装与解析**:将上层数据封装成以太网帧,并在接收端解析以太网帧。

- **碰撞检测与避免**:在早期的以太网标准中,如CSMA/CD(Carrier Sense Multiple Access with Collision Detection),MAC层通过监听信道来避免碰撞。

- **地址识别**:通过检查帧中的MAC地址来确认数据包是否应该被接收设备接收。

MAC地址是一种硬件地址,每个网卡设备出厂时都预设有一个唯一的地址,它用于在同一网络中唯一识别设备。在数据包传输过程中,源MAC地址和目的MAC地址的使用是关键环节。

### 2.1.2 以太网帧结构和MAC地址

以太网帧是数据链路层的数据封装单元,其结构定义了数据包的格式。一个标准的以太网帧包括以下部分:

- **前同步码和帧起始定界符**:用于同步帧的开始。

- **目的MAC地址和源MAC地址**:各占6个字节。

- **类型/长度字段**:指示上层协议或数据包长度。

- **数据载荷(payload)**:网络层传递下来的数据,其长度在46到1500字节之间。

- **帧校验序列(FCS)**:用于错误检测。

每个以太网设备都有一个48位长的MAC地址,由硬件制造商分配,并保证全球唯一。在网络中,当数据包到达一个设备时,该设备的MAC地址会被检查,只有当目的MAC地址与本设备地址匹配时,设备才会处理该数据包。

### 2.1.3 MAC协议的工作流程

以太网的MAC协议工作流程可以概括如下:

1. **帧发送**:当设备需要发送数据时,它会首先检测网络是否空闲。如果信道处于空闲状态,设备就可以发送数据帧。

2. **碰撞检测**:在共享介质的网络中,设备在发送数据的同时,还会监听信道,以检测是否有其他设备同时发送数据导致碰撞。如果发生碰撞,设备会等待一段时间后,再尝试发送。

3. **帧接收**:接收设备接收到数据帧后,会检查目的MAC地址是否与本设备地址匹配。如果匹配,接收设备将处理数据帧;如果错误,将丢弃数据帧。

## 2.2 Xilinx FPGA平台简介

### 2.2.1 Xilinx FPGA系列特点

Xilinx作为FPGA领域的主要厂商之一,提供了一系列特点鲜明的FPGA产品线,包括:

- **Virtex系列**:面向高性能计算和极端应用,提供丰富的逻辑单元和高性能内存接口。

- **Kintex系列**:针对成本敏感和功耗关键型应用设计,提供灵活的性能和价格平衡。

- **Artix系列**:主打低功耗、低成本的FPGA解决方案,适用于消费类和汽车电子等领域。

每一系列都根据其性能、容量、功耗和成本的不同而有不同的定位,满足不同市场的特定需求。

### 2.2.2 相关硬件资源和工具链

Xilinx FPGA的设计和开发需要依赖于一系列硬件资源和软件工具链:

- **硬件资源**:包括FPGA板卡、编程器/调试器、以及其他相关的开发和测试硬件。

- **软件工具链**:Xilinx提供Vivado设计套件,支持从逻辑设计、仿真、综合到布局布线和调试的全过程。此外,还有SDSoC开发环境,用于软件和硬件的协同设计。

在硬件方面,Xilinx还提供了一套适用于加速特定算法的平台,比如用于深度学习推理的Deep Neural Network Development Platform。

## 2.3 Tri-Mode MAC IP核特性

### 2.3.1 IP核架构和功能描述

Xilinx Tri-Mode MAC IP核是专为FPGA设计,支持以太网通信的MAC层功能。其架构和功能特点如下:

- **兼容性**:兼容IEEE 802.3标准,并支持全双工和半双工模式。

- **性能**:提供高达10Gbps的以太网吞吐量,适用于高带宽需求的应用场景。

- **接口**:支持多种接口标准,如GMII、RGMII、SGMII等,以适应不同的物理层设计。

Tri-Mode MAC IP核还支持多种高级特性,如流量控制、错误检测、统计信息收集等,可以提供丰

0

0