Xilinx Tri-Mode Ethernet MAC FPGA IP核设计指南

需积分: 15 89 浏览量

更新于2024-06-30

收藏 6MB PDF 举报

Xilinx Tri-Mode Ethernet MAC v9.0 是一款专为FPGA设计的LogiCORE IP核,它提供了灵活的以太网MAC功能,支持多种工作模式,适用于各种应用场合。这款产品是Vivado Design Suite的一部分,旨在帮助设计者在FPGA中实现高效且兼容的以太网通信。

核心概述:

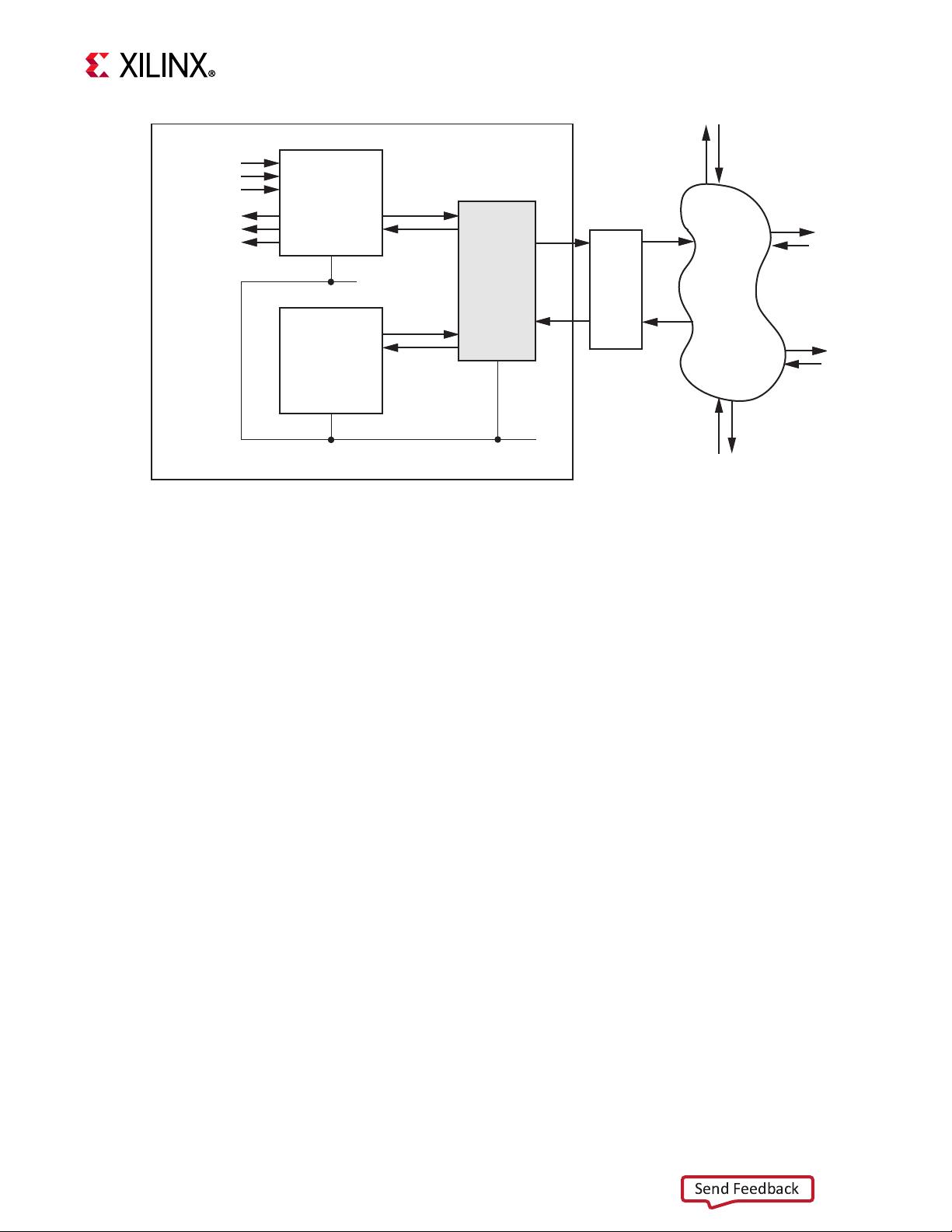

该MAC核提供了一个高度集成的解决方案,包括物理层(PHY)接口支持,能够适应7系列、Zynq-7000和UltraScale系列FPGA的不同架构。它支持三种工作模式:传统以太网模式、单速/全双工(10/100/1000Mbps)以及自动协商和流量控制(如IEEE 802.3az标准)。设计者可以根据项目需求灵活选择最适合的模式。

推荐设计经验:

对于初次使用该IP核的设计者,推荐有基础的FPGA开发经验和对以太网协议的了解,特别是AXI4-Stream接口的运用。此外,熟悉Xilinx Vivado工具链和逻辑综合、布线及仿真流程也是必要的。

产品规格:

- 标准支持:符合IEEE 802.3标准,包括10/100/1000Mbps和Auto Negotiation,以及可能的Advanced Vector Bridging (AVB) 功能。

- 性能指标:包括数据传输速率、最大帧长度、吞吐量和时延等参数,详细性能取决于具体FPGA平台。

- 资源利用:IP核占用的逻辑资源、存储器资源以及I/O引脚,设计者需要考虑这些限制以优化设计。

- 接口描述:包括主控接口(如AXI4-Stream)、配置和状态寄存器,以及可能的外部接口如PHY接口。

设计指南:

- 设计原则:共享逻辑模块可以提高效率,但需确保数据一致性;设计时应考虑不同设备的时钟和复位策略。

- 与PHY的交互:针对不同FPGA系列,IP提供不同的物理接口规范,确保正确连接和驱动PHY。

- 协议处理:详细解释了如何通过AXI4-Stream与上层处理器通信,以及如何处理802.3协议中的帧发送、接收和流量控制机制。

- 功能扩展:如使用优先级流控制、统计计数器以及帧过滤等高级特性。

配置和状态管理:

IP提供了一系列设置来配置MAC的行为,如TEMAC配置选项,以及用于监控MAC状态的寄存器。用户可以通过这些功能调整MAC的行为,满足特定应用的需求。

总结:

Xilinx Tri-Mode Ethernet MAC v9.0 IP核为FPGA设计者提供了一个强大且灵活的以太网MAC解决方案。通过深入理解其核心特性、设计指南和规格要求,设计者可以在FPGA中实现高效、稳定的以太网通信功能,适用于各种实时和嵌入式系统应用。使用Vivado Design Suite进行设计和集成,可以简化开发流程,提高设计质量。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

yb1010258369

- 粉丝: 1

- 资源: 3

最新资源

- 10天学会ASP.NET.pdf

- IBM内部PL1教材中文的

- 107条Javascript的常用语句.txt

- Visual C# 2005微软认证试题

- 一种摄像头自动白平衡的算法及硬件实现

- Linux 的引导过程.pdf

- EXTjs中文手册.pdf

- 你必须知道的.NET.pdf

- JDK5.0新特性介绍.pdf

- sed 使用手册linux unix 下常用的文本处理工具。用来处理格式化文本

- 卷积码的译码算法——维特比译码

- Oracle9i10g编程艺术

- MyEclipse 6 Java EE商业开发中文手册.pdf

- UML参考手册--基本概念

- strust2.0深入浅出

- 计算机专业毕业实习、毕业设计指导书