Linux内核中断处理机制:硬件到软件的完全路线图

发布时间: 2024-09-26 19:13:58 阅读量: 119 订阅数: 49

# 1. Linux内核中断处理机制概述

Linux内核作为操作系统的核心部分,其中断处理机制是保证系统响应外部事件和维持高效运行的关键。本章将概述Linux内核中断处理机制的基本概念和工作原理,为进一步深入研究提供基础。

中断处理机制允许计算机系统迅速响应外部或内部事件,从而提高程序执行的效率。在Linux内核中,中断主要分为硬件中断和软件中断。硬件中断由外部设备发出,通知CPU某个事件已经发生,例如按键操作或网络数据包的到达。软件中断则通常用于实现系统调用和服务请求。

由于中断处理需要在非常短的时间内完成,所以Linux内核采用了一种称为"中断线程化"的技术,将中断处理划分为上半部(top half)和下半部(bottom half)。上半部快速执行紧急任务,下半部则负责相对耗时的工作。这种设计实现了高效的任务处理,同时也降低了延迟。

本文将在接下来的章节中详细介绍硬件中断的基础知识、Linux内核中断管理的关键组件,以及软件层面的中断处理机制,并探讨在实践中的应用和性能优化策略。

# 2. 硬件中断的基本原理

## 2.1 中断的硬件基础

### 2.1.1 中断请求(IRQ)线的概念

中断请求(Interrupt Request,IRQ)是硬件设备与CPU通信的一种机制,用于通知CPU该设备需要处理器的服务。在传统的x86架构中,IRQ通过一组固定数量的物理引脚(或线)连接到中断控制器。这些IRQ线按照优先级从0到15编号,其中0代表最高优先级。

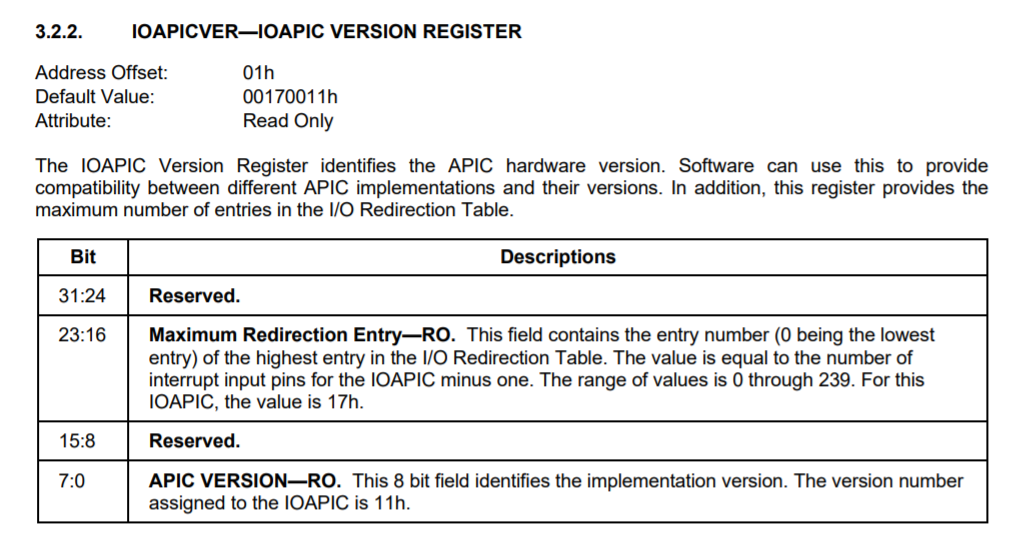

在现代计算机体系结构中,中断线可能由APIC(高级可编程中断控制器)管理,包括本地APIC(LAPIC)和I/O APIC。I/O APIC扩展了中断线的数量,允许更复杂的中断路由和处理。

### 2.1.2 中断控制器的作用和类型

中断控制器负责仲裁多个设备的中断请求,并决定何时将哪个设备的中断发送给CPU。它的工作是确保中断按预定的优先级顺序进行处理,以及在处理一个中断时,阻止或允许其他中断的介入。

中断控制器主要有两类:PIC(Programmable Interrupt Controller)和APIC。

- **PIC**:传统的PIC设计是为了管理最多8个中断源。当一个设备需要中断CPU时,它会发送一个信号到PIC的特定输入端口。PIC随后会向CPU发送一个中断信号,并在中断确认后发送一个IRQ号。PIC设计较为简单,但仅适用于中断源较少的情况。

- **APIC**:APIC分为本地APIC和I/O APIC。本地APIC是每个处理器核心自带的,用于处理本地中断;I/O APIC用于接收来自I/O设备的中断,并将它们路由到一个或多个本地APIC。APIC设计支持更复杂的中断系统,包括可扩展到数百个中断源。

## 2.2 中断的分类与触发机制

### 2.2.1 同步与异步中断的区别

中断可以分为同步中断和异步中断。

- **同步中断**(也称为内部中断或陷阱)是由当前执行的指令直接产生的中断。它们与CPU的执行流程是同步的。例如,执行一个系统调用指令或遇到一条非法操作码指令时,CPU将产生一个异常,这种中断的处理通常用于错误处理、任务调度等。

- **异步中断**(也称为外部中断)是由系统中其他组件(如I/O设备)独立于CPU当前执行的指令产生的。当一个硬件设备完成操作或需要CPU的服务时,它可以发起一个中断信号。CPU在完成当前指令后响应该中断信号。

### 2.2.2 中断的边缘触发和电平触发

中断信号的触发方式主要有两种:边缘触发和电平触发。

- **边缘触发**:这种触发方式下,中断仅在信号从低到高的跳变(即边缘)时被检测。这意味着中断控制器会检测到一次性的高电平变化,并将该变化解释为中断请求。这种方式的优点是中断不会因为持续的高电平而被重复检测,但缺点是可能会遗漏快速连续发生的中断信号。

- **电平触发**:在这种机制下,只要设备的信号线保持高电平状态,中断就会持续被请求。这种方式对于连续数据流中断处理非常有效,但如果高电平持续时间过长,可能会导致中断丢失或者竞争条件。

## 2.3 中断响应流程

### 2.3.1 CPU中断响应周期

当CPU收到一个中断请求后,它将进入一个中断响应周期,这个周期主要包含以下步骤:

1. **完成当前指令**:CPU在响应中断请求前,会先完成当前指令的执行。

2. **保存上下文**:CPU会将当前的程序状态保存到栈中,或者在某些架构中,保存到一个专门的寄存器集合中。这包括程序计数器(PC)、状态寄存器和其他关键的CPU寄存器。

3. **识别中断源**:CPU通过中断向量表或中断描述符表(IDT)来查找与中断号对应的处理程序入口地址。

4. **跳转到处理程序**:CPU使用找到的入口地址,跳转到相应的中断服务例程(ISR)开始处理中断。

5. **恢复上下文**:当中断处理完成后,CPU会恢复之前保存的程序状态,并返回到中断之前的位置继续执行。

### 2.3.2 中断优先级与嵌套处理

中断处理的过程中,可能会出现新的中断请求。在这种情况下,中断控制器会根据预设的优先级决定是否允许新的中断打断当前的处理流程,这个过程称为中断嵌套。

- **中断优先级**:通常由中断号决定,中断号小的优先级高。中断控制器使用这一机制来决定哪一个中断请求应当被首先处理。

- **中断嵌套**:在中断处理程序执行期间,如果一个更高优先级的中断发生,CPU会暂停当前的处理,并跳转去处理新的中断。处理完毕后,再返回之前中断的处理。

这种优先级和嵌套机制确保了对紧急和高优先级事件的即时响应,同时也要求中断处理程序要尽可能地短小和高效,以免阻塞其他中断太久。

在深入理解了硬件中断的基本原理之后,接下来我们将探讨Linux内核中的中断管理,以及它如何处理这些中断请求,实现高效和安全的中断服务。

# 3. Linux内核中的中断管理

Linux内核中的中断管理是操作系统响应外部事件的关键机制。内核必须能够高效地处理这些事件,同时不干扰系统的正常运行。在本章节中,我们将深入探讨Linux中断管理的核心组件,包括中断描述符表(IDT)、中断处理函数的注册与注销、以及中断上下文与任务管理的细节。

## 3.1 中断描述符表(IDT)

### 3.1.1 IDT的结构和功能

中断描述符表(IDT)是x86架构中用于中断和异常处理的主要数据结构。它类似于程序的调用门,存储了中断服务例程(ISR)的入口地址和描述符信息。当中断发生时,CPU会根据中断向量号,在IDT中查找相应的中断描述符,并通过描述符获取ISR的地址,进而执行中断处理代码。

IDT由8字节的门描述符组成,每个描述符可以是任务门、中断门或陷阱门。中断门和陷阱门分别用于处理中断和异常。当中断向量号确定后,CPU会将此号乘以8(因为每个IDT项的大小是8字节),然后将结果作为偏移量,在IDT表中找到对应的描述符。

### 3.1.2 中断门与陷阱门的实现

中断门(Interrupt Gate)和陷阱门(Trap Gate)是IDT中用到的两种类型的门。中断门通过清除IF标志,防止在当前中断处理函数执行期间发生新的可屏蔽中断。陷阱门类似于中断门,但不会清除IF标志,允许中断嵌套。

在Linux内核中,IDT的初始化主要通过`trap_init()`函数实现。该函数负责设置IDT的各个门,包括系统调用、定时器中断、以及其他硬件中断的处理。

```c

void __init trap_init(void)

{

// 初始化IDT的代码逻辑...

// 注册各种中断和异常处理函数的代码逻辑...

}

```

在注册中断处理函数时,内核使用`set_intr_gate`、`set_system_gate`等宏来设置中断门和陷阱门。这些宏使用汇编语言,因为需要对中断描

0

0