Verilog编码器故障诊断与排除:立即行动的10个紧急步骤

发布时间: 2024-12-15 12:07:03 订阅数: 4

基于FPGA的verilog实现8b-10b编码器包括testbench,包含仿真操作录像,中文注释

参考资源链接:[8-13编码器 verilog 实现 包含仿真图](https://wenku.csdn.net/doc/6412b78bbe7fbd1778d4aae4?spm=1055.2635.3001.10343)

# 1. Verilog编码器故障诊断概述

在数字电路设计中,Verilog编码器是一种重要的组件,它负责将多位二进制数据转换成一组有优先级的编码输出。本文将探讨Verilog编码器的故障诊断,分析其在设计、测试及部署过程中的问题诊断方法。我们将从理论基础出发,结合实际案例,深入探讨故障诊断的策略和技巧。目标是让读者不仅能理解故障诊断的基本概念,还能掌握实用的故障分析和解决方法。本文的内容将为那些希望提高Verilog编码器可靠性和性能的工程师们提供宝贵的指导。

# 2. 故障诊断前的理论准备

## 2.1 Verilog编码器基础

### 2.1.1 编码器的工作原理

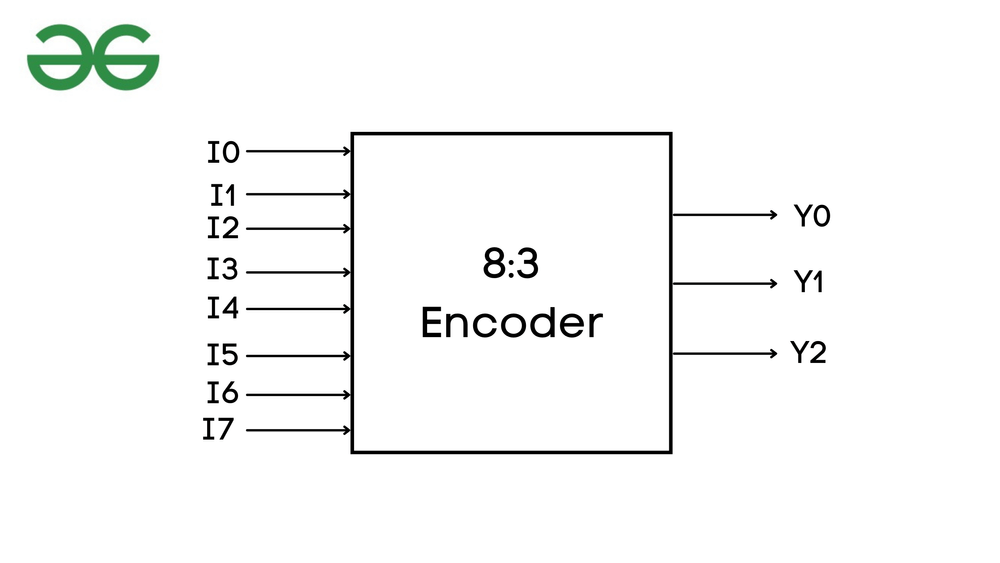

在数字逻辑设计中,编码器是一种将多个输入信号转换为一个输出信号的设备,通常是二进制码。编码器广泛应用于数字系统中,用于信号的编码、选择、分配和传输。典型的编码器有二进制编码器和优先级编码器等类型,它们的共同特点是将多个输入线路中的一个有效信号转换成相应的二进制或其它形式的编码。

编码器的工作原理可通过其逻辑功能来描述。以一个4-to-2二进制编码器为例,该编码器将四个输入线路中的有效信号编码成一个两位的二进制数输出。通常,编码器还有一个使能输入端,当使能端有效时,编码器才工作。当多个输入同时有效时,根据编码器的设计,有不同的优先级选择规则来确定输出。

### 2.1.2 Verilog编码器的组成与功能

在Verilog中设计编码器,通常要定义模块的行为和结构,包括输入和输出端口、内部逻辑及功能实现。Verilog编码器模块的基本组成有输入端口(input)、输出端口(output)以及可能的辅助信号,比如使能信号(enable)。其功能的实现依赖于Verilog语言提供的赋值语句、条件语句、循环语句等构造。

编码器模块的关键在于如何根据输入信号的状态确定输出信号的值。在实现过程中,可能需要使用case语句、if-else结构或者优先级编码的逻辑来完成编码功能。例如,使用case语句可以在一个时钟周期内检查输入端口的多个信号,并根据输入信号的优先级确定输出。

```verilog

module encoder(

input wire [3:0] in, // 4-bit input

input wire enable, // enable input

output reg [1:0] out // 2-bit output

);

always @(in or enable) begin

if (enable) begin

casez (in)

4'b1???: out = 2'b00;

4'b01??: out = 2'b01;

4'b001?: out = 2'b10;

4'b0001: out = 2'b11;

default: out = 2'b00; // default case if no input is high

endcase

end else begin

out = 2'b00; // no encoding when enable is low

end

end

endmodule

```

在上述Verilog代码中,`casez` 语句中的 `?` 符号代表 "不关心" 位,它允许我们忽略某些输入位。这使得一个优先级编码器能够根据其优先级规则来设置输出值。

## 2.2 故障诊断理论基础

### 2.2.1 故障模式与影响分析(FMEA)

故障模式与影响分析(Failure Modes and Effects Analysis,FMEA)是一种用于识别产品设计或制造过程中可能出现的故障模式,并评估这些故障模式对产品性能影响的方法。它是一种系统性的、定性的、预防性的分析工具,通过对产品设计和制造过程进行详尽的分析来预测故障,并指出需要采取措施以减轻故障风险。

在进行FMEA分析时,需要填写的表格通常包括以下列:故障模式、故障原因、故障影响、严重性(Severity)、频度(Occurrence)、检测性(Detection)、风险优先级(Risk Priority Number, RPN)。通过计算每个故障模式的RPN值,可以对故障进行排序,从而确定应该优先解决哪些问题。

### 2.2.2 故障树分析(FTA)

故障树分析(Fault Tree Analysis,FTA)是一种逻辑建模技术,用于系统地分析特定事件(通常指系统失效)发生的原因。在FTA中,顶层事件(top event)是研究的焦点,通过逻辑门(如AND、OR、NOT等)连接的各种底层事件和基本事件来表示可能导致顶层事件的路径。

构建故障树首先需要定义顶层事件,然后识别可能导致该事件发生的所有直接原因,并将其放入第一层逻辑门。继续这一过程,直到所有原因都被识别并纳入树中。最后,通过评估故障树中各个事件的概率和逻辑关系,可以确定顶层事件发生的概率。

FTA有助于发现系统设计中的薄弱环节,并对系统进行定量和定性的风险评估。通过识别可能的薄弱环节,工程师可以采取措施改进设计,从而提高系统的可靠性和安全性。

```mermaid

graph TD

A[Top Event: System Failure] --> B[Intermediate Event 1]

A --> C[Intermediate Event 2]

A --> D[Intermediate Event 3]

B --> E[Basic Event 1]

B --> F[Basic Event 2]

C --> G[Basic Event 3]

D --> H[Basic Event 4]

E --> I[External Factors]

F

```

0

0