Verilog编码器测试策略全解:确保设计质量的15个关键步骤

发布时间: 2024-12-15 11:27:48 阅读量: 2 订阅数: 4

8-Verilog HDL编码器与译码器设计.7z

参考资源链接:[8-13编码器 verilog 实现 包含仿真图](https://wenku.csdn.net/doc/6412b78bbe7fbd1778d4aae4?spm=1055.2635.3001.10343)

# 1. Verilog编码器测试策略概述

## 1.1 测试的重要性与目的

在数字设计领域,Verilog编码器是关键组成部分,其准确性和可靠性直接影响整个系统的性能。为了确保编码器按照预期工作,测试成为了不可或缺的一环。测试策略的设计旨在揭示潜在的设计缺陷,确保编码器在各种条件下的稳定性和性能。

## 1.2 测试流程的组成

一个全面的测试流程包括多个阶段,从基础的功能验证、性能分析到综合测试和硬件验证。各个阶段都有其独特的测试方法和技术,但它们共同的目标是保证编码器满足设计规范,能够在真实环境中可靠运行。

## 1.3 面临的挑战与应对措施

测试Verilog编码器面临多方面的挑战,包括复杂的环境模拟、多变的输入条件、以及性能瓶颈的诊断。通过使用高效的测试工具、合理设计测试用例、以及综合运用各种测试技术,可以有效地发现并解决这些问题。

# 2. ```

# 第二章:理论基础与测试准备

## 2.1 Verilog编码器的基本概念

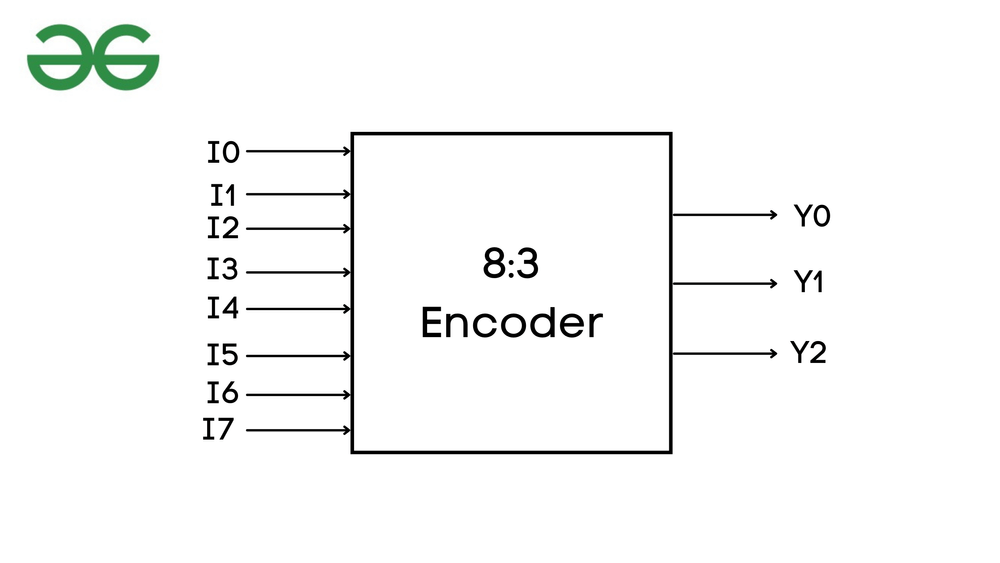

### 2.1.1 编码器的工作原理

编码器是一种将多个输入信号转换为少数输出信号的数字电路。在数字系统设计中,编码器通常用于数据通信、数据处理等领域,将多位二进制信息编码成一组较短的代码。在Verilog硬件描述语言中,编码器的实现往往涉及到逻辑门的组合,以及模块化编程的思想。

例如,一个简单的4到2编码器会接收4个输入信号,并输出两个二进制位表示输入的编号。如果输入信号0010,则输出将是01。

### 2.1.2 Verilog编码器的组成要素

Verilog编码器主要由以下部分组成:

- 输入端口:接收来自外部的输入信号。

- 逻辑电路:根据逻辑规则处理输入信号。

- 输出端口:输出转换后的代码。

在设计Verilog编码器时,需要特别注意信号的同步、状态的保持以及编码的唯一性,以确保编码器的稳定性和可靠性。

## 2.2 测试环境的搭建

### 2.2.1 测试平台的选择

选择适当的测试平台对于确保编码器设计的正确性和稳定性至关重要。常见的测试平台包括FPGA开发板和专用的硬件仿真平台。选择时需考虑以下因素:

- 性能:能否满足编码器设计对速度和容量的需求。

- 易用性:开发环境是否直观,是否易于部署和维护。

- 可扩展性:测试平台是否可以轻易地进行扩展或升级。

### 2.2.2 模拟器与仿真工具的配置

在编码器设计阶段,模拟器和仿真工具是不可或缺的。这些工具能够在编码器实现之前对其行为进行模拟,检测潜在的设计错误。例如,ModelSim是一款广泛使用的仿真工具,它提供了强大的波形查看和分析功能,有助于开发人员观察信号状态的变化。

在配置仿真工具时,需要确保:

- 正确安装和设置环境变量。

- 加载正确的库文件和模块。

- 设定模拟的时钟周期与测试周期。

## 2.3 测试用例的设计原则

### 2.3.1 覆盖率理论与实现

覆盖率理论是在软件测试中被广泛应用,以确保测试用例覆盖所有可能的代码路径。对于Verilog编码器,覆盖率分析可以指导测试用例的设计,确保验证过程中检查到所有设计的方面。覆盖率度量包括语句覆盖率、分支覆盖率、条件覆盖率等。

实现覆盖率分析通常需要:

- 选择合适的覆盖率工具。

- 生成覆盖率报告。

- 分析报告结果并调整测试用例。

### 2.3.2 测试用例的编写规范

为了编写有效的测试用例,需要遵循以下规范:

- 明确测试目标:确定测试用例需要验证的功能点。

- 设计详尽的测试场景:考虑边界情况、异常输入等。

- 定义预期结果:编写测试用例时,应明确每个场景的预期输出。

下面是一个简单的测试用例模板:

```verilog

module encoder_testbench;

// 测试信号声明

reg [3:0] inputs; // 输入信号

wire [1:0] outputs; // 输出信号

integer i;

// 实例化待测试的编码器模块

encoder uut (

.inputs(inputs),

.outputs(outputs)

);

// 测试用例的初始化和输入赋值

initial begin

// 初始化输入

inputs = 4'b0000;

// 遍历所有可能的输入情况

for (i = 0; i < 16; i = i + 1) begin

inputs = i; #10; // 更新输入,并等待10个时间单位

end

// 测试结束

$finish;

end

endmodule

```

上述代码展示了一个测试用例的基本结构,它会对一个4位输入的编码器进行测试,遍历所有可能的输入组合,并验证输出是否符合预期。在实际应用中,测试用例会更加复杂,涵盖更多的测试点和场景。

# 3. 功能验证与仿真测试

### 3.1 功能测试的关键步骤

功能测试是验证Verilog编码器设计是否符合预期行为的核心环节。此阶段的测试不仅涉及基本功能的正确性,还包括异常输入的处理能力和边界条件的测试。

#### 3.1.1 功能测试点的确定

在开始功能测试之前,需要明确Verilog编码器的核心功能点,这包括但不限于:

- 输入信号的有效性验证

- 编码结果的正确性

- 输出信号的时序要求

**核心功能点的细化示例:**

| 功能点编号 | 功能点描述 | 期望输出 |

|------------|--------------|------------|

| F01 | 输入信号为全0时输出特定编码 | 期望输出为预定义值 |

| F02 | 正常编码输入应得到正确的编码结果 | 验证输出是否与预期一致 |

| F03 | 输入信号变化时,输出信号应遵循时序规范 | 时序跟踪和分析 |

#### 3.1.2 测试向量的生成与应用

测试向量是功能测

```

0

0