CMOS IC设计:Razavi教材中的电路分析与设计挑战应对策略

发布时间: 2024-12-25 04:51:07 阅读量: 8 订阅数: 5

模拟CMOS集成电路设计(拉扎维)答案

# 摘要

随着集成电路技术的不断进步,CMOS(互补金属氧化物半导体)技术已成为集成电路设计领域的主流。本文综述了CMOS集成电路设计的基本理论、技巧以及面临的挑战。首先介绍了CMOS电路的基础理论,包括工作模式、逻辑门原理及性能参数分析。随后,根据Razavi教材深入探讨了多种CMOS电路设计模式和高级设计方法,并阐述了模拟与仿真工具的应用。第四章关注可靠性分析、射频与低功耗设计的挑战,以及尺寸缩减对设计的影响。第五章通过具体应用案例,展示了数字、模拟及混合信号CMOS电路设计的实际操作。最后,展望了CMOS IC设计未来的发展方向,包括新型技术、物联网与可穿戴设备的应用需求,以及设计师持续教育和成长的重要性。

# 关键字

CMOS集成电路;电路设计;性能参数;模拟仿真;可靠性分析;射频设计;低功耗技术;尺寸缩减;纳米工艺;SOI技术;物联网应用;教育与创新

参考资源链接:[拉扎维《微电子学基础》——CMOS IC设计入门](https://wenku.csdn.net/doc/6401abf9cce7214c316ea2d4?spm=1055.2635.3001.10343)

# 1. CMOS集成电路设计概述

## 1.1 CMOS集成电路简介

互补金属氧化物半导体(CMOS)集成电路技术作为当今微电子领域的核心技术之一,因其低功耗和高集成度的特性,在消费电子、通信、计算机及汽车电子等多个行业中扮演着关键角色。CMOS技术不仅涉及逻辑电路和存储器,还包括模拟和数字混合信号电路设计。

## 1.2 CMOS集成电路的重要性

CMOS集成电路的设计与制造是半导体产业的基础,其重要性体现在能够实现高效、复杂的逻辑运算和数据处理。随着技术的进步,CMOS集成电路正朝着更小的工艺节点、更高的集成度和更强的功能性发展,推动着电子产品的创新与智能化进程。

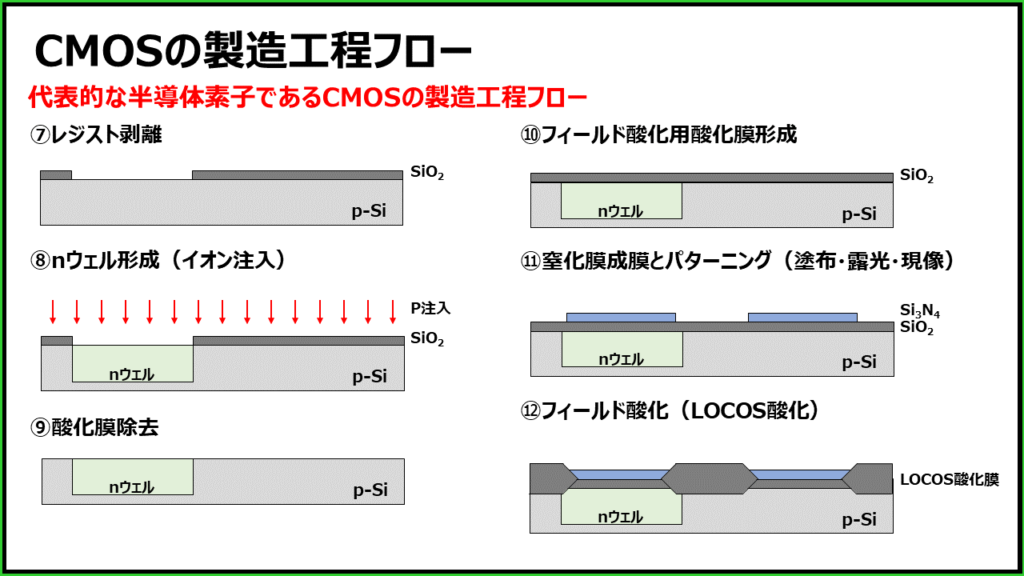

## 1.3 设计流程概述

CMOS集成电路设计流程复杂而精细,从概念的提出到最终的产品实现,需要经过电路设计、版图设计、仿真验证、掩膜制作、晶圆制造、封装测试等多个环节。整个设计流程需要设计师具备深厚的理论基础与实践经验,并且在特定的电子设计自动化(EDA)工具中实现。

# 2. CMOS电路基础理论

### 2.1 CMOS技术的基本原理

#### 2.1.1 CMOS晶体管的工作模式

CMOS晶体管由两种类型的场效应晶体管(FETs)组成,分别是P型(PMOS)和N型(NMOS)。它们的工作模式基于在栅极施加电压以控制源极和漏极之间的电流路径。PMOS晶体管在栅极电压低于阈值时导通,而NMOS晶体管在栅极电压高于阈值时导通。这一原理是构建CMOS逻辑门的基础,使得当输入逻辑电平从高变低时,一个晶体管将被关闭,而另一个则被开启,从而实现逻辑功能,同时消耗极小的静态电流。

```mermaid

graph TD

A[开始] --> B[应用电压到PMOS和NMOS栅极]

B --> C{PMOS导通条件}

C -->|Vgs低于阈值| D[PMOS导通]

C -->|Vgs高于阈值| E[PMOS截止]

B --> F{NMOS导通条件}

F -->|Vgs高于阈值| G[NMOS导通]

F -->|Vgs低于阈值| H[NMOS截止]

```

#### 2.1.2 CMOS逻辑门的工作原理

在CMOS技术中,逻辑门利用PMOS和NMOS晶体管的互补特性来实现逻辑功能。例如,一个简单的CMOS反相器包括一个上拉PMOS和一个下拉NMOS晶体管。当输入为高电平时,NMOS导通,PMOS截止,输出为低电平;当输入为低电平时,PMOS导通,NMOS截止,输出为高电平。这种设计确保了静态功耗最低,因为任何时候只有一个晶体管处于导通状态。

```mermaid

graph LR

A[输入高电平] -->|PMOS截止| B[NMOS导通]

B --> C[输出低电平]

A -->|NMOS导通| D[PMOS截止]

D --> C

E[输入低电平] -->|PMOS导通| F[NMOS截止]

F --> G[输出高电平]

E -->|NMOS截止| H[PMOS导通]

H --> G

```

### 2.2 CMOS电路的性能参数分析

#### 2.2.1 电压传输特性

电压传输特性(Voltage Transfer Characteristic, VTC)描述了CMOS逻辑门从输入电压到输出电压的转换关系。理想的VTC曲线具有高增益和陡峭的过渡区。在VTC图中,可以看到一个平滑的过渡区域,它表示在输入电压变化时输出电压响应的变化率。这一特性对于CMOS电路的信号完整性和噪声容限至关重要。

#### 2.2.2 功耗分析

CMOS电路的功耗可以分为静态功耗和动态功耗两部分。静态功耗发生在电路处于静态状态时,由于漏电流的存在而产生,相对较小。动态功耗是由电路中负载电容充放电造成的,在高速操作时占主要部分。动态功耗的计算公式为 `P = CL * V^2 * f`,其中 `CL` 是负载电容,`V` 是供电电压,`f` 是开关频率。

```python

# 动态功耗计算示例代码

def dynamic_power(CL, V, f):

return CL * V**2 * f

# 传入示例参数

capacitance = 1e-12 # 负载电容,单位法拉

voltage = 1.8 # 供电电压,单位伏特

frequency = 1e9 # 开关频率,单位赫兹

power = dynamic_power(capacitance, voltage, frequency)

print(f"动态功耗为: {power} 瓦特")

```

#### 2.2.3 速度与负载能力

CMOS电路的速度受到晶体管的开关速度和负载能力的限制。晶体管的开关速度取决于其跨导和负载电容。负载能力则涉及晶体管能够驱动的外部负载的大小。设计中需要优化晶体管尺寸和布局来平衡速度和负载能力,确保电路在满足性能要求的同时具有合理的功耗。

### 2.3 CMOS电路的噪声和稳定性

#### 2.3.1 噪声容限

噪声容限是指电路能够承受的最大噪声电压而不影响逻辑状态的能力。CMOS电路具有良好的噪声容限,这使得它在电气噪声和温度波动较大的环境中也能可靠工作。在电路设计中,需确保噪声容限高于预期的噪声水平。

#### 2.3.2 电源噪声和干扰

电源噪声和干扰是影响CMOS电路性能的常见问题。设计时需要考虑电源线和地线的布局,以减少干扰。同时,电源去耦电容的使用可以抑制高频噪声,提高电路的稳定性和抗干扰能力。

#### 2.3.3 电路稳定性分析

电路稳定性分析是确保CMOS电路在各种工作条件下都能可靠运行的关键步骤。稳定性分析包括检查电路对于工艺变化、温度变化和电源电压波动的响应。这通常涉及模拟仿真和极端条件测试,以确认电路的行为在设计规范之内。

通过本章节的介绍,读者应能够理解CMOS电路设计的基础理论和性能参数,以及如何分析和优化CMOS电路的噪声和稳定性。下一章节,我们将探讨Razavi教材中关于CMOS电路设计的高级技巧和实践方法。

# 3. Razavi教材中CMOS电路设计技巧

CMOS电路设计是一个不断演化的过程,它要求工程师不仅理解基本原理,还需要掌握各种高级设计技巧来应对现代电子系统的高性能要求。Razavi的教材《Design of Analog CMOS Integrated Circuits》是该领域的经典之作,其中介绍了许多实用的设计技巧和方法。在本章中,我们将深入探讨Razavi教材中提到的CMOS电路设计技巧,包括常用的电路设计模式、高级设计方法,以及模拟与仿真过程。

## 3.1 常用的CMOS电路设计模式

### 3.1.1 静态与动态逻辑设计

静态逻辑设计在CMOS电路中广泛使用,它具有较高的噪声容限和低功耗的特点。设计中常见的静态逻辑门包括与非门(NAND)、或非门(NOR)和反相器(Inverter),它们是构建复杂逻辑功能的基础模块。

动态逻辑设计利用电荷存储在节点上,通过电荷转移来实现逻辑运算。与静态逻辑相比,动态逻辑通常可以获得更快的操作速度和较小的芯片面积。然而,动态逻辑对时序要求更严格,并且对噪声较为敏感。典型的动态逻辑电路包括单相动态逻辑和双相动态逻辑。

**代码示例与逻辑分析:**

以下是一个简单的CMOS静态逻辑反相器设计示例:

```verilog

module cmos_inverter(

input wire vin, // 输入电压

output wire vout // 输出电压

);

// NMOS晶体管实例化

nMOS n1(.in(vin), .out(nmos_out));

// PMOS晶体管实例化

pMOS p1(.in(vin), .out(pmos_out));

// 输出逻辑

assign vout = nmos_out & ~pmos_out;

endmodule

// NMOS晶体管模型

module nMOS(

input wire in,

output wire out

);

// NMOS参数和实现逻辑

endmodule

// PMOS晶体管模型

module pMOS(

input wire in,

output wire out

);

// PMOS参数和实现逻辑

endmodule

```

### 3.1.2 传递门与传输晶体管逻辑

传递门逻辑利用NMOS和PMOS晶体管的组合来控制信号的传输,是实现复杂电路功能的关键技术。传递门能够有效地减少电

0

0