CMOS IC设计进阶必读:Razavi教材中的5大实用技巧全面解析

发布时间: 2024-12-25 04:10:58 阅读量: 5 订阅数: 3

# 摘要

本文全面覆盖了CMOS集成电路(IC)设计的各个方面,从基础理论到进阶技巧,再到实际案例的应用。首先概述了CMOS IC设计的基本概念,接着深入探讨了模拟和数字集成电路的基础知识,并分析了Razavi教材中的关键技术理论。第三章重点介绍了噪声分析、功耗管理和高频电路设计的实际技巧。进阶章节着重于高精度模拟电路设计、SoC集成以及创新技术的应用。最后,本文通过无线通信和VLSI设计的案例分析,深入讨论了设计验证、测试和故障分析。整体而言,本文为CMOS IC设计者提供了一个从理论到实践的完整学习路径,旨在提升设计效率和产品性能。

# 关键字

CMOS IC设计;模拟电路;数字电路;SoC集成;噪声优化;高频电路设计

参考资源链接:[拉扎维《微电子学基础》——CMOS IC设计入门](https://wenku.csdn.net/doc/6401abf9cce7214c316ea2d4?spm=1055.2635.3001.10343)

# 1. CMOS IC设计概述

CMOS IC(互补金属氧化物半导体集成电路)设计是现代电子工程的核心。在这一领域,设计者要处理复杂的物理、电气和逻辑问题,以构建高性能、低功耗的电路系统。本章将带您入门CMOS IC设计的世界,从基本概念讲起,逐渐深入到实践应用的各个层面。

## 1.1 CMOS技术发展简史

CMOS技术自20世纪60年代诞生以来,一直在推动集成电路的发展。它依赖于两种类型的晶体管:nMOS和pMOS,它们在电路中的工作是互补的,这一特性让CMOS芯片在功耗和性能方面表现卓越。

## 1.2 CMOS IC设计的范畴

设计CMOS IC不仅涉及电路图的绘制,还包括从系统规格到最终产品的全过程。设计者需要考虑的因素包括功耗、速度、可靠性、成本以及如何将电路集成到硅片上。

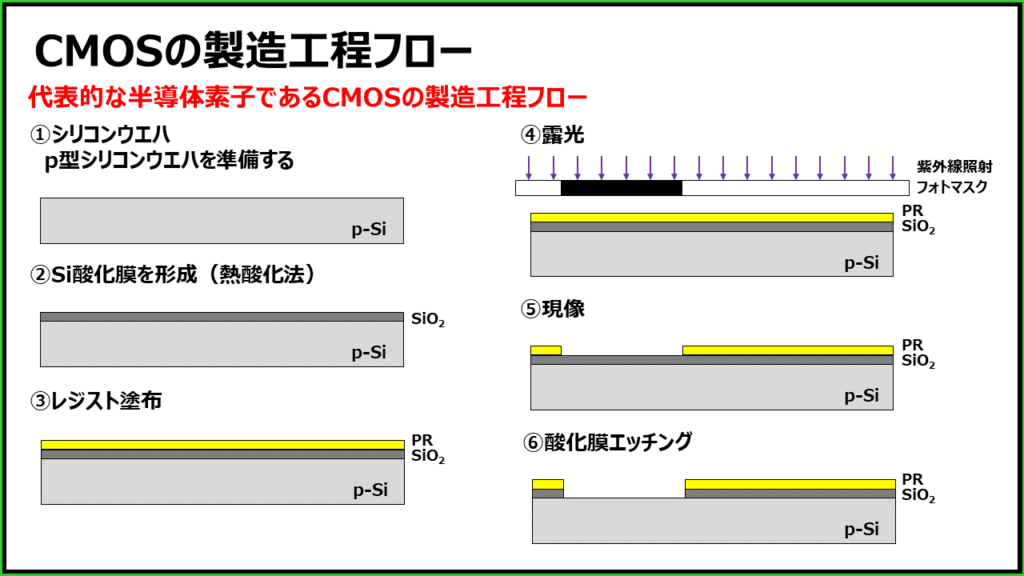

## 1.3 设计流程概述

一个典型的CMOS IC设计流程大致可以分为定义需求、电路设计、版图设计、验证和测试几个主要阶段。每个阶段对最终产品的质量都有决定性的影响。随后章节将详细介绍这些流程,指导读者深入了解CMOS IC的设计世界。

# 2. 深入理解Razavi教材中的基本理论

## 2.1 MOSFET器件物理

### 2.1.1 器件结构与工作原理

MOSFET(金属-氧化物-半导体场效应晶体管)是现代集成电路中应用最为广泛的器件之一。理解MOSFET的结构和工作原理是进行CMOS IC设计的基础。

MOSFET由四部分组成:源极(Source)、漏极(Drain)、栅极(Gate)和衬底(Substrate)。它的基本工作原理是通过栅极电压的变化来控制源极和漏极之间的导电通道的电阻,从而实现对电流的调制。

在NMOS器件中,栅极绝缘层上施加正电压会吸引电子,在栅极下方形成一个n型的反型层,从而形成一个导电通道。当源极和漏极之间施加电压时,电子通过这个通道从源极流向漏极。通过改变栅极电压的大小,可以控制导电通道的宽度,进而调节漏极电流的大小。

代码块:

```plaintext

MOSFET工作原理示意图:

+-----------------+ +-----------------+

| | | |

| Source |<---| Drain |

| | | |

+---------+-------+ +-------+---------+

| |

| |

+-------------------+

MOSFET Gate Insulator

```

栅极绝缘层的材质通常是二氧化硅(SiO2),确保了栅极电荷能够有效地控制导电通道。

### 2.1.2 MOSFET的非理想效应

在理想情况下,MOSFET工作时,漏极电流与栅极电压呈线性关系。但在实际情况中,由于各种非理想效应的存在,器件的性能会受到一定程度的影响。

非理想效应主要包括阈值电压变化、亚阈值导电、短沟道效应和热载流子效应等。

- 阈值电压变化:由于体效应和衬底偏置效应,阈值电压会随衬底电压的变化而变化。

- 亚阈值导电:当栅极电压低于阈值电压时,漏极电流并不会立即下降到零,而是会有一个缓慢下降的区域,这被称为亚阈值导电。

- 短沟道效应:随着沟道长度的缩短,阈值电压减小,漏极电流增大,造成控制性能下降。

- 热载流子效应:在漏极附近的高电场作用下,载流子速度接近饱和,产生大量高能电子和空穴,导致器件老化。

这些非理想效应对于电路设计者来说是一个巨大的挑战,必须通过各种设计技巧来克服它们,以确保电路的性能满足设计要求。

代码块:

```plaintext

// 非理想效应的简单模拟代码示例

// 在电路仿真软件中模拟MOSFET短沟道效应

// 参数设置

Vgs = ... // 栅极电压

Vds = ... // 漏极电压

Vbs = ... // 衬底电压

L = ... // 沟道长度

// 短沟道效应模拟

if (L < critical_length) {

Vt_shift = calculate_threshold_shift(Vbs);

Id = calculate_drain_current(Vgs, Vds, Vt_shift);

} else {

Id = calculate_drain_current(Vgs, Vds, Vt);

}

```

在上述代码示例中,我们首先设置了一些必要的参数,然后通过一个简单的条件判断来模拟短沟道效应,计算出阈值电压的变化,最终得到漏极电流的值。

通过上述分析和代码示例,我们能够对MOSFET的工作原理和非理想效应有一个更深入的理解。这将为我们在CMOS IC设计过程中遇到的相关问题提供理论基础和解决思路。

# 3. Razavi教材技巧实践应用

随着CMOS集成电路技术的不断发展,设计者在实践中需要掌握更深层次的设计技巧。本章节将深入探讨Razavi教材中提及的几种关键实践应用技巧,包括噪声分析与优化、功耗管理与效率提升、以及高频电路设计要点。

## 3.1 噪声分析与优化技巧

### 3.1.1 噪声的来源与模型

噪声是电路设计中的主要性能瓶颈之一,可能来源于多个方面,包括热噪声、闪烁噪声、电源噪声等。热噪声主要与温度和电阻有关,而闪烁噪声则与晶体管内部的载流子复合过程有关。电源噪声则往往由电源线上的电压波动造成。为了有效减少噪声对电路性能的影响,首先需要对噪声的来源有一个清晰的认识。

电路模型的建立是噪声分析的第一步。MOSFET的噪声模型包括沟道热噪声和闪烁噪声。沟道热噪声可以使用等效噪声电压和电流源来表示,而闪烁噪声则与MOSFET的栅漏电容和栅源电容有关。掌握这些基本模型对进行噪声分析至关重要。

### 3.1.2 噪声优化策略与实践

一旦识别了噪声的来源,接下来就是采取有效的优化策略。首先,可以通过设计适当的滤波电路来抑制某些特定频率的噪声。例如,使用低通滤波器或带通滤波器可以有效去除电源线上的高频噪声。

其次,优化晶体管尺寸和工作点可以减少闪烁噪声。此外,在电路设计中避免晶体管工作在截止区边缘,这样可以减少沟道热噪声。

在实际的电路设计中,可以使用一些电路仿真工具,如SPICE,进行噪声分析。以下是一个SPICE仿真中减少MOSFET噪声的简单示例代码块:

```spice

* SPICE deck to simulate noise in a MOSFET circuit

.include <model_file>.mod

M1 3 2 0 0 NMOS W=5u L=0.5u

Vgs 1 0 DC 1.5

Vds 3 1 DC 2.5

Rload 3 4 1k

.tran 1n 10u

.noise V(4) Vgs Vds

.end

```

通过这个示例,我们可以评估MOSFET在不同工作条件下的噪声表现,并通过改变MOSFET的W(宽度)和L(长度)参数来优化其噪声性能。参数分析之后,我们便能够找到合适的尺寸来减小噪声影响。

## 3.2 功耗管理与效率提升

### 3.2.1 功耗的基本概念与分类

功耗管理是当今集成电路设计中的一个重要议题,尤其对于移动设备和可穿戴技术来说更是如此。功耗可以分为静态功耗和动态功耗两大类。静态功耗主要是由于晶体管的泄漏电流造成的,而动态功耗则主要与信号切换频率和电路负载电容有关。

### 3.2.2 低功耗设计技巧与案例研究

为了实现低功耗设计,设计师通常会考虑多种策略。例如,可以使用多阈值电压晶体管(MTCMOS)技术来降低泄漏电流,也可以对电路进行时钟门控和电源门控优化,以降低不必要的功耗。

在设计时,考虑使用低功耗的电路架构也至关重要。例如,采用全差分结构和动态逻辑可以显著减少功耗。此外,合理设计电源网络,比如使用功率岛技术,可以有效地隔离各个部分的功耗,从而降低整体功耗。

接下来,我们将通过一个具体的案例来展示如何实施这些低功耗设计技巧。考虑一个典型的微处理器核心,其在不同运行模式下的功耗要求差异很大。为了优化功耗,设计者可以在处理器中集成多种电源管理策略,如动态电压频率调整(DVFS),以及根据不同的计算需求动态调节功率分配。

案例研究中涉及的代码或配置可能看起来像这样:

```vhdl

-- Example of a power management unit forDVFS in VHDL

architecture Behavioral of PMU is

signal voltage_level : integer range 0 to 3;

signal frequency_level : integer range 0 to 3;

begin

-- PMU controller process

process(system_clock)

begin

if rising_edge(system_clock) then

if cpu_demand_high then

voltage_level <= 3;

frequency_level <= 3;

elsif cpu_demand_medium then

voltage_level <= 2;

frequency_level <= 2;

else

voltage_level <= 1;

frequency_level <= 1;

end if;

end if;

end process;

end Behavioral;

```

在上述伪代码中,我们根据处理器的需求变化动态调整电压和频率,以实现功耗的优化。

## 3.3 高频电路设计要点

### 3.3.1 高频效应与电路布局

随着无线通信和数据速率的提升,高频电路设计成为了一个挑战。高频效应,如寄生电容、电感,以及趋肤效应等,对电路性能有着显著的影响。为了应对这些高频效应,电路布局时需要特别注意信号线的布线长度、信号回路以及避免相邻信号线之间的串扰。

### 3.3.2 信号完整性和阻抗匹配实例

为了保证信号完整性,阻抗匹配是一个关键的设计要点。在高频电路中,阻抗匹配问题尤为突出,不良的阻抗匹配会导致信号反射,从而降低信号传输效率和质量。

为了实现良好的阻抗匹配,电路设计者必须对传输线理论有深入的理解,并合理设置传输线的特性阻抗。通常,阻抗匹配可以通过调整传输线的物理尺寸或者使用匹配网络来实现。

举一个阻抗匹配的实例,以下是一个简单的L匹配网络示例:

```mermaid

graph TD

A[Input] --> B[L network]

B --> C[Output]

B -->|Controlled Impedance| D[Impedance matching]

```

在这个示例中,L匹配网络通过提供一个与源阻抗和负载阻抗相匹配的网络,来优化信号传输路径中的阻抗匹配。

针对阻抗匹配的设计,下面的代码块展示了如何使用SPICE进行阻抗匹配分析:

```spice

* SPICE simulation for impedance matching

.include <model_file>.mod

Rsource 1 2 50

Cmatch 2 3 1pF

Rload 3 0 100

Lmatch 2 3 1nH

.ac lin 100 100M 10GHz

.print ac im(Z(2,3))

.end

```

在这段代码中,我们通过分析节点2和3之间的阻抗来优化L匹配网络中的L和C元件的值。通过调整这些元件的值,我们最终能够实现源阻抗和负载阻抗的匹配,从而减少信号反射和损耗。

以上章节内容展示了Razavi教材中提及的实践应用技巧,并给出了具体的操作示例,帮助设计者们能够更好地理解和应用这些技巧。在下一章节中,我们将探讨更为高级的设计技巧,进一步深入CMOS IC设计领域。

# 4. CMOS IC设计进阶技巧解析

## 4.1 高精度模拟电路设计

在这一小节中,我们将深入探讨如何实现高精度模拟电路设计,特别是通过设计高性能的模数转换器(ADC)与数模转换器(DAC),以及如何打造低噪声放大器与滤波器。

### 4.1.1 模数转换器(ADC)与数模转换器(DAC)

在数字信息处理日益增长的需求下,模数转换器和数模转换器的性能直接关系到系统的整体表现。我们首先需要了解ADC和DAC的基本工作原理及其在CMOS工艺中的特殊实现挑战。

**模数转换器(ADC):**

- **工作原理:** ADC的核心是将模拟信号转换为数字信号。它的关键性能参数包括分辨率、采样率、信噪比(SNR)、有效位数(ENOB)和积分非线性(INL)等。

- **设计挑战:** 在CMOS工艺中,速度与精度通常是一对矛盾体。提高ADC的采样速率往往牺牲了精度,反之亦然。此外,热噪声、闪烁噪声和电源干扰也是实现高性能ADC时必须克服的问题。

**数模转换器(DAC):**

- **工作原理:** DAC的任务是将数字信号转换回模拟信号,其性能主要由分辨率、线性度、建立时间、微分非线性(DNL)和积分非线性(INL)等参数决定。

- **设计挑战:** 高精度DAC的难点在于稳定地生成接近理想模拟输出的电压或电流级别,同时减小来自数字逻辑的干扰。

### 代码块与逻辑分析

以一个简化的ADC设计为例,代码块展示了一个基本的二进制搜索型ADC的伪代码,用于说明设计流程。

```python

# ADC 二进制搜索型算法伪代码

def binary_search_adc(input_signal, reference, bits):

min_val = 0

max_val = 2**bits - 1

output = min_val

for i in range(bits):

mid_val = (min_val + max_val) // 2

if input_signal < reference[mid_val]:

max_val = mid_val

output = mid_val << (bits - i - 1)

else:

min_val = mid_val + 1

output = mid_val << (bits - i - 1) | (input_signal >= reference[mid_val + 1])

return output

reference = [2**i for i in range(10)] # 10位ADC的参考电压列表

input_signal = 789 # 输入模拟信号的数字等效值

bits = 10 # ADC位数

adc_output = binary_search_adc(input_signal, reference, bits)

```

在上述代码中,`binary_search_adc` 函数代表了一个使用二进制搜索算法实现的ADC。函数接收输入信号、参考电压列表和ADC位数作为参数,并通过迭代比较输入信号与参考电压,逐步缩小搜索范围,最终确定输出数字值。逻辑分析指出,这种算法的效率取决于搜索步骤的次数,而设计挑战在于参考电压的生成和稳定。

### 4.1.2 低噪声放大器与滤波器设计

为了确保信号在转换过程中不会丢失关键信息,电路中的噪声水平必须严格控制。低噪声放大器(LNA)和滤波器是降低系统噪声的关键组件。

**低噪声放大器(LNA):**

- **设计要点:** LNA的设计应尽可能降低噪声系数(NF),提高增益以及线性度。这通常要求细致的晶体管选择、偏置条件优化以及匹配网络的设计。

**滤波器设计:**

- **设计要点:** 滤波器旨在移除不需要的信号成分,例如电源或电路中产生的噪声。设计时要考虑滤波器类型(如低通、带通、高通、带阻)、阶数、截止频率以及在通带和阻带中的平坦度和过渡带宽度。

接下来,我们将展示一个简化的滤波器设计流程,并提供代码块来模拟滤波器的性能。

```python

import numpy as np

import matplotlib.pyplot as plt

from scipy.signal import butter, lfilter

# 设计一个简单的巴特沃斯低通滤波器

def butter_lowpass(cutoff, fs, order=5):

nyq = 0.5 * fs

normal_cutoff = cutoff / nyq

b, a = butter(order, normal_cutoff, btype='low', analog=False)

return b, a

def butter_lowpass_filter(data, cutoff, fs, order=5):

b, a = butter_lowpass(cutoff, fs, order=order)

y = lfilter(b, a, data)

return y

# 模拟参数

cutoff = 1000.0 # 截止频率 1 kHz

fs = 10000.0 # 采样率 10 kHz

data = np.random.randn(1000) # 随机数据

filtered_data = butter_lowpass_filter(data, cutoff, fs)

# 绘制滤波前后的数据

plt.figure()

plt.subplot(2, 1, 1)

plt.plot(data)

plt.title('Original Data')

plt.subplot(2, 1, 2)

plt.plot(filtered_data)

plt.title('Filtered Data')

plt.show()

```

代码块中,使用了Python的`scipy.signal`库来设计并模拟一个低通滤波器的性能。我们首先定义了`butter_lowpass`函数来生成滤波器的系数,然后用`butter_lowpass_filter`函数将滤波器应用于模拟信号。通过对比滤波前后的信号,我们可以评估滤波器的效果。代码块后面的逻辑分析指出,滤波器设计的关键在于选择合适的截止频率和阶数,以及考虑系统采样率对滤波器性能的影响。

以上内容,我们详细解析了高精度模拟电路设计中ADC和DAC的基本原理和设计挑战,以及低噪声放大器与滤波器的关键设计要点,提供了相应的代码和逻辑分析,以帮助读者更好地理解CMOS IC设计的进阶技巧。

# 5. CMOS IC设计案例分析与实战

在前几章中,我们已经深入了解了CMOS IC设计的基础理论、实践技巧以及一些进阶的设计方法。现在,让我们深入到实际案例中,分析并实战解决一些复杂而真实的设计问题。

## 5.1 无线通信芯片设计

### 5.1.1 无线通信系统的要求与挑战

无线通信芯片设计要求高度的集成度、低功耗以及高可靠性。这些要求来自于无线通信的特殊应用环境和用户对设备性能的不断追求。设计无线通信芯片面临的主要挑战包括:

- **频谱资源限制**:无线频谱是有限的,这就要求设计的芯片能够高效利用频谱资源,减少干扰。

- **功耗与性能的平衡**:移动设备对电池寿命有着严格的要求,同时还需要维持高性能的数据传输速率。

- **小型化与集成度**:随着便携式设备的流行,芯片设计需要考虑小型化,同时保持足够的集成度来实现复杂的功能。

### 5.1.2 关键电路的CMOS实现与优化

关键电路的设计直接关系到无线通信芯片的性能。一个典型的例子是RF前端的低噪声放大器(LNA)和混频器。在CMOS技术中实现这些电路,通常需要以下优化策略:

- **噪声优化**:利用适当的偏置技术减少热噪声,采用特殊的晶体管布局减少闪烁噪声。

- **线性度提升**:通过设计技术如共源共栅结构或负反馈来提升电路的线性度,以减小非线性失真。

- **阻抗匹配**:使用阻抗变换网络实现更好的阻抗匹配,从而减少信号反射和插入损失。

## 5.2 超大规模集成电路(VLSI)设计

### 5.2.1 VLSI设计的流程与技术

VLSI设计是一个高度复杂的过程,涉及到硬件描述语言(HDL)编程、逻辑综合、布局布线、时序分析等多个步骤。设计流程一般包括以下几个主要阶段:

- **需求分析和规格制定**:理解设计要求,制定芯片规格。

- **高层次综合(HLS)**:从高层次的算法描述转换成硬件描述。

- **逻辑综合与优化**:将HDL代码综合成门级网表,并进行优化。

- **布局布线**:物理设计过程,将逻辑门放置在芯片上并连接。

- **验证和测试**:确保设计满足功能和性能要求。

### 5.2.2 复杂系统设计案例分析

复杂的VLSI设计案例通常涉及数百万个晶体管,如处理器核心或高性能图形处理单元(GPU)。这里,我们分析一个高性能处理器核心的设计挑战:

- **功耗密度**:处理器的核心可能会产生大量的热量,因此需要优化功耗分布,同时实现有效的散热。

- **时钟树综合**:时钟信号需要均匀地分布在芯片上,同步各个部分的操作,这就要求优化时钟树设计来减少时钟偏差和功耗。

- **信号完整性**:高频操作下的信号干扰和串扰问题需要通过物理设计和布线策略来解决。

## 5.3 设计验证与测试

### 5.3.1 电路仿真与模型验证

在实际制造芯片之前,设计必须经过严格的仿真验证。使用仿真工具,如SPICE,可以在制造之前发现和修正设计中的错误。关键的仿真和验证步骤包括:

- **功能仿真**:验证电路按预期功能工作。

- **时序仿真**:分析电路在实际工作频率下的时序性能。

- **功耗分析**:对电路进行功耗仿真,预测其在不同工作条件下的功耗。

### 5.3.2 实物测试与故障分析

在电路仿真通过后,设计将进入原型制造阶段,这时需要进行实物测试。这一阶段的主要任务是验证实际电路与设计之间的匹配程度,并对可能的故障进行分析:

- **参数测试**:对芯片的电压、电流、频率等参数进行测试,确保它们在规定的范围内。

- **故障定位**:使用扫描链、边界扫描等测试方法,对芯片进行全面的故障定位。

- **故障仿真与优化**:根据测试结果进行故障仿真,调整设计来修复已发现的故障。

在本章中,我们通过案例分析的方式,深入探讨了无线通信芯片设计、VLSI设计流程、设计验证与测试的实战技巧。这些内容为CMOS IC设计提供了实践中的应用参考和优化方向,帮助IT和相关行业从业者提升设计能力。在下一章节,我们将继续探讨CMOS IC设计中的一些创新方法和未来技术的应用前景。

0

0