L-Edit版图设计的电源管理:优化PMOS版图的电源网络

发布时间: 2024-12-21 17:41:18 阅读量: 4 订阅数: 6

集成电路版图设计.docx

# 摘要

本文详细介绍了L-Edit版图设计中电源网络的概念与设计方法。首先,探讨了电源网络设计的基础知识,随后深入分析了PMOS晶体管在版图设计中的作用,包括其工作原理和性能特点。接下来,本文着重阐述了PMOS版图设计的关键参数,以及电源网络布局对电源管理策略的影响。此外,文章通过具体实践案例分析了L-Edit在电源网络设计中的应用,并提出了优化技巧。最后,讨论了先进工艺技术和软件发展对电源管理带来的挑战和未来趋势。本文旨在为版图设计工程师提供全面的指导,帮助他们优化电源网络设计,应对未来的技术变革。

# 关键字

版图设计;电源网络;PMOS晶体管;电源管理;L-Edit软件;优化技巧

参考资源链接:[L-Edit教程:PMOS版图设计与操作指南](https://wenku.csdn.net/doc/3m5dn2jr7a?spm=1055.2635.3001.10343)

# 1. L-Edit版图设计基础与电源网络概念

## 1.1 L-Edit版图设计基础

L-Edit是业界广泛使用的版图设计软件,它的应用贯穿于集成电路(IC)设计的每一个阶段。版图设计是将电路的逻辑设计转换为物理版图的过程。在进行版图设计时,需要考虑到电路的速度、面积、功耗以及电源的分配和管理。在实际操作中,设计者需要熟练掌握L-Edit的各种工具和功能,才能高效地完成设计任务。

## 1.2 电源网络的重要性

电源网络是版图设计中至关重要的一部分,它负责为集成电路提供稳定和有效的电源供给。电源网络设计的好坏直接关系到芯片的性能表现和可靠性。电源网络的布局必须仔细考虑,以确保电源的分配均匀,避免电源噪声和瞬时电压下降等问题。接下来的章节将深入探讨电源网络的多个方面,从电源网络的基础概念开始,逐渐深入到优化策略和实际应用案例。

# 2. PMOS晶体管在版图设计中的作用

## 2.1 PMOS晶体管的基本原理

### 2.1.1 PMOS的工作原理

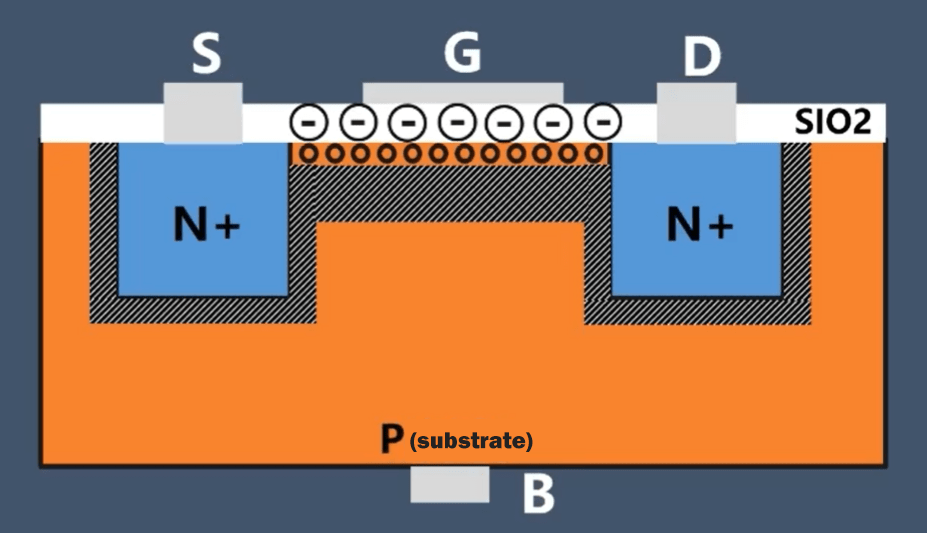

PMOS晶体管是一种在集成电路版图设计中广泛使用的场效应晶体管,其全称为P型金属氧化物半导体场效应晶体管。PMOS晶体管的工作原理基于电场控制导电沟道的产生和消失。在PMOS晶体管中,源极和漏极由P型半导体构成,而沟道区域则由N型半导体构成。晶体管的栅极由金属制成,并被一层氧化物绝缘层与沟道隔离。当栅极电压低于阈值电压时,由于负电压的排斥作用,P型半导体中的空穴会积累在栅极下方,形成一个低阻抗的P型导电沟道,此时电流可以在源极和漏极之间流动。当栅极电压高于阈值电压时,栅极附近的N型区域会形成一个电子积累层,这会阻挡P型导电沟道的形成,导致沟道关闭,阻止源极和漏极间的电流流动。

### 2.1.2 PMOS与NMOS的性能对比

为了完整理解PMOS晶体管在版图设计中的作用,我们有必要将其与另一种常见的晶体管——NMOS晶体管进行性能对比。NMOS晶体管的工作原理与PMOS类似,但其源极和漏极由N型半导体构成,而沟道区域由P型半导体构成。PMOS与NMOS的主要区别在于载流子类型以及开启电压的极性。NMOS晶体管中电流由电子构成,而PMOS中则由空穴构成,这导致了两者在性能参数上的差异,如载流子迁移率、阈值电压、以及开关速度等。

NMOS晶体管通常拥有比PMOS更高的电子迁移率,这意味着在相同条件下,NMOS的开关速度更快,功率效率更高。因此,在设计中,通常会优先使用NMOS晶体管以获得更好的性能。然而,在电源网络设计中,PMOS晶体管在实现某些特定电路功能时具有独特的优势,特别是在低功耗和高电压电路中。

## 2.2 PMOS版图设计的关键参数

### 2.2.1 通道长度与宽度的优化

在版图设计过程中,PMOS晶体管的通道长度(L)和宽度(W)是两个关键的尺寸参数,它们直接影响晶体管的电气性能。长度越短的通道,电子或空穴在通过沟道时遇到的电阻就越小,因此晶体管的开关速度就越快。同时,较短的通道长度可以减小晶体管的整体尺寸,增加集成电路的集成度。然而,过短的通道长度可能会引起严重的短沟道效应,从而影响晶体管的阈值电压和开关特性。

宽度的增加会使得更多的载流子可以并行流动,从而增加晶体管的电流驱动能力。但是,过大的晶体管宽度会导致晶体管占用过多的芯片面积,降低芯片的集成度。因此,在版图设计时,需要根据电路要求精心优化通道长度和宽度,以达到性能和空间的平衡。

### 2.2.2 阈值电压对性能的影响

阈值电压(Vth)是指晶体管从关闭状态转换到开启状态所需的最小栅极电压。合适的阈值电压对电路的稳定性和性能至关重要。如果阈值电压过低,晶体管可能会在非预期的条件下开启,导致漏电流增加,从而增加功耗。相反,如果阈值电压过高,晶体管开启所需的时间会延长,影响电路的开关速度。

在版图设计中,阈值电压通常通过掺杂浓度、栅介质材料和厚度以及栅极工作电压等因素进行控制。例如,可以通过增加N型掺杂来提高PMOS晶体管的阈值电压。在L-Edit等版图设计软件中,设计者可以通过调整晶体管结构参数来模拟和优化这些特性。

## 2.3 PMOS版图设计的电源管理策略

### 2.3.1 电源网络布局的影响因素

在集成电路版图设计中,电源网络布局是一个关键的因素,它决定了芯片内部各部分的供电质量和稳定性。良好的电源网络布局可以减少电源线上的阻抗和电压降,避免电源噪声对电路的干扰,从而确保电路的稳定工作。电源网络布局的影响因素包括电流分布、芯片的功率消耗、以及芯片的封装类型等。

电流分布的合理性对电源线的尺寸有直接影响。高电流密度区域需要较粗的电源线以减少电阻引起的压降。同时,为了避免功率损耗过大,设计时应尽量缩短电源线的长度。芯片的功率消耗不仅影响到电源网络的设计,还决定了芯片的热管理设计。高功率消耗往往需要更复杂的热管理解决方案,以确保芯片在正常工作温度下运行。此外,芯片的封装类型也决定了电源引脚的位置和数量,对电源网络布局有直接影响。

### 2

0

0