L-Edit版图设计的准确性保证:掌握DRC和LVS技巧

发布时间: 2024-12-21 17:26:25 阅读量: 4 订阅数: 6

AVR单片机项目-ADC键盘(源码+仿真+效果图).zip

# 摘要

L-Edit作为版图设计的常用工具,其版图设计的准确性和效率对集成电路设计至关重要。本文首先概述了L-Edit版图设计的基本流程和重要性,然后详细探讨了设计规则检查(DRC)和布局与验证(LVS)的关键步骤、常见问题以及准确性提升策略。文章进一步深入分析了版图设计优化技巧、参数化流程以及自动化和智能化的设计工具,最后通过实战演练环节,总结了版图设计项目规划和实施的实战经验,包括问题解决和设计准确性提升的方法。通过本文的深入分析与实践,旨在为版图设计工程师提供有价值的参考和指导,以达到提高设计质量与效率的目的。

# 关键字

L-Edit;版图设计;设计规则检查(DRC);布局与验证(LVS);版图优化;自动化设计

参考资源链接:[L-Edit教程:PMOS版图设计与操作指南](https://wenku.csdn.net/doc/3m5dn2jr7a?spm=1055.2635.3001.10343)

# 1. L-Edit版图设计概述

在现代集成电路设计中,版图设计是至关重要的一个环节。L-Edit作为一款专业的版图编辑软件,被广泛应用于微电子设计领域。它不仅仅是一款工具,更是一个艺术和科学结合的创作平台,允许设计者将电路理论转化为实际的物理布局。本章将概述L-Edit版图设计的基础知识,为后续章节关于设计规则检查(DRC)、布局与验证(LVS)以及版图设计技巧等的深入讨论打下基础。

## 1.1 版图设计在集成电路中的作用

版图设计是将电路设计转化为几何图形的过程,它不仅关系到芯片的性能,还直接影响到制造成本和最终产品的可靠性。一个精确的版图设计可以保证电路按照预期工作,同时减少制造过程中的错误和缺陷。

## 1.2 L-Edit版图设计的特点

L-Edit在版图设计方面的特点包括其强大的编辑功能、精确的图形操作以及丰富的设计验证工具。其直观的用户界面和高效的处理性能使得设计人员能够快速响应设计变更,缩短产品上市时间。

## 1.3 版图设计的基本流程

设计一个版图通常遵循以下基本流程:从电路设计原理图开始,规划出物理版图的大致布局,再利用L-Edit进行版图绘制和编辑,最后通过一系列的验证步骤确保设计的正确性。在整个流程中,版图设计人员需要兼顾电路性能、芯片面积以及制造工艺的约束条件。

# 2. 版图设计中的设计规则检查(DRC)

设计规则检查(Design Rule Check,DRC)是确保集成电路版图设计符合制造工艺要求的关键步骤。它涉及到大量的几何学计算和逻辑判断,目的是验证版图设计是否满足工艺制造中预设的一系列设计规则,从而确保芯片制造过程中的可靠性和成品率。

## 2.1 设计规则检查的基本概念

### 2.1.1 设计规则检查的目的与重要性

DRC的主要目的是发现版图设计中的那些可能导致制造失败的设计错误,例如线宽太细、间距不足、过度重叠等。这些错误在制造过程中可能导致断路、短路或器件性能不稳定。DRC的重要性体现在其能够保障产品的制造质量和可靠性,同时提高设计的生产效率,减少因版图错误导致的重复设计和制造。

### 2.1.2 设计规则的分类和示例

设计规则分为多种类型,主要包括:

- **几何规则**:规定了版图中线条、空间和区域的最小尺寸和间距。

- **连接规则**:规定了不同层之间连接的正确方式,例如通孔的尺寸和位置。

- **完整性规则**:确保设计中的所有部分都已正确连接,并无悬空的情况。

例如,在几何规则中,常见的有最小线宽规则,它要求在制造过程中,所有的导线宽度不能低于某个最小值,以确保导电性能和抗蚀刻能力。连接规则方面,通孔的尺寸和间距规则需要符合特定要求,以保证层间连接的可靠性和有效性。

## 2.2 设计规则检查的执行过程

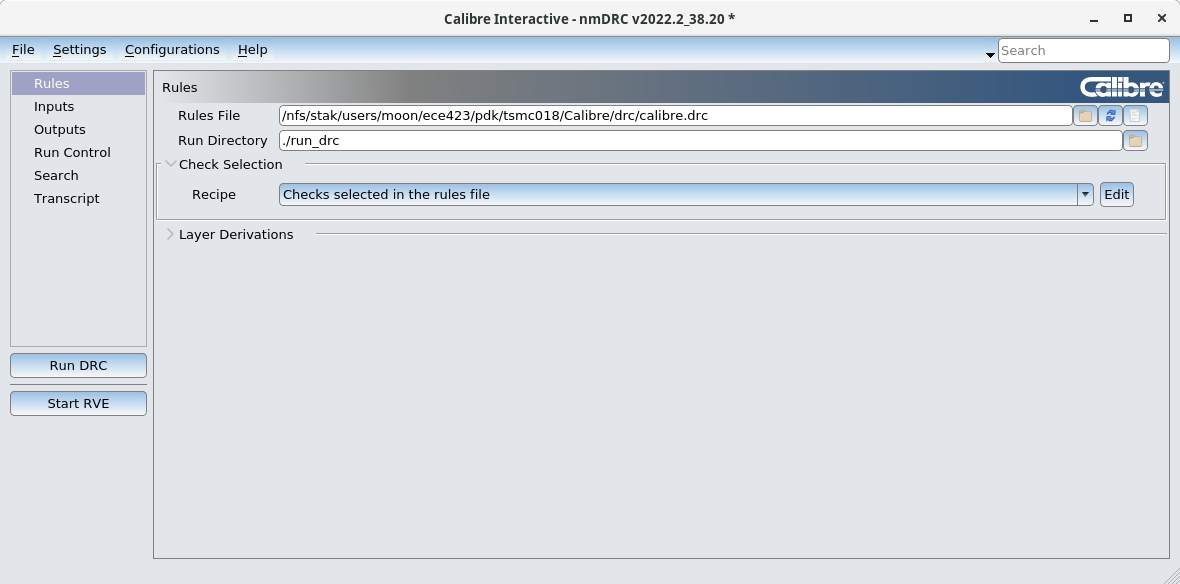

### 2.2.1 DRC流程详解

DRC的执行流程如下:

1. **规则加载**:将设计规则文件加载到DRC软件中。

2. **设计数据输入**:将版图设计数据导入到DRC工具中。

3. **检查执行**:运行DRC工具,根据规则文件对版图数据进行检查。

4. **结果输出**:生成包含所有DRC错误的报告文件。

5. **错误分析与修正**:分析错误报告,修正版图中的问题。

6. **复查**:再次执行DRC检查,确认所有错误已经修正。

### 2.2.2 DRC检查中的常见问题及解析

在DRC过程中可能会遇到各种问题,例如:

- **规则不匹配**:设计师使用的规则文件与实际制造工艺不匹配。

- **误报**:工具错误地识别版图特征为违规。

- **漏报**:未检测到实际存在的版图设计问题。

解析这些问题需要设计师对版图设计有深入的理解,并对制造工艺有足够的认识,以便能够合理解释DRC工具的报告结果,从而进行有效的版图修改。

## 2.3 提升设计规则检查的准确性

### 2.3.1 DRC规则的定制与优化

由于不同制造厂商和工艺节点有其特殊的设计要求,定制化DRC规则非常必要。设计师需要根据实际的制造工艺需求来调整DRC规则,以提高规则的适用性和检查的准确性。优化DRC规则可能包括添加特殊的设计考虑,调整参数容忍度等。

### 2.3.2 结合实际案例分析DRC问题

在实际的设计过程中,设计师可能会遇到多种复杂情况。分析这些案例能够帮助设计师深入理解DRC的应用,例如:

- 案例一:在处理一个深亚微米工艺节点的版图设计时,线宽和间距的限制变得非常严格,设计师如何调整版图布局以满足这些要求?

- 案例二:在进行跨层连接时,如何设置通孔位置,保证连接的可靠性,同时避免DRC误报?

通过分析具体案例,设计师能够更好地把握DRC的执行细节,提高设计的整体质量。

在这一章节中,我们深入探讨了设计规则检查(DRC)的基础知识、执行流程、常见问题以及提升DRC准确性的方法。DRC是版图设计中不可或缺的一环,涉及的细节非常丰富。在下一章节中,我们将继续深入了解版图设计中的布局与验证(LVS),探索其理论基础和实际操作,并分享提升准确性的策略。

# 3. 版图设计中的布局与验证(LVS)

## 3.1 布局与验证的理论基础

### 3.1.1 LVS的工作原理和目标

布局与验证(Layout Versus Schematic,简称LVS)是版图设计中的关键步骤,目的在于确保版图设计与电路设计原理图的一致性。通过LVS验证,可以发现版图中的错误,这些错误可能会导致电路在实际制造过程中出现不一致,从而影响产品的功能和性能。

工作原理上,LVS工具通过比较电路原理图(Schematic)和相应的版图(Layout)提取出来的电路,检查两者之间是否存在结构上的差异。这一过程通常包括以下步骤:

1. 提取版图中的电路结构,并将其转化为一种中间格

0

0