高速BISS-C编码器接口的FPGA应用:技术优化与性能提升

发布时间: 2024-12-15 02:54:26 阅读量: 11 订阅数: 9

参考资源链接:[FPGA实现的BISS-C协议编码器接口技术详解及解码仿真](https://wenku.csdn.net/doc/6471c28dd12cbe7ec301c4a4?spm=1055.2635.3001.10343)

# 1. 高速BISS-C编码器接口概述

在信息技术的浪潮中,BISS-C编码器作为一种高精度的位置传感器编码器,广泛应用于工业自动化、机器人技术和精密测量等领域。BISS-C(Binary Synchronous Serial Communication)接口因其高速、高效和同步的特点,在现代电子系统中扮演着至关重要的角色。本章将围绕BISS-C编码器接口进行概述,介绍其基本概念、工作原理以及应用领域。

## 1.1 BISS-C编码器的工作原理

BISS-C编码器是一种基于串行通信协议的编码器,它通过特定的数据格式和同步机制,实现编码器与控制器之间的高速数据传输。编码器在旋转或直线移动过程中,将其位置转换成数字信号,通过BISS-C接口进行数据打包,并按照预定的波特率发送。

## 1.2 BISS-C接口的优势与应用

与传统的并行通信接口相比,BISS-C接口以其更低的布线成本和更长的传输距离获得了行业内的青睐。它支持双向同步通信,能够有效减少数据传输错误,并提高系统的整体响应速度。BISS-C编码器接口在高速数据采集系统、高精度定位控制和遥测领域中表现出色。

本章旨在为读者提供BISS-C编码器接口的基础知识,为后续章节中介绍的FPGA接口设计和性能优化等内容打下基础。

# 2. FPGA基础及其在接口设计中的作用

## 2.1 FPGA技术简介

### 2.1.1 FPGA的基本原理和优势

FPGA(现场可编程门阵列)是一种通过编程来配置的半导体器件。区别于传统集成电路(IC)在制造过程中定义逻辑功能,FPGA允许用户在交付给最终用户之前,通过编程来定义其功能。这一特性使得FPGA在产品迭代、原型设计和小批量生产中显示出巨大的灵活性和优势。

FPGA主要由可编程逻辑块、可编程输入输出单元和可编程互连组成。逻辑块可以根据需要配置为各种复杂的组合逻辑或时序逻辑,而互连则负责逻辑块之间的信号传递。FPGA的可编程特性得益于存储在其配置存储器中的位流数据,这些数据定义了逻辑块的功能和互连方式。

FPGA的关键优势在于其高性能、可重配置性和并行处理能力。由于其内部结构的可定制性,FPGA可以在特定应用中进行优化,实现硬件加速。这与基于软件的处理器相比,可以提供更低的延迟和更高的吞吐量。同时,FPGA的并行性使其能够执行多个计算任务,而不会像串行处理器那样存在瓶颈。

### 2.1.2 FPGA在接口设计中的典型应用场景

FPGA在接口设计中的应用场景广泛,尤其是在要求高速数据传输和实时处理的场合。例如,在高速通信接口如PCI Express、SATA、HDMI等的实现中,FPGA可以提供所需的信号完整性、时序控制和协议实现。此外,FPGA也被广泛用于模拟器、测试设备、数据采集系统、图像处理以及自定义处理器设计中。

由于FPGA能够实时处理数据并做出快速决策,它在实时数据采集和处理系统中扮演了重要角色。在某些应用中,如雷达信号处理和基因测序,FPGA可以处理大量数据,快速实现复杂的算法,这样既提高了性能,又保持了设计的灵活性。

## 2.2 BISS-C编码器接口的硬件要求

### 2.2.1 BISS-C编码器的通信协议解析

BISS-C(Basic Interface for Sensors and Actuators, Class C)是一种用于传感器和执行器的接口标准,用于替代早期的BISS接口。BISS-C编码器提供了一个标准化的方法来传输位置、速度、温度或其他模拟量传感器的测量值。该协议是通过串行通信进行数据传输,支持全双工通信和距离较远的数据传输。

BISS-C协议主要采用NRZ编码方式,支持两种工作模式:主模式和从模式。在主模式下,BISS-C编码器可以接收命令并发送数据;在从模式下,它仅负责数据的发送。在数据帧结构上,BISS-C协议定义了起始位、地址位、数据位、奇偶校验位以及停止位,以确保数据的准确传输。

### 2.2.2 硬件设计要点

硬件设计时需要考虑的关键要点包括信号的完整性、电源设计、时钟同步和防干扰措施。信号完整性是指保证高速数据在传输路径中不失真的能力,这需要精心设计信号走线,使用匹配电阻和终结器,以及确保良好的电源和地平面布局。

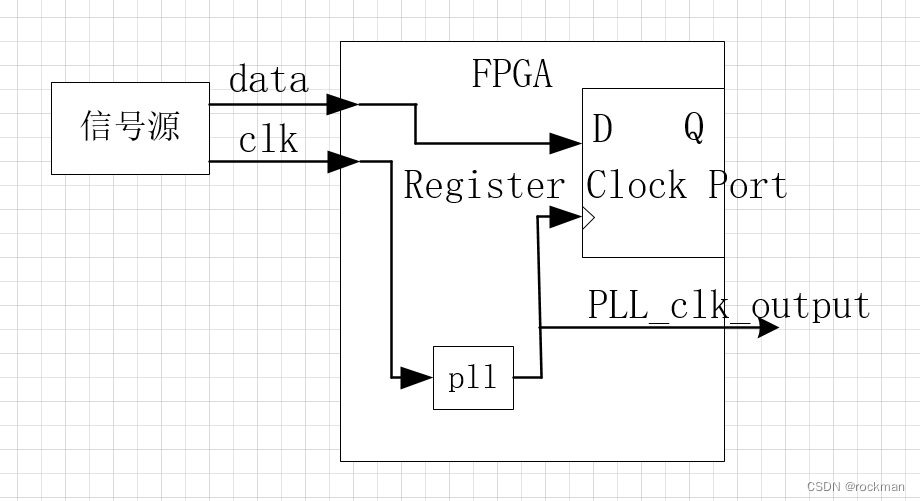

电源设计需要考虑FPGA和BISS-C编码器的供电要求,可能包括多个电源域和电压级别。时钟同步则涉及到为FPGA提供稳定且精确的时钟信号,以保证数据在接口中的同步传输。在设计时,通常会使用PLL(相位锁定环)来生成所需的时钟频率。

为了减少噪声对信号的干扰,硬件设计还需要包括电磁兼容(EMC)措施,如合理布局信号线、使用屏蔽和接地,以及考虑高速电路的信号回流路径。

## 2.3 FPGA与BISS-C接口的对接方案

### 2.3.1 接口电路设计

对接方案的第一步是设计一个能够满足BISS-C接口要求的电路。这需要考虑电气连接、信号电平转换、接口保护和电源管理。电气连接需要根据BISS-C的标准来设计,包括必要的信号线和地线。信号电平转换通常需要考虑不同芯片间的电平兼容问题,例如FPGA和BISS-C编码器之间的电平标准可能不一致,这需要通过电平转换器或收发器来解决。

在接口保护方面,通常会使用ESD(静电放电)保护器件,以防止静电对敏感的FPGA芯片造成损害。而电源管理则涉及到FPGA和BISS-C编码器的电压和电流要求,以确保整个系统的稳定运行。

### 2.3.2 接口电路仿真与调试

完成电路设计后,接下来是使用EDA(电子设计自动化)工具对电路进行仿真。仿真过程可以帮助设计者验证电路是否按照预定功能工作,特别是在处理高速信号和复杂协议时。仿真可以模拟信号在接口上的行为,检测可能的信号反射、串扰和时序问题。

仿真通过后,进行实际电路板的布局和布线(Layout and Routing),将电路设计转换为物理形态。在制造出实际硬件板后,还需要进行调试。调试包括验证硬件电路的物理连接、检查电源和地线的正确性、以及测试BISS-C通信协议的实现是否符合预期。

调试过程中,可能需要使用到示波器、逻辑分析仪等测试设备来观察信号波形,检查数据传输是否准确。如果发现问题,需要根据测试结果对设计进行迭代优化,直到硬件接口稳定可靠地工作。

# 3. ```

# 第三章:高速BISS-C编码器接口的FPGA设计

在高速数据采集和处理系统中,BISS-C编码器接口以其高速、高精度和高抗干扰性而广泛应用于各种场景,如机器人控制系统、精密测量设备等。由于FPGA具有并行处理能力和灵活的编程

```

0

0