FPGA实现的BISS-C编码器接口安全特性:全面分析与优化

发布时间: 2024-12-15 03:41:40 阅读量: 6 订阅数: 9

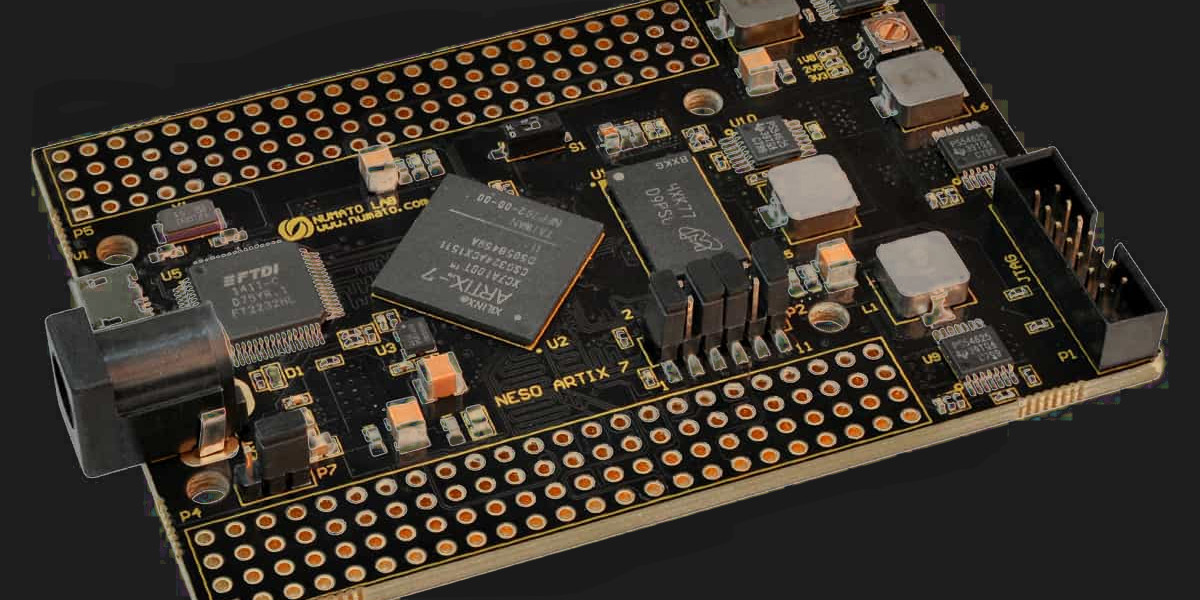

基于FPGA编写的BISS-C接口协议发送模块

参考资源链接:[FPGA实现的BISS-C协议编码器接口技术详解及解码仿真](https://wenku.csdn.net/doc/6471c28dd12cbe7ec301c4a4?spm=1055.2635.3001.10343)

# 1. BISS-C编码器接口概述

## 1.1 BISS-C编码器接口简介

BISS-C编码器是一种用于工业控制和数据采集系统的接口标准。它确保了信号在传输过程中的准确性和可靠性,是实现精确测量的关键工具。BISS-C通过编码技术,将传感器信号转换成数字形式,再通过标准的电气接口发送至数据处理系统。

## 1.2 接口的应用范围

这种编码器接口广泛应用于各种自动化设备和机器人系统中,如定位控制、速度测量和角度测量等。其精准的编码技术使得数据处理系统能够准确地读取传感器的输出信号,从而执行更精确的控制和反馈。

## 1.3 接口的技术优势

BISS-C编码器接口的特点包括其高速数据传输、低干扰和高抗噪性能,这些优势使其在复杂工业环境中具有很高的稳定性和可靠性。通过采用差分信号传输,BISS-C进一步提升了信号的抗干扰能力,确保了数据的完整性。

通过本章,我们将深入了解BISS-C编码器接口的基本概念,以及其在工业领域中的重要应用和优势。接下来,我们将深入探讨其工作原理以及在FPGA中实现其安全特性的方法。

# 2. BISS-C编码器接口的理论基础

### 2.1 BISS-C编码器的工作原理

BISS-C编码器是一种利用二进制编码来传输模拟数据的编码方式,广泛应用于位置和角度的测量。它将模拟信号转换为数字信号,便于长距离传输和数字信号处理,广泛应用于工业自动化、机器人技术、汽车、航天航空等领域。

#### 2.1.1 数据采集和编码过程

数据采集是BISS-C编码器操作的第一步,涉及将模拟信号转换为数字数据。这通常通过模数转换器(ADC)完成。编码器将这些数据转换为二进制编码,之后通过差分信号线传输到接收端。

```mermaid

graph LR

A[模拟信号] -->|ADC| B[数字数据]

B --> C[编码器]

C -->|二进制编码| D[差分信号线传输]

```

在编码过程中,BISS-C协议通常会加入同步信息和校验位以确保数据的完整性。这些同步信息和校验位能够帮助接收器准确地锁定信号并检测数据传输中的错误。

#### 2.1.2 BISS-C协议的特点和优势

BISS-C编码器接口因其简单、可靠和高效而受到青睐。协议支持实时、高精度的数据传输,并且具有抗干扰性强,通信距离远的优势。

### 2.2 安全特性的重要性

在现代工业应用中,数据的完整性和保密性至关重要。因此,BISS-C编码器接口的安全性显得尤为重要。

#### 2.2.1 接口安全的挑战和需求

接口安全的挑战包括数据篡改、信号干扰以及未授权的数据访问等问题。为了应对这些挑战,BISS-C编码器接口必须集成加密、认证等安全特性。

#### 2.2.2 安全标准和法规要求

为了确保数据传输的安全性,必须遵循一系列国际和行业的安全标准,如IEC 60870-5-101/104,它们规定了数据传输过程中的安全要求和规范。这些标准对数据加密、认证机制、数据完整性和访问控制等方面都有明确的要求。

综上所述,本章节重点介绍了BISS-C编码器的工作原理和重要性,深入探讨了其数据采集和编码过程,以及协议本身的特点和优势。同时,本章节强调了接口安全的必要性,并探讨了面临的挑战以及与之相关的标准和法规要求。通过本章节的介绍,读者能够对BISS-C编码器接口有一个全面而深入的了解,并认识到在设计和实现过程中必须考虑的安全特性。

# 3. FPGA实现BISS-C接口的安全特性

## 3.1 FPGA技术与接口设计

### 3.1.1 FPGA的基本概念和优势

现场可编程门阵列(FPGA)是一种通过编程来配置的半导体设备,它们允许在硬件层面上实现几乎无限的自定义功能。不同于传统的ASIC(专用集成电路)解决方案,FPGA在制造完成后仍可以通过编程来重新配置其内部逻辑,提供了极高的灵活性。FPGA是用硬件描述语言(HDL),如VHDL或Verilog,编写的逻辑电路可以通过EDA工具编译和烧录到FPGA芯片中。这使得设计者能够修改和更新设计,而无需更改物理硬件。

FPGA的出现给接口设计带来了革命性的变革,尤其是在需要高安全性、高速数据处理以及可编程特性的场合。FPGA相较于ASIC的优势在于其高度的灵活性和可编程性,这使得它们能够在不同应用之间迅速迁移,降低了产品开发和维护的成本。在BISS-C接口中,FPGA可以用于实现协议规定的加密和解密过程,以及身份验证和访问控制等安全特性。

### 3.1.2 FPGA在接口设计中的应用

FPGA在接口设计中扮演着至关重要的角色。在BISS-C编码器接口中,FPGA可以用来实现数据流的控制逻辑、数据加密、同步和通信协议的执行。由于BISS-C接口要求加密和解密过程具备高安全性和高速处理能力,FPGA可以利用其并行处理的优势,实现这些复杂的算法,从而保证数据在传输过程中的安全和实时性。

FPGA通常在高速串行接口、实时数据处理和高安全要求的通信接口中得到应用。通过利用FPGA的可编程逻辑单元,设计者可以创建复杂的时序和组合逻辑,优化信号的处理流程,从而实现高性能和低延迟的数据传输。在BISS-C接口的应用中,FPGA能够高效地处理信号,减少由于软件处理引起的延迟和性能瓶颈。

## 3.2 安全特性的硬件实现

### 3.2.1 加密算法的硬件实现

BISS-C接口的安全特性要求使用强大的加密算法来保护数据传输。FPGA由于其固有的并行处理能力,是实现加密算法硬件加速的理想选择。典型的加密算法如AES(高级加密标准)可以在FPGA上高度优化,并能实现比传统CPU更加高效的数据处理。

在FPGA上实现加密算法通常涉及以下几个步骤:

1. **算法选择与分析**:确定BISS-C接口所需的安全级别,并选择合适强度的加密算法。

2. **HDL编码**:使用硬件描述语言编写加密算法的逻辑。

3. **功能仿真**:对编写的HDL代码进行仿真测试,确保算法逻辑正确。

4. **综合与布局布线**:通过EDA工具将HDL代码综合成FPGA的逻辑元件,并进行布局布线。

5. **硬件测试**:在实际的FPGA硬件上测试加密算法,验证其实际性能与预期相符。

以下为AES加密算法在FPGA上的一段示例HDL代码,用于实现数据的加密过程:

```verilog

// AES加密模块示例代码

module aes_encrypt(

input clk, // 时钟信号

input reset, // 复位信号

input [127:0] plaintext, // 明文输入

input [127:0] key, // 加密密钥

output reg [127:0] ciphertext // 密文输出

);

// AES加密逻辑定义

always @(posedge clk or posedge reset) begin

if (reset) begin

// 复位时的处理逻辑

end else begin

// AES加密算法逻辑

end

end

// ... 其他加密细节实现 ...

endmodule

```

### 3.2.2 身份验证和访问控制机制

为了实现安全的身份验证和访问控制,FPGA可以设计为

0

0