Saleae 16 信号完整性分析:提高数据准确性

发布时间: 2024-12-27 05:49:46 阅读量: 9 订阅数: 12

saleae16 100M采样16通道逻辑分析仪.rar

# 摘要

本文首先概述了Saleae 16及其在信号完整性中的重要性,然后深入探讨信号完整性基础知识,包括信号完整性的定义、影响因素以及常见问题如反射、串扰和电磁干扰等。文章接着介绍Saleae 16软件界面、信号完整性测试与分析工具和问题解决策略。最后,本文详细阐述了Saleae 16在硬件调试中的应用,如硬件设计验证、嵌入式系统调试以及故障排除与性能优化,并展望了Saleae 16的高级应用与未来发展趋势。文章旨在提供对Saleae 16工具的全面理解,并强调其在提高信号完整性和硬件调试效率中的关键作用。

# 关键字

信号完整性;Saleae 16;硬件调试;反射;串扰;电磁干扰

参考资源链接:[Saleae16逻辑分析仪全方位使用教程](https://wenku.csdn.net/doc/2k40fv1uwd?spm=1055.2635.3001.10343)

# 1. Saleae 16概述及其信号完整性的重要性

Saleae Logic分析仪是工程师在进行硬件调试和信号分析时常选的工具之一。作为本系列文章的第一章,我们将介绍Saleae 16的基本概念以及信号完整性(Signal Integrity, SI)对于现代电子设计至关重要的原因。

## 1.1 Saleae 16的简介

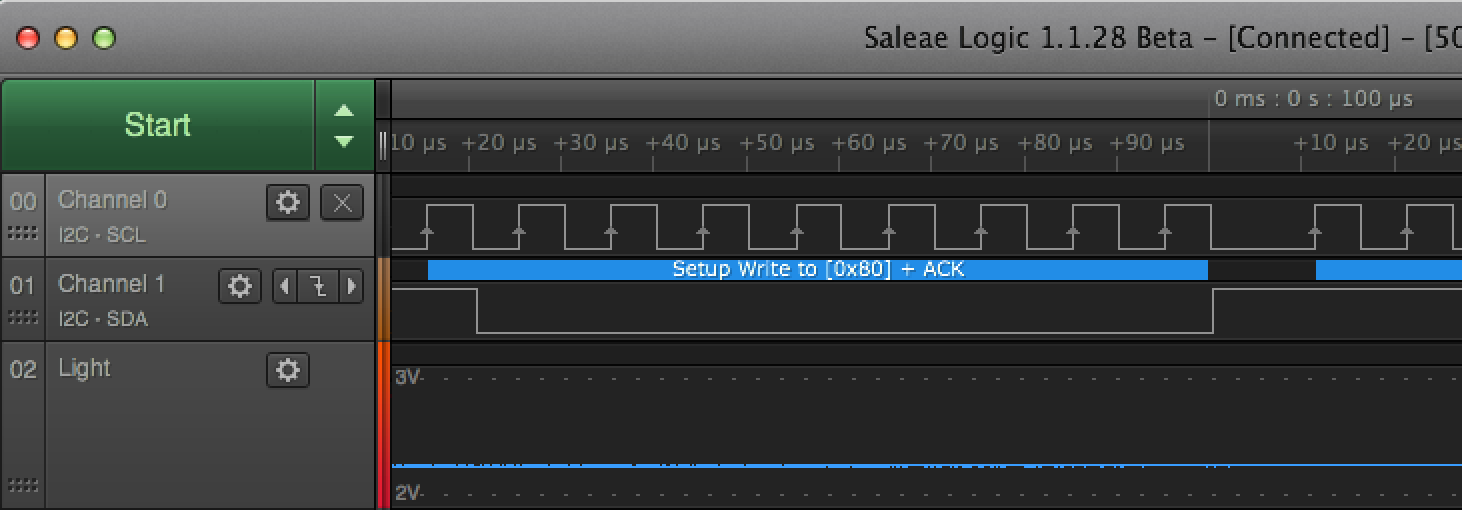

Saleae Logic系列逻辑分析仪是一款便携、易用、性价比高的硬件调试工具,支持多通道高速数字信号捕获和分析。Saleae 16是该系列中的一个型号,它能够同时监测16个数字信号,适用于多种场合,从简单的微控制器项目到复杂的数字通信系统。其易用性使得工程师能够快速地进行信号捕获和协议分析,大大简化了硬件调试流程。

## 1.2 信号完整性的重要性

在电子设计中,信号完整性指的是信号在传输路径中保持其幅度、形状和时序特性不变的能力。随着数字电路的时钟频率提高,信号上升时间变短,电路板上微弱的电气噪声都会对信号传输产生重大影响。这就要求电子工程师必须更加重视信号完整性,保证电路设计的可靠性和性能。

信号完整性对于高速数字电路设计尤为重要,不良的信号完整性可能导致数据传输错误,造成系统不稳定或完全故障。因此,分析并优化信号完整性是确保电路板设计成功的关键一环。在接下来的章节中,我们将深入探讨信号完整性基础知识、常见问题和提高信号完整性的设计策略。

# 2. 信号完整性基础知识

### 2.1 信号完整性的定义和影响因素

#### 2.1.1 信号完整性的基本概念

信号完整性(Signal Integrity, SI)是指信号在电路板上传输时,能够保持其理想的电压和时间特性,而不会受到各种电磁效应的干扰。良好的信号完整性意味着信号传输过程中失真最小,确保了数据的准确性和系统的稳定性。在数字电路设计中,信号完整性问题尤为突出,因为高速信号在传输路径上可能由于线路阻抗不匹配、串扰、反射和其他电磁干扰(EMI)而产生严重的信号质量下降。

#### 2.1.2 影响信号完整性的主要因素

影响信号完整性的因素众多,其中包括:

- **线路阻抗:** 信号传输路径上的阻抗不匹配会导致信号反射,影响信号质量。

- **传输线长度:** 高速信号的传输线如果过长,可能会因为传播延迟和信号衰减而降低信号完整性。

- **串扰:** 当邻近的信号线之间的电磁场相互作用时,会相互干扰,导致信号失真。

- **电磁干扰(EMI):** 外部和内部的电磁干扰源可以影响信号的质量。

- **电源和地线设计:** 不恰当的电源和地线设计可能会引起电源噪声和地弹。

- **终端匹配:** 如果信号的末端没有正确匹配,会造成信号反射,从而影响完整性。

### 2.2 信号完整性中的常见问题

#### 2.2.1 反射、串扰和电磁干扰

**反射:** 当信号在传输线中遇到阻抗不匹配点时,部分信号能量会反射回信号源,造成信号波形失真。反射的严重程度取决于阻抗不连续性的大小和信号上升时间。为了减少反射,设计时需要确保信号传输线和负载之间有良好的阻抗匹配。

**串扰:** 信号线之间相互靠得太近时,由于电磁感应,一个信号线上的电压变化会在邻近的线路上感应出电压,这被称为串扰。串扰可以是容性耦合(电容性串扰)或感性耦合(电感性串扰)。减小串扰的方法包括增加线间距、使用地平面隔离、减小走线长度和优化信号线的布线方向。

**电磁干扰(EMI):** 设计时不仅要考虑电路板上的信号,还要考虑到电路板与外界环境的电磁兼容性。EMI会导致系统性能下降,并可能引起设备之间的相互干扰。为了减少EMI,设计人员应该采取措施如使用屏蔽、优化布线、合理布局和选择合适的元件。

#### 2.2.2 电源和地线问题

电源和地线设计对确保信号完整性至关重要。电源平面和地平面不连续会引入噪声和电磁干扰,影响信号的稳定传输。在多层印制电路板(PCB)设计中,通常会有一个或多个专用层作为电源和地平面。设计时需要注意以下几点:

- **地平面设计:** 确保信号回路尽可能短,以减少电磁干扰和天线效应。

- **电源平面设计:** 高速电路中电源平面应尽可能靠近信号层,以减少电源噪声的影响。

- **去耦电容的使用:** 在关键芯片的电源引脚附近放置去耦电容,以减少电源线上的噪声。

#### 2.2.3 时序分析与噪声

**时序分析:** 在数字电路中,确保信号到达接收端的时机是正确的非常关键。时序分析用于评估电路的时序关系是否满足设计要求。时序问题可能导致逻辑错误或性能瓶颈。确保时序的关键在于:

- **精确计算信号传播时间:** 考虑所有的延时,包括传输线延迟、门延迟等。

- **遵守建立时间和保持时间:** 对于触发器和寄存器,确保数据稳定到达的时序满足建立时间和保持时间的要求。

**噪声:** 噪声是电子系统中不可避免的现象,它会导致信号失真,影响电路的性能。减少噪声的策略包括:

- **降低电源噪声:** 使用适当的电源管理技术和滤波器。

- **减小信号路径的干扰:** 通过合理的布局布线,以及使用屏蔽和接地策略。

- **设计裕量:** 在设计时考虑一定的信号容限,以应对噪声带来的影响。

### 2.3 提高信号完整性的设计策略

#### 2.3.1 布线和层叠设计的最佳实践

在PCB设计中,遵循一系列最佳实践可以帮助提高信号的完整性:

- **保持走线一致性:** 信号线应尽量保持直且平滑,避免锐角和90度角。

- **使用多层板:** 多层板设计可以提供更好的信号完整性,因为它允许更好的布线以及电源和地平面的使用。

- **优化层叠结构:** 合理的层叠设计可以帮助控制阻抗,提供信号屏蔽,并减少信号间串扰。

- **避免高速信号跨越分割平面:** 高速信号线不应跨越电源或地线平面分割区域,以防止回流路径的不连续性。

#### 2.3.2 终

0

0