Saleae 16 在FPGA调试中的应用:快速定位问题

发布时间: 2024-12-27 06:14:26 阅读量: 11 订阅数: 11

Saleae16 Logic+Setup+1.1.18完美板上位机 haowei

# 摘要

本文全面介绍了Saleae Logic软件及其在FPGA调试中的应用。首先,本文概述了Saleae Logic的基本安装与操作,为读者提供了软件界面和硬件连接的指南。随后,深入探讨了Saleae 16在FPGA信号逻辑分析中的基础应用,包括信号的捕获、解码以及常见信号问题的诊断方法。文章继续阐述了Saleae 16的高级功能,如多通道同步分析、信号比较与校验,以及脚本自动化测试的实践。此外,本文还探讨了Saleae 16与集成开发环境的整合使用,以及在实际FPGA项目中的案例分析,分享了调试经验、技巧和性能优化方法。最后,本文展望了Saleae 16在未来FPGA技术发展中的适应性和潜在应用前景。

# 关键字

Saleae Logic;FPGA调试;逻辑分析;信号捕获;自动化测试;集成开发环境

参考资源链接:[Saleae16逻辑分析仪全方位使用教程](https://wenku.csdn.net/doc/2k40fv1uwd?spm=1055.2635.3001.10343)

# 1. Saleae Logic的介绍与安装

## 1.1 软件简介

Saleae Logic是一款功能强大的逻辑分析仪软件,它能够捕获、记录和分析数字信号,广泛应用于电子工程师和硬件开发者的调试工作中。Saleae Logic以其直观的用户界面、高级分析功能和与硬件设备的无缝连接,赢得了业界的好评。

## 1.2 安装步骤

要开始使用Saleae Logic,首先需要下载并安装软件,这通常涉及到以下步骤:

1. 访问Saleae官网下载最新版本的安装包。

2. 运行安装程序,并按照指示完成安装过程。

3. 安装完成后,打开Saleae Logic软件,并完成设备的首次连接和配置。

## 1.3 初次使用准备

初次使用Saleae Logic之前,需确保已经连接了Saleae的硬件设备。软件会自动检测硬件并引导用户完成初始配置,包括设置采样率、通道数和其他采集参数。完成这些步骤后,就可以开始探索软件提供的丰富功能了。

# 2. Saleae 16在FPGA调试中的基础应用

## 2.1 Saleae Logic软件操作基础

### 2.1.1 界面布局与功能介绍

Saleae Logic软件的界面布局直观而简洁,便于用户迅速地掌握其核心功能。在软件打开后,界面通常由以下几个主要部分组成:设备状态栏、通道控制面板、信号查看窗口、时间轴显示以及导出和设置选项。

**设备状态栏**位于窗口的顶部,显示当前所连接的设备信息及数据捕获状态。通过这里可以快速检查硬件连接是否正常以及设备工作状态。

**通道控制面板**则让用户能够对每个通道的属性进行详细设置,包括通道的开关、名称、采样速率、触发源等参数的配置。此面板也常用于配置信号的逻辑电平标准,比如TTL、CMOS等。

**信号查看窗口**是进行信号分析的核心区域,支持波形、十六进制、CSV等多种视图模式。在波形视图模式下,用户可以直观地看到信号的变化趋势和时间关系。

**时间轴显示**则提供了一个全局的时间线参考,用户可以在这里设置触发点,以及查看捕获数据的开始和结束时间。

**导出和设置选项**提供用户进行数据导出以及软件的自定义设置,包括测量单位、时间格式等。

在使用Saleae Logic软件进行FPGA调试时,界面布局和功能的熟悉是提高调试效率的第一步。

### 2.1.2 硬件连接与信号捕获

与FPGA硬件连接是Saleae Logic软件进行信号捕获的基础。在硬件连接前,确保Saleae Logic设备已正确安装驱动程序,并且设备端口已经连接到计算机。

具体连接步骤如下:

1. 将Saleae Logic设备通过USB接口连接至电脑。

2. 打开Saleae Logic软件,软件将自动检测设备并显示设备状态。

3. 准备FPGA开发板,并根据需要使用的通道数选择正确的连接线。

4. 将连接线分别连接到Saleae Logic设备和FPGA开发板的对应测试点或引脚。

5. 在Saleae Logic软件中配置通道参数,包括通道名称、逻辑电平标准、采样速率等。

6. 点击开始捕获按钮,根据需要设置触发条件,并开始信号捕获。

信号捕获时,根据信号的特性和调试需求,可能需要调整采样速率和触发条件,以获得最佳的捕获效果。高采样速率能够捕捉到更细节的信号变化,但同时也会占用更多的存储空间。合理设置触发条件能够快速定位到感兴趣的信号区域,提高调试效率。

## 2.2 FPGA信号的逻辑分析

### 2.2.1 信号触发与捕获技巧

在使用Saleae Logic对FPGA信号进行捕获时,信号触发是关键的一步。通过正确的触发设置,可以有效地捕获到特定的信号事件,比如错误发生时的信号状态,或者是特定时间点的信号数据。

信号触发可以简单地分为边沿触发和模式匹配触发:

- **边沿触发**是最基本的触发方式,适用于捕获信号上升沿或下降沿的事件。在Saleae Logic中,用户可以选择“上升沿”、“下降沿”或者“任意边沿”作为触发条件。

- **模式匹配触发**适用于需要根据特定的信号模式来触发捕获的情况。在FPGA调试中,可能需要根据一组信号的特定组合来定位问题,模式匹配触发提供了这样的能力。

具体设置步骤如下:

1. 在Saleae Logic软件中,找到触发设置选项。

2. 根据需要选择边沿触发或模式匹配触发。

3. 对于边沿触发,选择触发信号通道并设定触发方向。

4. 对于模式匹配触发,输入期望的信号模式序列。

在捕获过程中,如果信号变化复杂或者没有明确的触发条件,可以通过设置时间延迟或者前导事件来辅助触发,或者调整触发的灵敏度和次数限制来优化捕获。

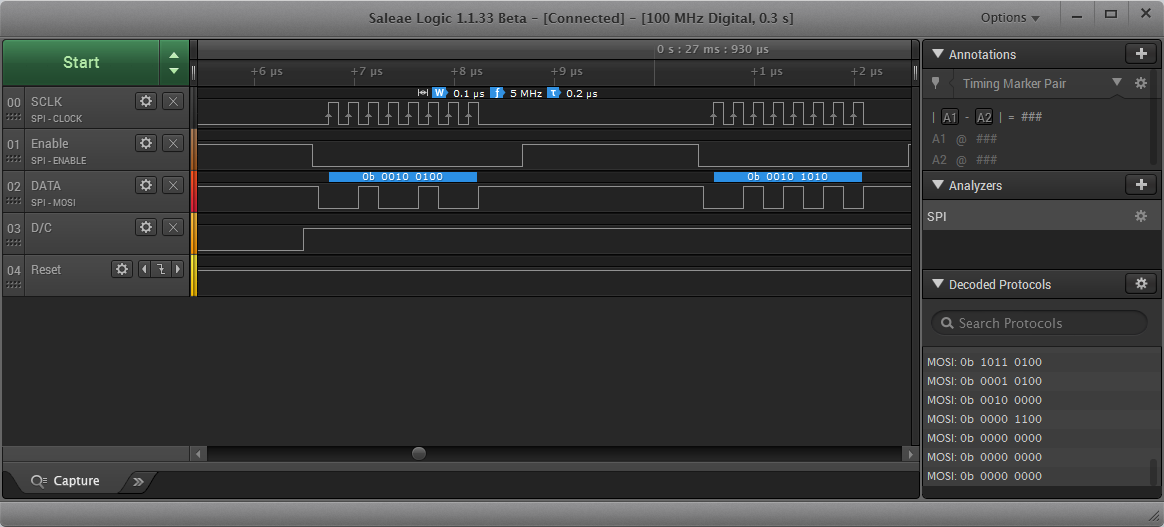

### 2.2.2 信号解码与协议分析

FPGA产生的信号往往是复杂的,并且可能遵循特定的通信协议。Saleae Logic软件内置了多种通信协议的解码功能,能够将信号波形转换为易于理解的协议层数据。

信号解码的步骤包括:

1. 选择解码协议:在信号查看窗口的工具栏上,点击“解码”选项,然后选择对应的协议进行解码。Saleae Logic支持常见的通信协议如SPI、I2C、UART、CAN等。

2. 配置协议参数:根据实际的信号情况,设置通信协议的参数,包括波特率、时钟极性、数据位宽等。

3. 查看解码结果:设置完成后,信号波形下方会显示解码后的数据,用户可以直观地查看到信号中的有效数据内容。

4. 分析协议数据:进一步分析协议数据,比如检查数据包的完整性、计算校验和等,以便于发现潜在的通信问题。

5. 使用协议分析功能:Saleae Logic还提供协议分析功能,允许用户对解码后的数据进行过滤、搜索和统计等操作,这对于复杂信号的调试尤为有用。

通过信号解码与协议分析,可以快速定位FPGA信号中的逻辑错误和通信问题,极大地提高了调试的效率和准确性。

## 2.3 常见信号问题的诊断方法

### 2.3.1 信号完整性检查

信号完整性(Signal Integrity, SI)是指信号在电路中保持原有特性传输的能力。在FPGA设计中,良好的信号完整性是确保系统稳定工作的关键因素之一。当信号完整性不佳时,可能会导致信号失真、反射、串扰和同步错误等问题,影响系统的可靠性和性能。

使用Saleae Logic进行信号完整性检查的基本步骤:

1. 捕获FPGA信号,确保信号的连续性和完整性。

2. 分析波形,查找是否存在如下问题:

- **过冲和下冲**:信号值超过规定的高电平或低电平的最大值。

- **反射**:信号在传输过程中遇到阻抗不匹配时产生的反射波形。

- **抖动**:时钟或数据信号的周期性变化超出了一定的范围。

- **同步错误**:比如时钟和数据信号之间不正确的对齐。

3. 对于可能存在的问题,需要进一步细化测试,比如使用示波器的探头来测试不同的点,或者更换具有更好电气性能的连接线。

### 2.3.2 时序问题的排查与分析

时序问题通常是指信号之间的到达时间不符合设计要求,导致数据无法在正确的时钟边沿被准确采样。在FPGA中,时序问题可能导致功能错误或性能下降,需要通过时序分析工具仔细排查。

使用Saleae Logic进行时序问题排查的步骤:

1. 捕获FPGA的时钟信号以及相关的数据信号。

2. 在信号查看窗口中查看时钟与数据信号的对应关系,检查是否有延迟、偏移或者相位不一致等问题。

3. 使用软件的测量工具,测量两个信号之间的时序关系,比如测量数据沿到时钟沿之间的延迟时间。

4. 分析测量结果,判断是否存在时序裕量不足的情况。时序裕量是指信号之间正确的时序关系应满足的设计规范。

5. 如果发现时序问题,需要回到FPGA设计中进行调整,可能涉及重新布局布线、调整时钟树或者改变信号逻辑。

通过Saleae Logic软件的直观波形显示和精确的测量工具,可以有效地进行时序问题的排查与分析,帮助FPGA设计人员发现并解决问题。

# 第三章:Saleae 16的高级功能实践

## 3.1 多通道同步分析

### 3.1.1 同步通道的设置和应用

Saleae Logic软件的多通道同步分析功能,允许用户同时捕获来自不同信号源的信号,并将这些信号同步显示在同一个时间线上,这对于分析信号间的时序关系至关重要。

设置多通道同步分析的步骤如下:

1. 在Saleae Logic软件中,确认所有需要同步的通道都已经正确连接并配置。

2. 打开一个新会话,并在会话设置中选择需要同步的通道。

3. 确保所有通道使用相同的采样速率,并选择适当的通道时钟源。可以手动设置一个通道作为同步的参考源,或者让软件自动检测最佳的同步源。

4. 开始捕获信号,所有同步通道的数据将同时显示。

5. 通过软件提供的时序测量工具,可以测量并分析不同信号间的时间关系,比如信号之间的相对延迟。

多通道同步分析在FPGA调试中非常有用,尤其是

0

0