设计高效I2C接口最佳实践:硬件与软件的融合之道

发布时间: 2024-12-18 11:22:45 阅读量: 6 订阅数: 10

STM32单片机FPGA毕设电路原理论文报告基于avr单片机的煤矿传感器设计

# 摘要

I2C接口作为一种广泛使用的串行通信总线,在多种系统中扮演着核心角色。本文首先概述了I2C接口的重要性及其基本概念。随后,详细探讨了I2C硬件设计的关键要素,如信号特性、硬件接口电路设计和设备地址规划。文章第三章着重于I2C软件协议栈的组成与实现,并提出了性能优化技巧。第四章讨论了I2C接口的故障诊断与调试方法。在第五章中,通过应用案例深入分析了I2C在嵌入式系统、消费电子及工业自动化中的集成和使用。最后一章展望了I2C技术的未来发展,挑战与机遇,并强调了持续学习的重要性。本文旨在为I2C技术的从业者提供全面的参考,并助力于I2C技术的进步与创新。

# 关键字

I2C接口;硬件设计;软件协议;故障诊断;通信协议;技术展望

参考资源链接:[DesignWare DW_APB_I2C 数据手册](https://wenku.csdn.net/doc/7gsutt6tii?spm=1055.2635.3001.10343)

# 1. I2C接口概述及其重要性

I2C(Inter-Integrated Circuit)总线接口,是电子通信领域内一种广泛使用的串行通信协议。其设计目的在于提供一种低成本的串行通信方法,允许微控制器(MCU)和各种外围设备进行连接。I2C接口支持多主多从模式,使得它能够被用于实现模块间的简单通信。对于嵌入式系统开发者来说,I2C技术的应用至关重要,因为它不仅减少了所需的I/O端口数量,也简化了系统硬件设计。此外,由于其低速特性,I2C非常适合用于传感器和低速外围设备的数据交换,是物联网和消费电子产品中不可或缺的通信方式之一。接下来,我们将探讨I2C的设计关键要素,帮助读者深入理解这一重要接口的设计和应用。

# 2. I2C硬件设计的关键要素

### 2.1 I2C总线标准与信号特性

#### 信号电平和时钟速率

I2C(Inter-Integrated Circuit)总线是一种多主机、串行计算机总线,用于连接低速外围设备到处理器或微控制器,以及在处理器或微控制器之间进行通信。I2C总线信号电平定义了逻辑“1”和“0”的电压范围。标准模式下,逻辑“0”定义为低于0.3×VDD(供电电压)的电压,逻辑“1”为高于0.7×VDD的电压。这些电平标准允许不同逻辑电平的设备之间进行通信。

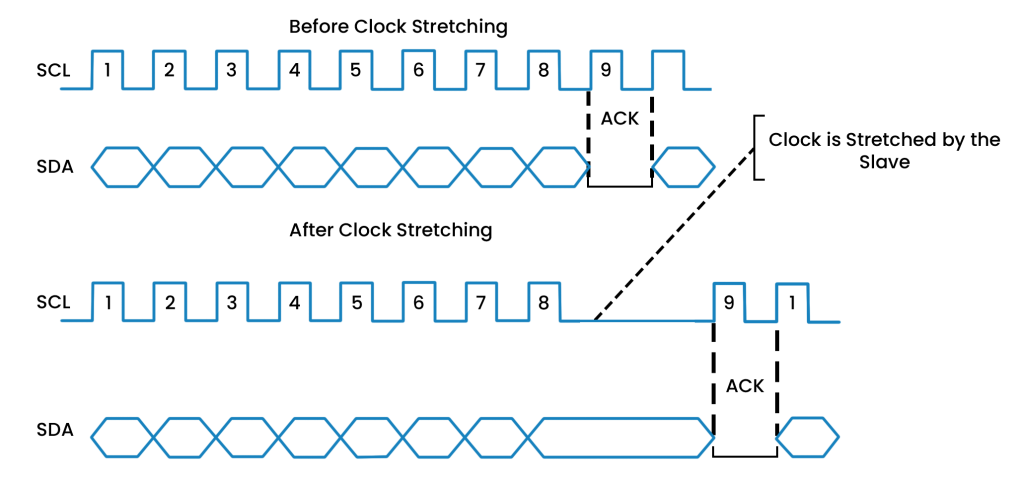

时钟速率对于I2C总线而言是一个关键参数,它决定了数据传输的速率。标准模式下的速率可以达到100kbps,而快速模式(Fast-mode)则提升到400kbps,快速模式+(Fast-mode Plus)可以达到1Mbps,而更高速率的I2C变种也在开发中。高速模式(High-speed mode)能支持高达3.4Mbps的速率。为了保证兼容性,高时钟速率下还必须考虑到时钟拉伸、信号建立和保持时间等参数。

### 2.2 I2C硬件接口的电路设计

#### 拉高电阻的选择和计算

在I2C总线设计中,线路上使用上拉电阻(Pull-up resistor)将I2C总线线拉高到逻辑高电平。选择合适的电阻值对于系统的稳定性和通信速率至关重要。电阻值过低会导致较高的静态电流消耗,而电阻值过高则可能造成信号完整性问题,如无法达到最小的高电平要求。

例如,对于标准模式的I2C,总线电容一般不超过400pF,根据I2C标准,可以通过以下公式计算上拉电阻值:

\[ R = \frac{{V_{DD} - V_{OL}}}{{I_{OL}}}\]

其中,\( V_{DD} \) 是供电电压,\( V_{OL} \) 是输出低电平电压,\( I_{OL} \) 是输出低电平时的电流。如果供电电压为5V,\( V_{OL} \) 最大为0.4V,\( I_{OL} \) 通常为3mA,则最小上拉电阻值为100欧姆。

#### 滤波器和保护电路的集成

为了确保信号质量和抗干扰能力,I2C总线通常需要集成滤波器和保护电路。滤波器可以帮助滤除信号线上的高频噪声,常见的滤波方法包括在I2C线路中串接一个小电容(一般为4.7nF),或者使用RC低通滤波器。保护电路则包括限流电阻、ESD(静电放电)保护二极管等,以防止电压尖峰损坏I2C设备。

### 2.3 I2C设备地址规划与分配

#### 静态与动态地址分配方法

I2C设备的地址分配是总线初始化和通信的一个重要方面。每个I2C设备都有一个7位的地址,因此理论上可以有128个不同的地址。在静态地址分配方法中,设备地址在硬件设计阶段就已固定,这种方法适用于设备数量固定的系统。

动态地址分配通过软件在系统运行时分配地址,适用于需要动态添加或删除设备的场合。动态分配通常需要一个地址分配协议,通过协商确定各个设备的地址。硬件上,一些设备支持地址重映射或引脚配置来实现地址的动态变化。

#### 设备地址冲突的解决策略

当两个设备拥有相同的地址时,就发生了地址冲突,这将导致数据传输错误。为了解决这一问题,I2C总线协议提供了一些策略,如在设备上实现地址掩码位,允许某些地址位被硬件或软件控制来唯一标识设备。另外,设计者可以使用“地址解码逻辑”方法,通过逻辑电路设计让设备在识别到主设备发出的地址后决定是否响应。此外,还有一些协议扩展,如 SMBus Alert Response Address,用于在地址冲突时提供独特的响应机制。

# 3. I2C软件协议的实现与优化

## 3.1 I2C软件协议栈的基本组成

### 3.1.1 主机与从机的通信协议

I2C通信协议支持多主机和多从机的配置。主从机之间通过地址识别,从而进行数据传输。主机负责发起通信,生成时钟信号(SCL),并控制数据传输方向。在I2C通信中,所有从机都使用相同的时钟信号和数据线(SDA),因此主机需要提供一个起始条件(S),在起始条件之后,主机发送一个地址帧,这个帧包含了7位地址和1位读/写方向位。从机会监听这个地址,如果与自己的地址匹配,那么就会响应主机,开始数据传输。

通信过程中,数据都是以8位为单位进行传输的,数据位后面紧跟着一个应答位。主机在传输完一个字节数据后,会释放数据线(SDA),然后提供一个时钟脉冲(SCL),等待从机发送应答信号。如果从机正确接收到数据,它会在时钟脉冲期间将SDA拉低,表示应答(ACK)。如果没有应答(NACK),SDA将会保持高电平。

### 3.1.2 错误检测与恢复机制

错误检测是I2C通信中非常关键的一步,确保数据传输的准确性和可靠性。I2C协议提供了多种错误检测机制,包括仲裁丢失(Arbitration Lost)检测和时钟同步错误检测。在多主机环境中,如果两个主机同时发送了起始条件和地址信息,那么最终在SDA线上呈现的电平将由输出低电平能力最强的主机决定。如果一个主机检测到线上的电平与自己发送的不一致,它就会检测到仲裁丢失。此外,如果时钟信号被错误地拉长,比如由于某些设备的响应速度慢,会导致时钟同步错误,这种情况下协议也会进行错误恢复。

错误恢复机制通常包括停止条件(P),该条件由主机在检测到错误后发出,用以结束当前的通信,从而重置总线状态。在软件协议栈中,错误检测和恢复通常是通过状态机来实现的,状态机能够根据I2C事件的状态进行相应的处理,保证数据传输的完整性和一致性。

## 3.2 I2C通信的软件实现

### 3.2.1 驱动程序的加载与配置

I2C驱动程序在Linux内核中通常是以设备驱动程序的形式存在。驱动程序的加载与配置对I2C通信的实现至关重要。驱动程序加载到内核后,需要配置设备树(Device Tree)或ACPI表,以描述I2C控制器和连接的设备信息。例如,在Linux内核中,设备树需要包含I2C控制器的物理地址、中断号、时钟速率等信息。对于连接到控制器的每个设备,也需要有一个节点描述其I2C地址、所属控制器等。

加载驱动程序通常涉及以下步骤:

1. 编译内核或模块。

2. 在启动时加载模块(或重启以使用新的内核配置)。

3. 检查是否成功加载,通常是通过查看`dmesg`输出或`/sys/class/i2c-adapter/i2c-<n>/device/`目录下的设备节点。

### 3.2.2 读写操作的数据封装与解析

在I2C通信中,数据的封装和解析是通过数据帧的形式进行的。当主机要向从机发送数据时,它首先将起始条件和从机地址帧发送到总线上。然后发送数据帧,每个数据帧由8位数据组成,并且在数据帧之

0

0