I2C时钟拉伸与总线竞争解决方案:避免与解决之道

发布时间: 2024-12-18 12:03:55 阅读量: 3 订阅数: 8

i2c的时钟延展问题

# 摘要

I2C通信协议在嵌入式系统中广泛使用,但时钟拉伸现象和总线竞争是影响其稳定性的两大挑战。本文首先介绍了I2C通信协议的基础知识,然后深入解析了时钟拉伸的理论,探讨了其对总线通信的负面影响,以及总线竞争的产生和后果。通过硬件和软件两个层面的预防策略,如选择合适的上拉电阻和驱动优化,本文旨在提供有效的解决方案,以避免时钟拉伸与总线竞争的发生。此外,本文还提供了解决方案的实践案例,包括问题诊断和解决方案的实施,以确保I2C通信的稳定性和可靠性。

# 关键字

I2C通信协议;时钟拉伸;总线竞争;硬件预防;软件处理;实践案例

参考资源链接:[DesignWare DW_APB_I2C 数据手册](https://wenku.csdn.net/doc/7gsutt6tii?spm=1055.2635.3001.10343)

# 1. I2C通信协议基础

I2C(Inter-Integrated Circuit)通信协议是一种由菲利普半导体公司在1980年代推出的高度流行的串行通信协议。它主要用于微控制器和各种外围设备之间的低速通信。I2C的设计理念是节省微控制器的I/O端口,因此该协议仅使用两根线:一根用于时钟信号(SCL),另一根用于数据信号(SDA)。这两根线都通过上拉电阻连接到正电源,从而确保空闲状态下两线均为高电平。

尽管I2C协议简单,但它支持多主机模式,允许多个主机同时控制总线。协议在设计时考虑到了主机之间的冲突解决机制,确保通信的有序进行。在数据传输时,数据信号(SDA)在时钟信号(SCL)的上升沿和下降沿之间保持稳定,以保证数据的准确读取。

I2C协议的灵活性和效率使其在多种电子设计中得到广泛应用,从简单的传感器到复杂的存储设备都可能使用I2C进行数据交换。接下来的章节将深入探讨I2C的高级主题,比如时钟拉伸和总线竞争,以及如何优化和解决这些问题。

# 2. I2C时钟拉伸现象的理论解析

## 2.1 I2C时钟信号特性

### 2.1.1 时钟信号的角色和要求

在I2C(Inter-Integrated Circuit)总线协议中,时钟信号(SCL)扮演着至关重要的角色。SCL线负责同步数据传输,确保所有参与通信的设备在相同的时间点上对数据位进行采样。为了保证数据传输的可靠性,I2C协议对SCL线有特定的要求。

首先,SCL线必须提供一个稳定的时钟频率,这个频率定义了数据传输的最大速率。I2C协议支持从低速(10kHz)到高速(400kHz)乃至快速模式(1MHz)以上的数据传输速率。其次,时钟信号必须有良好的上升和下降时间,以避免产生干扰和误读。此外,为了确保系统的稳定性和同步,所有设备都必须在SCL线的控制下进行通信。

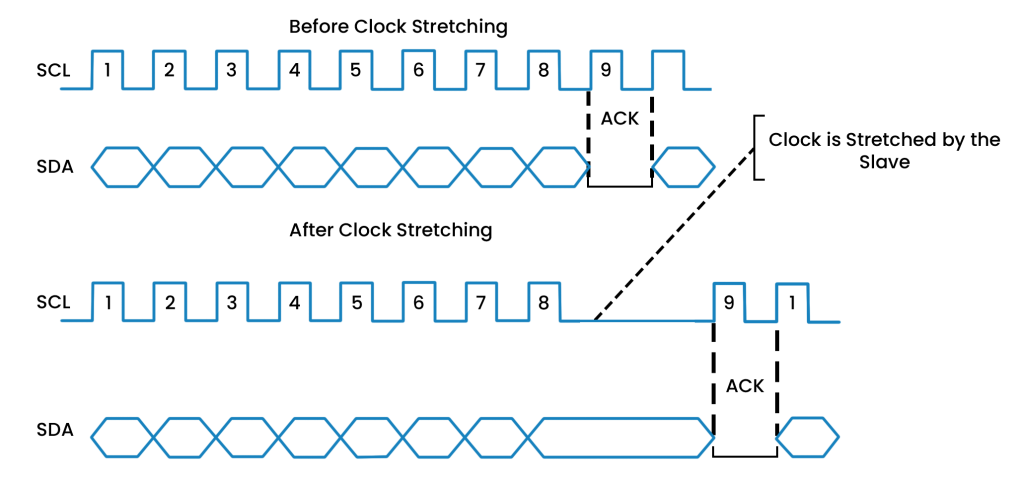

### 2.1.2 时钟拉伸的定义和成因

时钟拉伸(Clock Stretching)是I2C通信协议中一个特有的现象,它发生在从设备需要更多时间来处理接收到的数据时。在这种情况下,从设备通过延长SCL线的低电平时间,强制主设备等待,直到从设备准备就绪。这是一种硬件层面的流量控制机制,允许从设备在不丢失数据的情况下调节总线的传输速率。

时钟拉伸的成因通常是由于从设备的内部处理速度较慢,或者是在处理一个较为复杂的操作时,需要额外的时间来确保数据处理的准确性。例如,一个从设备可能需要执行一个内存写入操作,而这个操作的时间可能比数据传输时间要长,此时使用时钟拉伸可以防止数据丢失或损坏。

## 2.2 时钟拉伸对总线通信的影响

### 2.2.1 时钟拉伸的直接后果

时钟拉伸的直接后果是导致数据传输的延迟。由于从设备通过拉低SCL线来“冻结”总线,主设备必须等待直到SCL线回到高电平状态才能继续传输数据。这种延迟对于数据传输速率和总线吞吐量有直接的影响,特别是当频繁发生时钟拉伸时,总线的效率会显著降低。

另一个后果是时钟拉伸可能导致总线上的其他设备进入不确定状态。如果主设备或其他从设备没有正确处理时钟拉伸,可能会引起通信错误或总线仲裁失败。因此,所有I2C设备的设计都必须考虑时钟拉伸的可能性,并在硬件和软件层面实现相应的处理机制。

### 2.2.2 通信故障的可能场景

在某些情况下,时钟拉伸可能导致通信故障。最常见的情况之一是当从设备未能在规定的时间内释放SCL线,造成总线阻塞。这可能是因为从设备硬件故障、软件死锁或错误地实现时钟拉伸逻辑。

此外,如果主设备没有正确处理从设备的时钟拉伸,可能会导致数据位的错误采样,进而引起数据损坏。在极端情况下,时钟拉伸还可能引发系统级的故障,例如引起主设备的看门狗定时器超时,从而导致系统重置。

为了避免这些故障场景,设计人员需要在硬件和软件中实现对时钟拉伸的正确处理。在硬件层面,需要确保有恰当的上拉电阻设

0

0