AXI协议深度解析:【事务处理与流量控制的优化艺术】

发布时间: 2024-12-29 00:15:09 阅读量: 12 订阅数: 12

AXI总线协议(中文)+AXI总线协议(英文)

# 摘要

本文全面介绍了AXI协议的基础知识、架构概览以及事务处理机制,深入探讨了不同AXI事务类型和通道信号交互的特点。通过分析AXI流量控制与优化策略,本文提出了一系列技术以提高数据传输效率和系统性能。同时,本文也对AXI协议在高性能计算、FPGA开发和SoC设计中的实际应用案例进行了详尽分析,并探讨了未来发展趋势和面临的挑战。文章旨在为设计工程师提供在各种应用场景下实现高效、稳定AXI通信的参考和指导。

# 关键字

AXI协议;事务处理;通道信号;流量控制;性能优化;FPGA开发;SoC设计;协议演进

参考资源链接:[Zynq SoC与AXI Quad SPI接口设计指南](https://wenku.csdn.net/doc/6401ac6bcce7214c316ebc9c?spm=1055.2635.3001.10343)

# 1. AXI协议基础与架构概览

## 1.1 AXI协议简介

AXI(Advanced eXtensible Interface)是ARM公司推出的一种高带宽、高性能的片上总线协议,广泛应用于复杂集成电路的设计中。它为处理器和IP核之间的高速数据传输提供了一种标准化的接口。

## 1.2 AXI架构的组成

AXI架构主要由Master(主设备)、Slave(从设备)、以及连接它们的通道和信号线组成。它支持多条独立的通道并行工作,可以大大提升数据传输的效率。

## 1.3 AXI的设计目标

AXI协议的设计目标是提供一种灵活且高性能的接口,使设计者能够构建高速且复杂的系统级芯片(SoC)。它支持非阻塞传输,允许多个事务同时进行,从而提高带宽利用率。

通过本章节内容,我们将对AXI协议有一个基础的认识,并且了解到其架构概览,为后续深入解析AXI协议的事务处理机制、流量控制与优化策略、以及实际设计中的应用案例打下基础。接下来的章节将详细探讨AXI协议的核心机制和实际应用。

# 2. AXI事务处理机制详解

### 2.1 AXI事务类型及特点

#### 2.1.1 读事务与写事务的区别

在AXI协议中,读事务和写事务是两种最基础的数据传输方式。读事务是从从设备获取数据,写事务是向从设备写入数据。在操作上,它们的主要区别在于数据流向的不同以及完成事务所需信号的差异。

- 读事务中,主设备向从设备发出读请求,从设备在准备好数据后将其发送回主设备。期间,主设备使用`ARVALID`信号发起地址读请求,并且在`ARREADY`信号有效时,从设备响应并确认接受请求。一旦数据准备就绪,从设备将数据放到数据通道,并通过`RVALID`信号通知主设备数据有效,主设备通过`RREADY`信号确认数据接收。

- 写事务则相反,主设备将数据写入从设备。主设备通过`AWVALID`信号发起地址写请求,并在从设备用`AWREADY`确认请求后,将数据通过`WVALID`和`WDATA`信号发送。从设备在准备好接收数据后,使用`WREADY`信号进行确认,最后主设备通过`BVALID`信号告知从设备写操作完成,从设备响应`BREADY`信号确认完成。

在整个过程中,读事务通常包含三个通道的交互(地址、读数据、控制),而写事务则包含五个通道的交互(地址、写数据、控制),增加了写响应通道。

#### 2.1.2 独立事务和组合事务的实现

独立事务是AXI中的基础事务类型,每项事务都独立于其他事务进行。例如,一个写事务完成之后才允许下一个写事务开始,这意味着事务之间没有重叠或并发。

组合事务是指通过一系列的信号和协议机制,允许多个独立的事务同时进行,提高了系统的效率。例如,可以通过“突发”传输多个数据项,而不需要在每次数据传输之间都有独立的事务请求。组合事务能够提升带宽利用率和减少延迟。

在AXI协议中,可以使用`INCR`(递增)、`WRAP`(环绕)等突发类型信号来实现组合事务。主设备会发出一系列包含起始地址和突发长度的请求,从设备响应并返回/接收相应序列的数据。在组合事务中,`BVALID`和`RVALID`信号可以同时有效,允许多个读写事务并行处理,这在一定程度上缓解了数据传输的瓶颈问题。

### 2.2 AXI通道与信号交互

#### 2.2.1 地址通道、数据通道和控制通道的功能

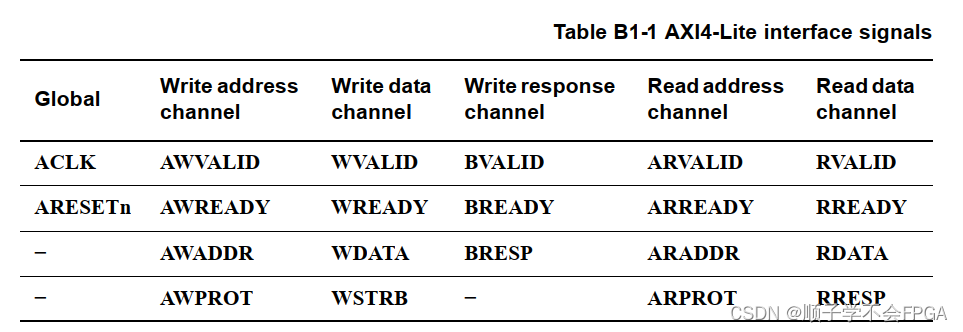

AXI协议定义了五个独立的通道,每个通道都有特定的功能和信号:

- **地址通道**:包含用于指定传输目标的地址和传输类型(读或写)的信号。例如`ARADDR`(地址读请求信号)、`ARPROT`(保护类型)、`ARVALID`(地址读请求有效信号)以及相应的响应信号`ARREADY`。写事务也有类似的地址通道信号`AWADDR`、`AWPROT`、`AWVALID`及`AWREADY`。

- **数据通道**:承载实际的数据,对于读事务来说,从设备将数据放在`RDATA`信号上,并通过`RVALID`及`RREADY`信号控制数据流;对于写事务,主设备将数据放在`WDATA`信号上,并通过`WVALID`及`WREADY`信号控制数据发送。

- **控制通道**:负责传输事务相关的控制信号,例如`RRESP`和`BRESP`用于读和写事务的响应状态,`RLAST`和`BLAST`信号用于标识突发传输的结束。

#### 2.2.2 关键信号的时序和协议约束

AXI协议的信号交互遵循严格的时序约束,以保证数据传输的一致性和正确性。以下是几个关键信号的时序和协议约束:

- **有效信号与就绪信号的匹配**:主设备发出有效信号(如`AWVALID`)必须与从设备的就绪信号(如`AWREADY`)匹配,这表示主设备准备发送地址信息,而从设备准备接收。数据传输只能在有效信号和就绪信号都为高时发生。

- **响应信号与事务状态**:事务发起后,必须收到从设备的响应信号(如`RRESP`和`BRESP`)以确认事务的完成状态。主设备和从设备需要根据事务类型和状态码来处理事务的成功或错误。

- **突发传输的时序**:在突发传输模式下,主设备可以在不等待每个数据项单独响应的情况下发送连续的数据项。`AWLEN`或`ARLEN`信号定义了突发传输中的数据项数量,`AWSIZE`或`ARSIZE`定义了每个数据项的大小。传输结束时,主设备使用`WLAST`(写事务)或`RLAST`(读事务)信号来标识。

### 2.3 AXI事务处理的性能影响因素

#### 2.3.1 竞争与仲裁机制

在多个主设备共享同一从设备的系统中,可能会发生对从设备访问的竞争。为了避免冲突,并确保系统稳定运行,AXI协议定义了仲裁机制。

- **仲裁逻辑**:系统中的仲裁器负责控制主设备对从设备的访问。它根据一定的优先级规则和算法决定哪个主设备可以进行事务处理。仲裁器必须确保事务的顺序性和公平性,以防止低优先级的事务被饿死。

- **仲裁策略**:常见的仲裁策略包括固

0

0