ZYNQ SOC图像处理:利用FPGA加速图像算法的革命性方法

发布时间: 2024-12-27 22:55:24 阅读量: 6 订阅数: 7

基于springboot的酒店管理系统源码(java毕业设计完整源码+LW).zip

# 摘要

本文综述了基于ZYNQ SOC和FPGA技术的图像处理系统的设计与实现。首先介绍了ZYNQ SOC的技术概念和FPGA在图像处理领域的优势,包括其并行处理能力和可重配置性。随后详细探讨了ZYNQ SOC开发环境的搭建过程,以及图像处理算法的分类和原理。接着通过实践案例深入分析了基于FPGA的图像处理编程模型和优化技术,性能评估,以及具体的项目案例分析。文章强调了在进行实时视频流处理和智能交通监控系统开发时遇到的硬件资源限制、软件与硬件协同开发的问题及解决方案,为相关领域的研究和开发工作提供了参考。

# 关键字

ZYNQ SOC;FPGA;图像处理;并行处理;实时处理;硬件加速

参考资源链接:[ZYNQ SOC全面教程:1200页修炼秘籍](https://wenku.csdn.net/doc/5fhyx59uj8?spm=1055.2635.3001.10343)

# 1. ZYNQ SOC和FPGA技术概述

## 系统级芯片(SoC)的概念

系统级芯片(System on Chip, SoC)是一种集成电路(IC),它集成了一个完整系统的所有电子电路,包括处理器、存储器、输入/输出端口等。SoC设计旨在在单个芯片上提供更低功耗、更小尺寸和更高性能的优势。

## FPGA技术简介

现场可编程门阵列(Field Programmable Gate Array, FPGA)是一种可以通过编程来配置的集成电路。与传统ASIC相比,FPGA提供了更高的灵活性和快速原型设计的能力,允许设计者在硬件层面上优化算法的性能。

## ZYNQ SOC的独特之处

ZYNQ SOC是Xilinx公司推出的一种集成了处理器系统(PS)和可编程逻辑(PL)的SoC平台,为开发者提供了处理与逻辑定制的综合解决方案。这种架构特别适合于需要高效并行处理能力和动态可重配置能力的应用场景,如图像处理、机器视觉等。

# 2. 图像处理算法的理论基础

## 2.1 图像处理算法分类与原理

### 2.1.1 空间域处理技术

空间域处理技术直接在图像的像素上进行操作,利用像素邻域信息来执行算法。它不涉及图像的频率域变换,适用于如滤波和锐化这类的图像增强操作。常见的空间域算法包括:

- 滤波算法:用于去除图像中的噪声或模糊图像,如均值滤波、中值滤波等。

- 锐化算法:用于增强图像中物体的边缘,突出细节。

- 二值化算法:用于将灰度图像转换为黑白二值图像,常用于图像分割。

空间域处理在实现过程中主要关注邻域操作的效率和边界条件的处理。例如,在实现卷积滤波时,需要考虑边界像素的填充问题,防止数据越界。

### 2.1.2 频域处理技术

频域处理技术涉及到图像的频率成分,首先需要将图像从空间域转换到频域,然后在频域中进行处理,最后再转换回空间域。这种处理方式对于图像压缩和特征提取非常有效。一些关键的频域处理算法包括:

- 傅里叶变换:是频域处理的基础,可将图像从空间域转换到频域。

- 高通和低通滤波器:常用于图像的边缘提取和模糊化。

- 带通和带阻滤波器:用于特定频率成分的提取和抑制。

频域处理的计算复杂度较高,特别是在处理大尺寸图像时。但利用快速傅里叶变换(FFT)算法可以显著提高变换的效率。

## 2.2 FPGA在图像处理中的优势

### 2.2.1 并行处理与硬件加速

FPGA的优势在于其并行处理能力,它允许用户根据算法需求定制硬件逻辑。图像处理中的许多操作,如卷积、滤波等,都可以通过数据流的方式实现高度并行,提高处理速度。

为了进一步加速处理,可以利用FPGA中的DSP(数字信号处理)单元来执行乘法和累加操作,这是许多图像处理算法中的核心操作。并行处理和硬件加速使得FPGA在处理实时图像流时具有显著优势。

### 2.2.2 灵活的可重配置性

FPGA的一个关键特性是可重配置性,即能够在硬件层面根据需求更改算法实现。这一点对于图像处理尤为重要,因为图像算法会随着应用的不同而变化。

通过修改配置文件,可以快速调整FPGA硬件逻辑以适应新的算法或优化现有的处理流程。这种灵活性使得FPGA在快速迭代开发和原型设计中特别有用。

## 2.3 图像算法FPGA实现的挑战

### 2.3.1 实时处理需求

实时性是图像处理系统的重要要求,特别是在安全监控和医疗成像等领域。FPGA通过并行处理能力能够提供高速图像处理,但仍需面对资源调度、数据传输和处理延时等挑战。

为了满足实时性要求,FPGA开发人员需要在设计时考虑算法的高效映射、内存访问优化和减少流水线延迟等因素。

### 2.3.2 资源和功耗的平衡

虽然FPGA提供了灵活性和高性能,但其资源消耗和功耗也比传统处理器要高。因此,在实现图像算法时,需要在性能和资源消耗之间找到平衡点。

在硬件设计阶段,通常需要仔细规划算法的硬件实现以节省资源,并通过动态电源管理策略来降低功耗。这涉及到算法优化、资源复用、优化的流水线设计等技术。

在下面的章节中,我们将深入探讨这些挑战以及如何在FPGA上实现高效的图像处理算法。

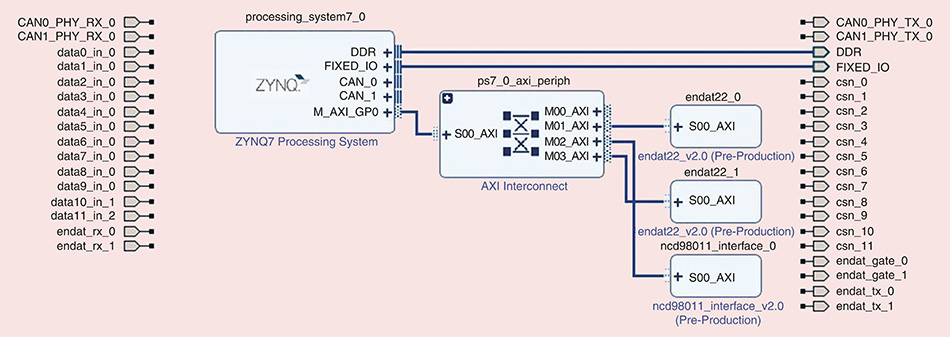

# 3. ZYNQ SOC开发环境的搭建

## 3.1 ZYNQ SOC的硬件架构和特性

ZYNQ SOC,也被称作Zynq-7000,是Xilinx公司推出的一款系统级芯片(SoC),它将处理器系统(PS)和可编程逻辑(PL)巧妙地结合在了一起,为开发者提供了一种全新的设计范式。ZYNQ SOC为多种应用提供灵活性和性能,特别适合于需要高集成度和高性能的图像处理应用。

### 3.1.1 双核心处理系统

ZYNQ的PS部分集成了一个双核心ARM Cortex-A9处理器,这是基于ARM架构的高性能处理器。这种处理器能够运行操作系统,如Linux,并处理复杂的应用逻辑。同时,它为图像处理应用提供了丰富的外围接口,如USB、以太网和PCIe等。

核心特性和优势:

- 双核处理器实现多任务并行处理。

- 高性能的处理器单元,能够运行现代操作系统。

- 支持多层存储系统设计,包括SDRAM、NAND闪存等。

- 可以作为整体系统管理器,负责控制、配置和监控可编程逻辑资源。

### 3.1.2 可编程逻辑的集成

ZYNQ的PL部分由大量的逻辑单元、存储资源以及DSP(数字信号处理)单元构成,可以实现高度定制化的硬件加速器。在图像处理应用中,这允许开发者实现高度并行化的数据处理,从而提高整个系统的吞吐量。

核心特性和优势:

- 可以实现定制的硬件加速器,满足特定算法的需求。

- 丰富的FPGA资源,包括BRAM(块RAM)和DSP单元。

- 逻辑单元可以被编程实现各种算法的并行处理。

- 低延迟和高吞吐量的数据处理能力。

## 3.2 Xilinx开发工具链介绍

Xilinx提供了完整的开发工具链,使开发者能够利用ZYNQ SOC实现复杂的设计。主要的工具有Vivado设计套件和软件开发工具包(SDK),它们共同为开发流程提供支持。

### 3.2.1 Vivado设计套件概述

Vivado设计套件是一个集成的设计环境,它包括了从设计输入、综合、实现到生成比特流的完整流程。Vivado不仅支持传统的FPGA设计,还支持基于ZYNQ SOC的设计。

核心特性和优势:

- 高效的设计流程,缩短产品上市时间。

- 支持高层次综合(HLS),允许使用C/C++语言进行硬件设计。

- 提供了丰富的IP核,能够快速实现常用功能模块。

- 强大的仿真和分析工具,帮助开发者优化设计。

### 3.2.2 SDK和Vivado HLS的集成

Xilinx SDK为基于ARM处理器的应用软件开发提供了环境。Vivado HLS则是将高级语言(如C/C++)转换为FPGA上可执行硬件逻辑的工具。这种集成能够极大提高开发效率,允许软件开发者无需深入了解硬件细节,即可进行硬件加速应用的开发。

核心特性和优势:

- 软硬件协同设计,可以同时开发处理器软件和FPGA逻辑。

- 支持基于C/C++的高层次综合,缩短硬件开发周期。

- 提供丰富的调试工具和性能分析工具,优化软硬件设计。

- 简化了传统FPGA编程的复杂性,允许工

0

0