【蓝桥杯EDA高效解题技巧】:揭秘专家如何快速应对各类问题

发布时间: 2024-12-13 16:32:54 阅读量: 7 订阅数: 14

参考资源链接:[蓝桥杯EDA历届试题解析与资料合集](https://wenku.csdn.net/doc/37ffkjwgsu?spm=1055.2635.3001.10343)

# 1. 蓝桥杯EDA赛题概述

蓝桥杯全国软件和信息技术专业人才大赛中的EDA(电子设计自动化)赛题一直是众多IT从业者及高校学生的挑战与机遇。本章节旨在为读者提供一个关于蓝桥杯EDA赛题的全面概述,帮助理解赛题背后的基础知识、技能要求以及如何将理论知识应用于实际问题解决中。

## 1.1 赛题的目的与意义

蓝桥杯EDA赛题不仅是对参赛者EDA相关知识掌握程度的测试,更是一次对创新思维和实际操作能力的挑战。通过解决这些赛题,参与者能深入了解EDA工具的使用,提高电路设计与仿真技能,从而在实际的工程项目中更加得心应手。

## 1.2 赛题特点分析

赛题通常会涵盖数字逻辑设计、时序分析、电路仿真等多个方面,强调理论与实践相结合。参赛者需要熟练运用EDA工具,如Cadence、Altera或Xilinx等,来完成赛题要求,这对快速学习和应用新知识提出了较高要求。

## 1.3 参赛准备建议

对于准备参加蓝桥杯EDA赛项的朋友们,建议尽早开始准备,熟悉相关的EDA工具和编程语言,如VHDL或Verilog,同时应该多做历年的真题,以熟悉考试形式和难度。适当的培训和辅导也能起到很好的辅助作用。

通过本章的介绍,我们希望读者能对蓝桥杯EDA赛题有一个整体的认识,并在后续章节中深入了解EDA的各个方面,为赛题的成功解决打下坚实的基础。

# 2. EDA基础知识与理论

### 2.1 EDA的核心概念

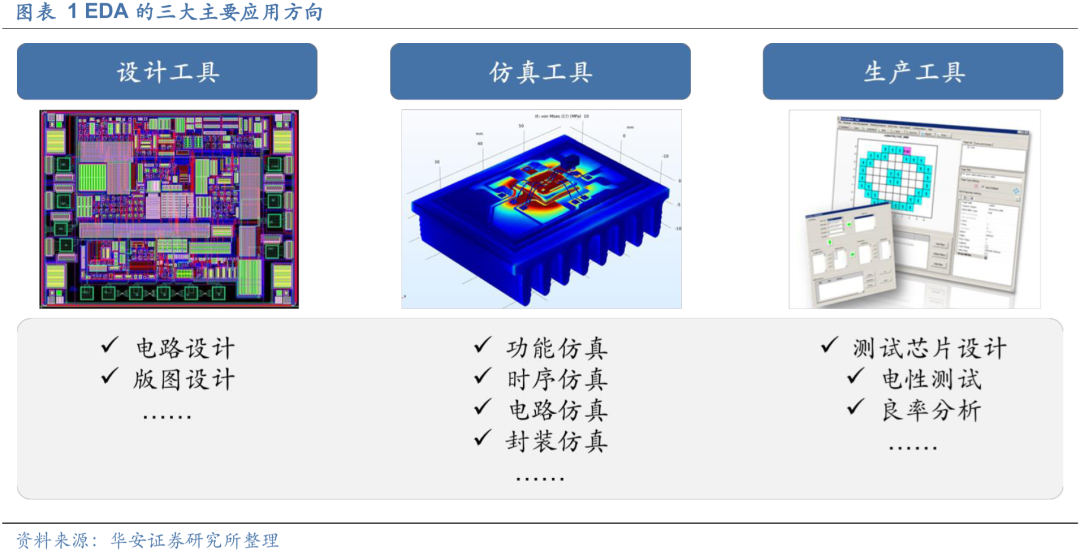

EDA(Electronic Design Automation)电子设计自动化是一种计算机辅助设计(CAD)技术,它广泛应用于电子系统设计中。EDA技术集合了计算机图形学、算法、数据管理以及界面设计等多项技术,旨在帮助工程师快速完成电子系统的设计工作。

#### 2.1.1 EDA的定义与重要性

EDA是实现电子系统设计自动化的核心技术,涵盖了从电路图设计、仿真、布线到物理验证等全过程。EDA工具让工程师能够以更高的效率、更低的成本完成复杂电子产品的设计,极大地缩短了产品从设计到上市的周期。

#### 2.1.2 EDA在蓝桥杯中的应用场景

在蓝桥杯等电子设计竞赛中,EDA工具是实现设计思路与创新的重要手段。参赛者通过EDA工具将电路设计、逻辑仿真以及PCB布局等环节高效融合,从而在有限的时间内展现其电子设计能力。

### 2.2 常用EDA工具解析

#### 2.2.1 工具功能和使用特点

EDA工具各有其独特的功能与特点。例如,Cadence提供了全面的设计解决方案,而Altium Designer则以其用户友好的界面和综合设计能力而闻名。这些工具能够提供从原理图捕获到PCB布局布线的完整流程。

#### 2.2.2 工具间的对比分析

对比不同EDA工具时,需要关注它们在功能、性能、易用性、成本以及生态支持等方面的表现。例如,一些工具可能更适合大规模集成电路设计,而另一些则可能更适合小型项目或学生使用。

### 2.3 数字逻辑设计基础

#### 2.3.1 逻辑门与逻辑表达式

数字逻辑设计的基石是逻辑门电路,包括AND、OR、NOT等基本逻辑门。逻辑门的组合形成更复杂的逻辑表达式,它们是构成数字电路的基础。

#### 2.3.2 组合逻辑与时序逻辑设计

组合逻辑电路的输出仅取决于当前输入,而时序逻辑电路的输出不仅与当前输入有关,还与电路的历史状态有关。理解这两种逻辑电路的设计方法对于掌握电子系统设计至关重要。

# 3. 蓝桥杯EDA解题实践

## 3.1 电路图绘制技巧

### 3.1.1 快速绘图方法

在EDA工具中,电路图的绘制是解题的基础,同时也是耗时最长的阶段之一。快速准确地绘制电路图对于提高解题效率至关重要。以下是几个提升绘图效率的技巧:

1. **熟悉快捷键与操作流程**:大多数EDA工具都有自己的快捷键和操作流程,学习并熟练这些操作可以显著提高绘图速度。例如,在使用Cadence或Altium Designer时,通过快速布局(Rapid Layout)功能可以实现快速的连线。

2. **组件库的优化使用**:事先整理和优化组件库可以减少在绘图时的搜寻时间。应当将常用的元件按照类别和使用频率进行分类,以便快速调用。

3. **模板与模块化设计**:创建通用电路模块的模板,可以实现复用。例如,标准的时序电路单元或者通用的接口电路都可以预先设计好模板,在需要时直接调用。

### 3.1.2 常见问题及解决方案

在绘图过程中,开发者可能会遇到各种问题,以下是一些常见问题及其解决方法:

1. **元件定位不准**:在绘制复杂电路时,元件的精确定位是挑战之一。使用网格对齐功能和对齐工具可以确保元件位置准确。

2. **连线混乱**:电路图中连线混乱会影响图纸的可读性。可以使用信号追踪和自动布线功能,这些工具能自动优化连线路径,提高电路图的整洁度。

3. **元件库不足**:可能会遇到EDA工具提供的元件库不全的情况,这时可以通过导入外部库文件来解决。

```mermaid

graph TD

A[开始绘制电路图] --> B[优化快捷键使用]

B --> C[创建电路模块模板]

C --> D[绘图]

D --> E[定位元件]

E --> F[连线]

F --> G[优化连线路径]

G --> H[使用外部库文件补充元件]

H --> I[结束绘图]

```

## 3.2 仿真调试流程

### 3.2.1 仿真环境的搭建

仿真环境的搭建是验证电路设计正确性的重要步骤,其操作流程如下:

1. **选择合适的仿真器**:根据电路设计的类型选择合适的仿真器。例如,对于数字电路设计,可以使用ModelSim或者Vivado。

2. **配置仿真环境**:设置正确的仿真参数,包括仿真时间、波形文件输出格式、仿真算法选择等。

3. **加载设计和测试平台**:将电路设计和测试平台代码加载到仿真器中。

4. **编译与初始化**:编译设计文件,确保没有语法错误,并进行仿真前的初始化设置。

### 3.2.2 故障定位与分析技巧

当仿真结果与预期不符时,需要进行故障定位和分析。以下是故障分析的一些常用步骤:

1. **查看仿真波形**:分析输出波形,比较与预期波形的差异。

2. **逐步执行仿真**:逐步执行仿真,观察关键信号的变化,找出故障点。

3. **逻辑分析仪使用**:利用逻辑分析仪工具,对电路中的逻辑信号进行实时监测。

4. **检查设计文件**:回到设计文件,对比仿真波形,查找设计逻辑错误。

5. **利用仿真器的断言功能**:设置断言,当仿真器遇到特定条件时会停止,帮助定位问题。

```mermaid

graph LR

A[开始仿真调试] --> B[选择合适的仿真器]

B --> C[配置仿真环境]

C --> D[加载设计和测试平台]

D --> E[编译与初始化]

E --> F[查看仿真波形]

F --> G[逐步执行仿真]

G --> H[使用逻辑分析仪]

H --> I[检查设计文件]

I --> J[使用断言功能定位问题]

J --> K[结束仿真调试]

```

## 3.3 高效解题策略

### 3.3.1 赛题分类与解题模板

蓝桥杯EDA赛题往往覆盖了多个领域,包括数字逻辑、电路仿真、FPGA设计等。为了提高解题效率,可以将赛题进行分类,并为每类赛题准备相应的解题模板:

1. **数字逻辑题模板**:针对组合逻辑和时序逻辑设计准备不同的模板,包含通用的解题思路和方法。

2. **电路仿真题模板**:总结出通用的仿真流程和常见故障分析方法,形成模板。

3. **FPGA设计题模板**:FPGA题型可能包括状态机设计、数据路径设计等,对应这些题型建立模板。

### 3.3.2 时间管理与分数优化

在竞赛中,时间管理和分数优化同样重要。以下是一些管理时间和优化分数的策略:

1. **题目分析**:在开始解题前,仔细阅读题目要求,明确解题目标。

2. **分阶段完成**:将解题过程分为多个阶段,例如,先完成最容易的部分以获得分数,再逐步攻克难点。

3. **时间分配**:根据各部分的分数和难度合理分配时间,优先处理分值高的题目或自己最擅长的部分。

4. **持续练习**:通过大量练习,熟悉各类题型的解题技巧,快速识别题目的关键点。

```mermaid

graph LR

A[开始解题] --> B[赛题分类]

B --> C[准备解题模板]

C --> D[时间管理]

D --> E[优先处理高分值题目]

E --> F[分配时间给各个部分]

F --> G[持续练习以熟悉技巧]

G --> H[结束解题]

```

以上章节内容为第三章:蓝桥杯EDA解题实践的详细介绍,以帮助读者在准备和参加蓝桥杯EDA赛题时能够更加高效和系统地进行。

# 4. ```

# 第四章:蓝桥杯EDA高级技巧

在前三章中,我们已经熟悉了EDA的基础知识、理论和一些实用的解题实践,为进一步提高解题能力和电路设计水平,本章将深入探讨一些高级技巧,包括优化与重构电路设计、编程语言在EDA中的应用,以及算法在EDA中的实现。

## 4.1 优化与重构电路设计

优化和重构是EDA设计中非常重要的一部分,它不仅涉及电路性能的提升,还关系到资源的合理利用和设计的可维护性。

### 4.1.1 设计规则检查(DRC)

设计规则检查(DRC)是确保电路设计满足制造工艺要求的关键步骤。DRC会检查布局图是否符合一系列预定义的规则,比如线宽、间距、过孔密度等。不满足这些规则的设计可能会导致制造失败或性能不稳定。

```mermaid

graph LR

A[开始DRC检查] --> B[加载设计文件]

B --> C[选择检查规则集]

C --> D[运行DRC检查]

D --> E{是否发现错误?}

E -->|是| F[标记并修正错误]

E -->|否| G[通过DRC检查]

F --> H[重新运行检查]

H --> E

G --> I[完成DRC检查]

```

在实际操作中,使用EDA工具进行DRC时,需要选择合适的规则集,这通常由特定的工艺技术决定。检查结果可以详细到每个错误的具体位置,设计者根据这些信息进行逐一修正。

### 4.1.2 时序分析与优化

时序分析是评估电路中信号传输时间和系统性能的重要步骤。良好的时序性能是确保电路稳定运行的基础。

```mermaid

graph TD

A[开始时序分析] --> B[提取设计中的时序信息]

B --> C[建立时序约束]

C --> D[运行时序分析工具]

D --> E{是否满足时序要求?}

E -->|是| F[时序分析通过]

E -->|否| G[识别时序违规]

G --> H[优化设计以满足时序要求]

H --> D

```

进行时序优化时,首先需要确认时序违例的具体位置和原因,然后可以通过调整逻辑门的布局、使用更快的逻辑元件、增加缓冲器、减少路径长度等方法来解决时序问题。

## 4.2 编程语言在EDA中的应用

EDA工具不仅仅限于图形化的界面操作,编程语言在其中也有着重要的作用。

### 4.2.1 HDL语言基础

硬件描述语言(HDL)是描述和设计电子系统的一类编程语言,主要分为VHDL和Verilog两种。HDL语言在EDA中可以用来描述硬件设计,实现仿真和生成实际的硬件配置文件。

以Verilog为例,基本的模块定义如下:

```verilog

module my_module(

input wire clk,

input wire reset,

input wire [3:0] data_in,

output reg [7:0] data_out

);

// 模块内部逻辑定义

endmodule

```

在编写HDL代码时,需要理解模块化设计的重要性,确保代码的可重用性和可维护性。同时,对代码进行充分的仿真测试,验证逻辑正确性是至关重要的步骤。

### 4.2.2 高级语言接口与混合编程

现代EDA设计不仅支持HDL语言,还支持与C/C++等高级语言的接口,这种混合编程可以将复杂算法的实现交给更适合的编程语言处理,再通过接口与硬件设计协同工作。

```c

// C语言部分,用于实现复杂的算法逻辑

void complex_algorithm(int *input_data, int *output_data) {

// 算法实现细节

}

```

在混合编程模型中,需要处理好C语言和HDL之间的数据交互,确保数据能正确传递和处理。这通常通过定义特定的接口模块来实现。

## 4.3 算法在EDA中的实现

算法在EDA中的实现是将软件层面的逻辑转化为硬件电路,这个过程涉及算法的理解、优化、硬件映射等多个层面。

### 4.3.1 算法与硬件设计的结合

将算法转化为硬件电路设计,需要根据算法特点和硬件资源特性进行合理的映射。例如,图像处理算法可能需要大量的并行处理能力,而这种并行性在硬件实现上就比软件更容易实现。

算法实现到硬件通常分为以下几个步骤:

1. **算法分析:** 分析算法特性,包括计算复杂度、数据依赖关系等。

2. **数据路径设计:** 根据算法需求设计数据路径和处理单元。

3. **控制逻辑实现:** 设计与数据路径协同工作的控制逻辑。

4. **资源优化:** 对设计进行优化,减少资源消耗和提高运行效率。

### 4.3.2 实例分析:算法加速与优化

考虑一个图像处理中常见的卷积操作,传统的软件实现效率较低,如果将其映射到硬件实现,我们可以设计一个卷积加速器,通过并行处理单元来提升处理速度。

```mermaid

graph LR

A[开始卷积加速器设计] --> B[确定卷积操作的参数]

B --> C[设计并行处理单元]

C --> D[设计数据存储与传输机制]

D --> E[实现控制逻辑]

E --> F[硬件仿真测试]

F --> G{是否满足速度要求?}

G -->|是| H[完成卷积加速器设计]

G -->|否| I[优化设计]

I --> E

```

在设计卷积加速器时,可能涉及到数据的重用、流水线设计、存储器访问优化等高级技巧。这要求设计者不仅有扎实的EDA基础,还要对图像处理算法有深入的理解。

本章总结了EDA设计中的高级技巧,展示了如何进行优化与重构电路设计、如何应用编程语言以及如何在EDA中实现和优化算法。通过这些高级技巧的掌握,可以显著提升电路设计的效率和性能,同时也能在蓝桥杯等EDA竞赛中脱颖而出。

```

# 5. 蓝桥杯EDA案例分析

## 5.1 历年赛题回顾与解析

### 5.1.1 赛题趋势分析

在过去的几年里,蓝桥杯EDA赛题的发展趋势主要集中在复杂性、实用性和创新性上。随着集成电路的发展和EDA工具的进步,题目不仅在技术要求上越来越高,而且越来越接近实际工程问题。例如,赛题开始涉及FPGA的底层设计、SoC系统集成,甚至跨学科的问题,如与物联网、人工智能结合的项目。

为了更深入地理解这些趋势,我们可以按照年份将历年的赛题进行分类和分析。一般而言,赛题可以大致分为基础题目、中等难度题目以及高级题目。

- **基础题目**:通常涉及基础电路设计、逻辑门实现、简单状态机设计等。这类题目旨在考核参赛者对EDA工具的熟练程度和基础知识的掌握。

- **中等难度题目**:这部分题目可能包含更为复杂的组合逻辑和时序逻辑设计,要求参赛者对各种触发器、计数器等进行设计。近年来,这类题目开始要求参赛者利用特定的EDA工具特性来实现一些额外的功能,如资源优化、功耗降低等。

- **高级题目**:高级题目则更多地考察参赛者的综合设计能力,如集成多种功能的电路板设计、综合使用多种设计语言和工具进行设计、考虑实际工程中遇到的约束和条件。

### 5.1.2 解题思路与技巧总结

要解决蓝桥杯EDA赛题,参赛者需要熟练掌握电子设计自动化工具和设计方法。以下是一些解题思路和技巧的总结:

- **理解题目要求**:首先,对赛题的要求进行深入理解,明确题目的关键点和限制条件,这将指导你后续设计的方向。

- **基础知识的夯实**:基础知识点是解题的基石,包括数字逻辑基础、电路原理、EDA工具使用等,这些知识需通过不断练习来加强记忆和应用能力。

- **工具的熟练使用**:EDA工具的功能非常强大,学会使用工具进行快速设计和仿真,可以帮助你节约大量的时间。

- **设计的模块化和规范化**:良好的设计习惯可以提高效率并减少错误,模块化设计可以让你更容易地复用和测试各个部分。

- **仿真测试的重要性**:在设计的每个阶段进行仿真测试是非常重要的,它可以帮助你及早发现问题并进行修正。

- **代码的优化**:在使用硬件描述语言进行设计时,代码的清晰、简洁和优化是提高设计质量的关键。

通过以上步骤,参赛者可以逐步提高自己的解题能力,并在蓝桥杯EDA赛题中取得更好的成绩。

### 5.2 专家经验分享

#### 5.2.1 解题心得与学习方法

在蓝桥杯的竞赛中,专家们往往有着独到的见解和丰富的经验。以下是来自多位专家的解题心得和建议的学习方法:

- **积极学习新知识**:专家们强调,学习新知识和工具是提升解题能力的关键。不断更新自己的知识体系,才能在竞赛中保持优势。

- **理论联系实际**:将理论知识与实际案例相结合,通过项目实践加深对知识的理解。这不仅能够提升个人技能,也能在赛题中更好地运用所学知识。

- **交流与合作**:和他人交流想法、知识与经验,特别是与高年级同学或老师交流,可以开阔视野,提升解决问题的思路。

- **持续的实践练习**:专家们推荐定期进行实际的电路设计与仿真,通过不断的实践来巩固知识和提高解题速度。

#### 5.2.2 赛前准备与心理调适

在赛前,选手需要做好充分的准备,并保持良好的心理状态:

- **制定计划**:赛前应该制定详细的学习计划和训练计划,合理分配时间给知识点的学习、工具的使用练习、赛题的模拟练习等。

- **保持健康作息**:良好的作息习惯对于保持高效的学习和竞赛状态至关重要,避免赛前熬夜和疲劳过度。

- **心理准备**:竞赛不仅是对技术的考验,也是对心理素质的考验。需要学会调节情绪,保持冷静,对自己有信心。

通过以上这些经验分享,我们可以看出专家们在解题、学习和准备竞赛的过程中注重细节、平衡心态以及持续进步的重要性。

0

0