数字锁相环技术详解:ADS仿真中的数字处理与优化

发布时间: 2025-01-03 01:16:13 阅读量: 24 订阅数: 20

# 摘要

数字锁相环技术是无线通信和信号处理领域中的重要组成部分,它能够在高速数据传输中实现精确的时钟同步和频率跟踪。本文首先概述了数字锁相环的基本理论和技术,包括其组成部分、工作原理以及数学模型的建立。随后,探讨了数字处理技术如何提升锁相环性能,以及在ADS仿真环境下数字锁相环的设计与实现。最后,通过实践应用案例分析,揭示了数字锁相环在无线通信中的具体应用和设计挑战,为未来的技术发展和研究方向提供了见解。

# 关键字

数字锁相环;信号处理;数学模型;ADS仿真;时钟同步;性能优化

参考资源链接:[PLL锁相环ADS仿真教程](https://wenku.csdn.net/doc/5c1r6avx74?spm=1055.2635.3001.10343)

# 1. 数字锁相环技术概述

## 数字锁相环技术的兴起

数字锁相环(Digital Phase-Locked Loop, DPLL)技术是一种电子技术,用于使一个或多个输出信号与一个输入参考信号相位同步。该技术在无线通信、网络同步、高精度时钟生成等领域有广泛应用。

## 技术特点与应用价值

由于数字技术的引入,DPLL相较于传统的模拟锁相环(Analog PLL, APLL)具有更高的稳定性和灵活性。数字锁相环可以通过软件编程实现更加复杂的功能和算法,且容易集成于现代数字集成电路中。

## 发展背景

随着集成电路工艺的进步,数字处理技术的成本逐渐下降,使得数字锁相环技术得以在多个行业中应用。此外,数字锁相环在抗干扰、噪声抑制和频率合成方面的优势,使其成为行业关注的焦点。

## 结语

本章概述了数字锁相环技术的基本概念和发展背景,为理解后续章节的深入分析打下了基础。在接下来的章节中,我们将深入探讨锁相环的理论基础、数学模型、性能指标、设计实现以及应用案例。

# 2. 锁相环的基本理论与数学模型

## 2.1 锁相环的组成与工作原理

### 2.1.1 锁相环的基本组成部分

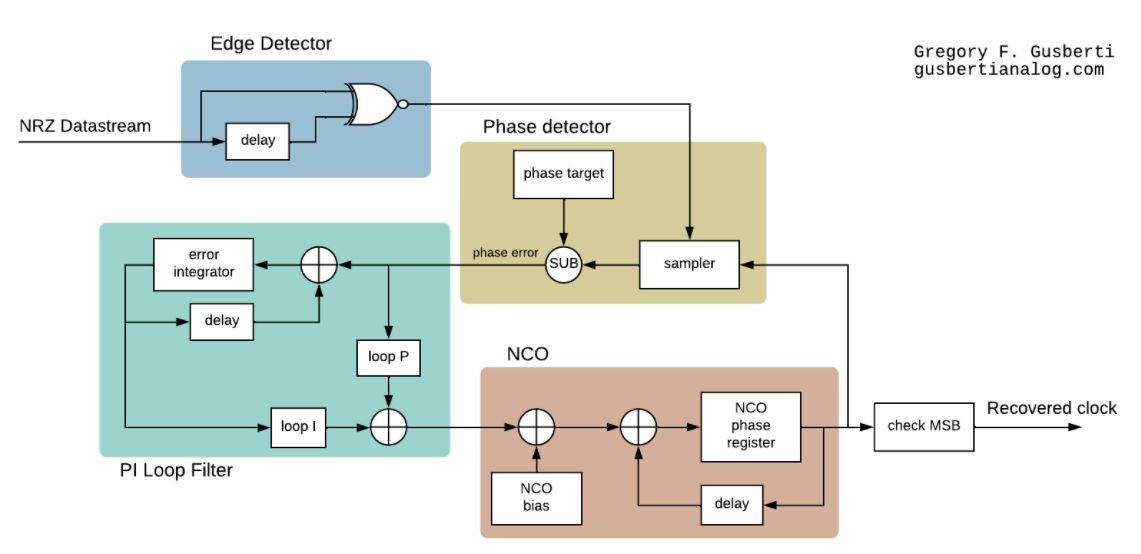

锁相环(Phase-Locked Loop,PLL)是一种利用反馈控制原理来实现信号相位同步的电路系统。它主要由相位检测器(Phase Detector)、环路滤波器(Loop Filter)、压控振荡器(Voltage-Controlled Oscillator,VCO)三个基本部分组成。

- **相位检测器**:这是锁相环中的关键部件,它负责检测输入信号与VCO输出信号之间的相位差,并将这个相位差转换成误差电压。典型的是鉴频鉴相器,可以是数字或模拟实现。

- **环路滤波器**:它是一个低通滤波器,目的是为了滤除高频噪声,并将相位检测器的输出误差信号平滑,再送入VCO作为控制电压。这一步骤至关重要,因为它决定了锁相环的稳定性与响应速度。

- **压控振荡器**:VCO输出信号的频率是由输入的控制电压决定的。在PLL中,VCO的频率会根据环路滤波器的控制电压进行调整,直到其输出信号与输入信号同步(即相位差为零)。

这三部分相互作用,形成了一个闭合的环路。当输入信号与VCO输出信号相位差不为零时,环路会自动调节直到锁定状态,实现频率与相位的同步。

### 2.1.2 锁相环的工作过程解析

锁相环工作过程的解析,可分为以下几个阶段:

1. **捕获阶段**:当PLL启动时,若VCO的频率与输入信号的频率不一致,则必须调整VCO的频率以使频率逐渐接近输入频率。这通常是通过环路滤波器逐渐增大VCO的控制电压来实现的。

2. **跟踪阶段**:一旦VCO的频率接近输入信号的频率,相位检测器就会开始输出误差电压来调整VCO的相位。环路滤波器将平滑这个信号,避免过快的相位调整导致的环路不稳定性。

3. **锁定状态**:在理想状态下,PLL最终将进入锁定状态,在这个状态下,VCO的频率和输入信号完全同步,并且相位差保持在恒定值(通常为零)。

4. **维持锁定**:一旦锁定,即使存在环境干扰或输入信号的变化,PLL也能通过调整VCO的频率和相位来维持锁定状态。

了解这些工作原理后,可以进一步深入分析锁相环的数学模型,为设计和优化提供理论支持。

## 2.2 锁相环数学模型的建立

### 2.2.1 线性模型的构建

为了方便分析和设计,通常在一定条件下,将锁相环的非线性模型线性化。线性模型通常假设小信号操作,即相位差在锁定点附近变化不大。一个典型的线性模型如下:

- 线性化后的相位检测器可视为一个增益为\(K_d\)的模块。

- VCO的特性可以通过增益\(K_v\)表示,即控制电压变化所引起频率变化的比例。

- 环路滤波器可以看作一个传递函数\(F(s)\),其中\(s\)是拉普拉斯变换变量。

当锁相环处于稳定状态时,可以使用如下传递函数来描述PLL的动态特性:

\[ \frac{\theta_o(s)}{\theta_i(s)} = \frac{K_d K_v F(s)}{s + K_d K_v F(s)} \]

这里,\(\theta_o(s)\)和\(\theta_i(s)\)分别是VCO输出信号和输入信号的相位拉普拉斯变换。\(K_d K_v F(s)\)项称为环路增益,对PLL的稳定性与性能影响重大。

### 2.2.2 非线性因素的影响分析

尽管线性模型简化了分析过程,但实际的锁相环存在许多非线性因素。这些因素包括:

- **鉴频鉴相器的死区**:在小相位差时,鉴频鉴相器的输出可能不随输入变化。

- **VCO的饱和效应**:控制电压到达一定值后,VCO的输出频率不再增加。

- **环路滤波器的非线性**:实际滤波器元件可能表

0

0